具有集成的和屏蔽的电感器的半导体封装的制作方法

具有集成的和屏蔽的电感器的半导体封装

【技术领域】

1.本发明涉及半导体-电感器封装,特别涉及一种能屏蔽集成电感器的半导体芯片的封装。

背景技术:

2.半导体芯片应用广泛,通常都被封装在引线框架(lead-frame)塑料封装内。焊线(bonding wires)位于半导体芯片上的焊盘(bonding pads)和引线框架上的焊盘之间。然后用塑料封装引线框架和芯片,覆盖并保护焊线以及芯片和引线框架。引线框架的末端从塑料中突出来,形成引脚(pins)。从引脚、通过引线框架到引线框架的焊盘、通过焊线到芯片上的焊盘,形成了一条电路径。

3.虽然使用互补金属氧化物半导体(cmos)工艺等技术可以轻松地将晶体管、电阻器和电容器集成到半导体芯片中,但电感器却不行,无法集成,因为电感值太小或面积太大。

4.所以通常使用外部电感器。通常情况下,在金属芯周围多次缠绕金属线,而形成一个金属芯电感器。空芯电感器的电感比金属芯电感器的电感低,但更容易制造。一个空芯电感器可以由一个小的、扁平的螺旋线圈形成。这种平面电感器的能量损耗较低,对高频开关很有用,但对于某些应用(如电源转换器)来说,电感太低了。

5.这种平面空芯电感器在物理上可能能够与半导体芯片集成,也许集成在单个封装中。然而,电感线圈产生的电磁场可以在附近的金属导线中感应出电流。当电感器放置在半导体芯片附近时,电磁场会在半导体芯片的金属迹线中感应出不必要的电流。这些不必要的电流会干扰所需的信号,并导致半导体芯片不能正常运行。对于更高的电感和线圈电流,以及与芯片的紧密间距,芯片中的感应电流甚至可能损坏芯片。因此,由线圈产生的这种电磁干扰(emi)会妨碍与芯片集成在半导体封装中。

6.封装可以做得更大,以便半导体芯片和电感器间隔足够远,以使emi不会伤害到半导体芯片。然而,这个间距可能是电感器或芯片尺寸的几倍。封装不得不比期望的大许多倍。

7.多芯片模块或许可以有集成电感器,但这些模块比单芯片封装大很多倍。如此大的模块成本高昂,并且在安装它们的印刷电路板(pcb)上占用面积太大。某些应用,如物联网(internet-of-things,iot),在面积和成本上受到限制,无法使用大型封装。

8.希望有一种同时包含半导体芯片和电感器的半导体封装。希望能为半导体芯片屏蔽掉线圈产生的电磁干扰。还希望能提高线圈的电感。希望在半导体封装中增加一种结构,既能保护芯片免受emi影响,又可以提高电感器的电感。

【附图说明】

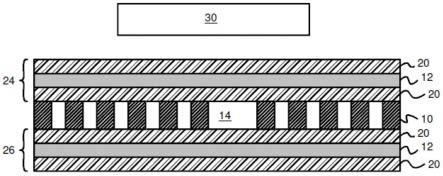

9.图1是一个屏蔽式电感器半导体封装的简化截面图。

10.图2a、2b、2c是图1的屏蔽式电感器半导体封装的截面的电磁场强度图。

11.图3是一个屏蔽式电感器半导体封装的三维图。

12.图4是去除了上铁氧体-电介质屏蔽层以显示出电感线圈的屏蔽式电感器半导体封装的三维图。

13.图5是图3的屏蔽式电感器半导体封装的俯视图。

14.图6是图3的屏蔽式电感器半导体封装的俯视图,其中去除了上铁氧体-电介质屏蔽层以显示出电感线圈。

15.图7是使用表面贴装焊球安装到pcb上的屏蔽式电感器半导体封装的截面图。

16.图8是另一种具有焊球的倒装芯片屏蔽式电感器半导体封装。

17.图9是另一种具有两个线圈的屏蔽式电感器半导体封装的截面图。

18.图10是另一种具有两个线圈的屏蔽式电感器半导体封装的截面图。

19.图11是一种双线圈屏蔽式电感器半导体封装的三维图。

20.图12是去除了上铁氧体-电介质屏蔽层以更好地显示出电感线圈的双线圈屏蔽式电感器半导体封装的三维图。

21.图13是另一种具有两个线圈的屏蔽式电感器半导体封装的截面图。

【具体实施方式】

22.本发明涉及一种半导体-电感器封装的改进。下面的描述是为了使本领域普通技术人员能够在特定应用及其要求的背景下制造和使用本发明。对于本领域的技术人员来说,对优选实施例的各种修改是显而易见的,本文定义的一般原则也可应用于其它实施例。因此,本发明并不打算局限于所示和所述的特定实施例,而是要给予符合本文所公开的原则和新颖特征的最广泛的范围。

23.图1是一个屏蔽式电感器半导体封装的简化截面图。半导体芯片30和电感线圈10一起集成在一个封装中(未示出)。电感线圈10在其中心有空芯14,并且是垂直于图1平面的螺旋状。虽然这个截面显示出的是断裂的电感线圈10,但是电感线圈10实际上是一个垂直于图1平面的连续线圈。

24.当电流通过电感线圈10时,会产生一个电磁场,这可能会在半导体芯片30中引起电磁干扰(emi)。然而,上铁氧体-电介质屏蔽层24被置于电感线圈10上方,在电感线圈10和半导体芯片30之间。上铁氧体-电介质屏蔽层24包含铁氧体层12,铁氧体层12在其顶部和底部被电介质层20夹在中间。

25.铁氧体层12是含有磁化铁或铁氧体金属颗粒的陶瓷层,如锰锌铁氧体(mnzn,分子式为mnazn

(1-a)

fe2o4)、或镍锌铁氧体(nizn,分子式为niazn

(1-a)

fe2o4)。电介质层20可以是塑料层压板或其他绝缘体,例如fr4或pi,它们是nema等级的玻璃增强环氧树脂层压材料。fr-4是一种复合材料,由编织玻璃纤维布和环氧树脂粘合剂组成,具有阻燃性(自熄灭)。pi是一种聚酰亚胺,它是属于高性能塑料类的酰亚胺单体的聚合物。经典的聚酰亚胺是kapton,它是由均苯四甲酸二酐(pyromellitic dianhydride)和4,4'-二胺基二苯醚(4,4'-oxydianiline)缩合而成。上铁氧体-电介质屏蔽层24可以制成片状的铁氧体层12,在其顶部和底部上覆盖有电介质层20,可以根据需要切割大小。

26.第二屏蔽是由下铁氧体-电介质屏蔽层26提供,以防止电磁场从电感线圈10的底部逸出并可能绕过上铁氧体-电介质屏蔽层24的边缘到达半导体芯片30。由于电感线圈10被上铁氧体-电介质屏蔽层24和下铁氧体-电介质屏蔽层26夹在中间,由电感线圈10产生的

电磁场被限制在上铁氧体-电介质屏蔽层24中的铁氧体层12和下铁氧体-电介质屏蔽层26中的铁氧体层12之间的一个小区域。

27.铁氧体层12对电磁场的这种限制也增加了电感线圈10的电感。即使电感线圈10是一个空芯电感器,因为电感线圈10的中心是空芯14,在电感线圈10平面上方和下方的铁氧体层12的存在也会增加其电感。

28.上铁氧体-电介质屏蔽层24可以接触电感线圈10的顶部,因为电介质层20可以防止电感线圈10和铁氧体层12之间的电短路。因此,铁氧体层12可以放置得非常靠近电感线圈10。电介质层20的厚度可以仅为0.1mm,因此可以非常严格地限制电磁场。电磁场的这种紧密间隔和限制可以进一步增强电感器线圈10的电感。虽然是空芯电感器,但被铁氧体-电介质屏蔽层24、26包围的电感线圈10可以具有可观的电感值,接近磁芯电感器的电感值。

29.图2a、2b、2c显示了图1的屏蔽式电感器半导体封装的截面上的电磁场强度图。当交流电通过电感线圈10时,会产生一个时变电磁场。当铁氧体层12不存在时,如图2a所示,该电磁场的强度如图2c中的曲线104所示。

30.图2b中铁氧体12的存在导致电磁场集中在铁氧体层12内,并在包围每个铁氧体层12的电介质层20内迅速下降。图2c中的曲线102显示电磁场强度的下降是如此之快,以至于在厚度各为0.1mm的电介质层20和铁氧体层12之外电磁场接近于零。在半导体芯片30附近,曲线102所示的具有铁氧体层12的电磁场远小于曲线104所示的不具有铁氧体层12的电磁场。

31.虽然铁氧体层12内的电磁场尖峰很大,如曲线102所示,但这些尖峰在电介质层20外部,如在半导体芯片30的表面附近,提供较低的电磁场强度。因此,由于铁氧体层12的存在,在半导体芯片30处的emi减少了。

32.在模拟中,半导体芯片30的表面(距离0.0)在偏离空芯14中心约10毫米(图2的z方向,即垂直于图2纸面的方向)和上铁氧体-电介质屏蔽层24顶部上方0.1毫米处,当铁氧体层12不存在时,此处电磁场强度为967μt,而当铁氧体层12存在时仅为0.523μt。

33.因此,铁氧体层12将半导体芯片30看到的电磁场降低了大约2,000倍。

34.图3是一个屏蔽式电感器半导体封装的三维图。例如通过环氧树脂或其他键合,半导体芯片30贴附到芯片贴装焊盘34(die attach pad)上。焊线42在半导体芯片30上的焊盘和引线框架焊盘40之间布线。一些焊线则从半导体芯片30上的焊盘走线到芯片贴装焊盘34上。

35.引线框架焊盘40、41位于引线框架立柱46、45的顶部,这些立柱连接到从封装底部突出的封装引脚,并且在被焊接到较大系统的pcb上时可以安置在pcb上的孔中。引线框架立柱46可以弯曲或连接到引线框架的其他部分(未示出),这些部分通向外部封装引脚、焊球或其他外部连接器(未示出)。

36.引线框架立柱45、46形成一个矩形,围绕着半导体芯片30、芯片贴装焊盘34和电感线圈10,电感线圈10大部分被上铁氧体-电介质屏蔽层24遮挡隐藏。电感线圈10顶部被上铁氧体-电介质屏蔽层24覆盖,底部被下铁氧体-电介质屏蔽层26覆盖。根据所需的电感值,电感线圈10的面积可以大于芯片贴装焊盘34和半导体芯片30的面积。

37.图4是一个屏蔽式电感器半导体封装的三维图,其中去除了上铁氧体-电介质屏蔽层以显示出电感线圈。在图4中,上铁氧体-电介质屏蔽层24已被移除。电感线圈10是一个平

面线圈,从其中心的中心柱36向外盘绕,中心柱36将芯片贴装焊盘34电连接到电感线圈10的中心绕组。电感线圈10的最外侧绕组通过线圈延长线48连接到引线框架外立柱45。

38.半导体芯片30上的大多数焊盘通过焊线42和引线框架焊盘40与引线框架立柱46末端的封装引脚形成电连接。然而,半导体芯片30的三个焊盘通过焊线连接到芯片贴装焊盘34的上表面。然后从芯片贴装焊盘34的上表面到芯片贴装焊盘34的下表面和中心柱36形成电连接。芯片贴装焊盘34可以是导电或金属迹线,芯片贴装焊盘34上的孔或通孔可以形成从半导体芯片30到中心柱36的电连接。因此,从半导体芯片30到电感线圈10的中心绕组形成了电连接。电感线圈10的外侧绕组通过线圈延长线48连接到引线框架外立柱45,该立柱在顶部有引线框架焊盘41,在底部连接到外部封装引脚。引线框架焊盘41不接收来自半导体芯片30的焊线42。

39.因此,电感线圈10在半导体芯片30的三个焊盘和外部封装引脚之间提供了一个串联电感。当变化的电流流过电感线圈10时,产生的电磁场被上铁氧体-电介质屏蔽层24(图3)屏蔽,以免在半导体芯片30中引起emi。

40.图5是图3的屏蔽式电感器半导体封装的俯视图。半导体芯片30连接到芯片贴装焊盘34的顶部,并通过焊线42电连接到引线框架焊盘40。在该俯视图中,引线框架立柱46被引线框架焊盘40遮挡隐藏。

41.电感线圈10的大部分被位于芯片贴装焊盘34和电感线圈10之间的上铁氧体-电介质屏蔽层24遮挡隐藏,并为半导体芯片30提供emi屏蔽。然而,电感线圈10的部分外侧绕组可见。电感线圈10的外部绕组的末端通过线圈延长线48连接到引线框架外立柱45(未示出),然后连接到引线框架焊盘41。电感线圈10的内侧绕组连接到芯片贴装焊盘34的下侧,然后通过焊线43连接到半导体芯片30。

42.图6是图3的屏蔽式电感器半导体封装的俯视图,其中去除了上铁氧体-电介质屏蔽层以显示出电感线圈。电感线圈10从其中心向外盘绕直到其最外侧绕组,该中心被半导体芯片30和芯片贴装焊盘34遮挡隐藏。电感线圈10的外侧绕组的末端通过线圈延长线48连接到引线框架外立柱45(未示出),然后连接到引线框架焊盘41。

43.图7是使用表面贴装焊球将屏蔽式电感器半导体封装安装到pcb上的截面图。电感线圈10夹在上铁氧体-电介质屏蔽层24和下铁氧体-电介质屏蔽层26之间,形成可弯曲的柔性层板。感应线圈10内的线圈可以相对于平面向上或向下移动,因为感应线圈10不是一片连续的金属片而是形成金属绕组的线圈。上铁氧体-电介质屏蔽层24和下铁氧体-电介质屏蔽层26分别包含被电介质层20夹住的铁氧体层12。电介质层20防止铁氧体层12与电感线圈10短路。图7显示了电感线圈10的最大弯曲或曲率。

44.芯片贴装焊盘34上的半导体芯片30通过焊线42连接到引线框架立柱46顶部的引线框架焊盘40。在本实施例中,引线框架立柱46的顶部可以用作引线框架焊盘40。半导体芯片30安装在芯片贴装焊盘34上,其位于上铁氧体-电介质屏蔽层24的顶部上方。铁氧体层12阻止由电感线圈10产生的磁通量到达半导体芯片30并导致emi。

45.引线框架立柱46的底部连接有焊球60,其可以是在加热时形成与pcb 62上的表面安装焊盘形成焊合的焊球。塑料封装剂(未示出)可以封装半导体芯片30并保护焊线42。

46.图8是另一种具有焊球的倒装芯片屏蔽式电感器半导体封装。半导体芯片30是一个表面安装芯片,它被翻转并通过焊球62连接到封装基板35的顶部。封装基板35上图案化

的金属迹线将芯片焊球62连接到更大的外部焊球60,该更大的外部焊球60将屏蔽式电感器半导体封装连接到系统pcb。

47.而且在该变体中,有两个电感线圈10、11,它们被电介质层21隔开。上铁氧体-电介质屏蔽层24屏蔽电感线圈10的顶部,而下铁氧体-电介质屏蔽层26屏蔽电感线圈11的底部。电感线圈10中心的空芯14与电感线圈11中心的空芯对齐。线圈立柱16连接上电感线圈10和下电感线圈11的外侧绕组。线圈立柱16可以向上延伸到封装基板35,然后到焊球60或半导体芯片30。可以添加焊线65以将半导体芯片30上的芯片焊球62之一连接到焊球60,焊球60连接到电感线圈10外端的线圈立柱16。

48.图9是具有两个线圈的屏蔽式电感器半导体封装的截面图。在该变体中,有两个电感线圈10、11,它们被电介质层21隔开。上铁氧体-电介质屏蔽层24屏蔽电感线圈10的顶部,而下铁氧体-电介质屏蔽层26屏蔽电感线圈11的底部。电感线圈10中心的空芯14与电感线圈11中心的空芯15对齐。半导体芯片30(未示出)可以放置在上铁氧体-电介质屏蔽层24上方或下铁氧体-电介质屏蔽层26下方。

49.图10是另一种具有两个线圈的屏蔽式电感器半导体封装的截面图。在该变体中,两个电感线圈10、11被中间铁氧体-电介质屏蔽层28隔开,该中间铁氧体-电介质屏蔽层28的电介质层21夹住铁氧体层13。在该变体中,电感线圈10通过铁氧体层13与电感线圈11屏蔽。另外,电感线圈10、11的电感可以通过增加铁氧体层13而增加。

50.图11是一个双线圈屏蔽式电感器半导体封装的三维图。在本实施例中,有两层线圈,上电感线圈10(未示出,其被上铁氧体-电介质屏蔽层24遮挡隐藏)和下电感线圈11。电感线圈10、11之间可以有电介质层21(未示出),如图9所示,或者中间铁氧体-电介质屏蔽层28(未示出),如图10所示。电感线圈10、11之间的间距在图11和12中被扩大,以便更好地观察,但实际上电感线圈10、11之间的间距会接近得多,如图9-10所示。因此,即使在有两层电感线圈10、11的情况下,也可以获得一个相对平坦的、薄型封装。

51.例如通过环氧树脂或其他键合,半导体芯片30贴附到芯片贴装焊盘34上。焊线42在半导体芯片30上的焊盘和引线框架焊盘40之间布线。一些焊线则从半导体芯片30上的焊盘走线到芯片贴装焊盘34。

52.引线框架焊盘40位于引线框架立柱46的顶部,该立柱连接到从封装底部突出的封装引脚,并且在焊接到更大系统的pcb时可以安置在pcb中的孔中。引线框架立柱45、46可以弯曲或连接到引线框架的其他部分(未示出),这些部分通向外部封装引脚、焊球或其他外部连接器(未示出)。

53.引线框架立柱45、46形成一个矩形,围绕着半导体芯片30、芯片贴装焊盘34和电感线圈10,电感线圈10大部分被上铁氧体-电介质屏蔽层24遮挡隐藏。电感线圈10顶部被上铁氧体-电介质屏蔽层24覆盖。

54.尽管上电感线圈10大部分被上铁氧体-电介质屏蔽层24覆盖,但是下电感线圈11是可见的。下铁氧体-电介质屏蔽层26贴附在下电感线圈11的底部。线圈立柱16连接上电感线圈10和下电感线圈11的外侧绕组。

55.芯片贴装焊盘34的底部连接到中心柱36,中心柱36穿过上铁氧体-电介质屏蔽层24的靠近空芯14的中央开口。上铁氧体-电介质屏蔽层24的这个开口允许中心柱36将芯片贴装焊盘34连接到电感线圈10的中心绕组。当电感线圈10、11并联电连接时,中心柱36可以

向下延伸并连接到上电感线圈10和下电感线圈11的中心绕组。

56.图12是一个双线圈层屏蔽式电感器半导体封装的三维图,其中去除了上铁氧体-电介质屏蔽层以便更好地显示出电感线圈。在图12中,图11的上铁氧体-电介质屏蔽层24已被移除。电感线圈10是一个平面线圈,从其中心的中心柱36向外盘绕,中心柱36将芯片贴装焊盘34电连接到电感线圈10的中心绕组。上电感线圈10的最外侧绕组连接到线圈立柱16和连接到下电感线圈11的最外侧绕组。线圈立柱16比引线框架立柱46短。

57.半导体芯片30上的大多数焊盘通过焊线42和引线框架焊盘40与引线框架立柱46末端的封装引脚形成电连接。然而,半导体芯片30的三个焊盘通过焊线连接到芯片贴装焊盘34的上表面。然后从芯片贴装焊盘34的上表面到芯片贴装焊盘34的下表面和中心柱36形成电连接。

58.因此,当中心柱36向下延伸时(未示出),从半导体芯片30到上电感线圈10的中心绕组和下电感线圈11的中心绕组形成电连接。上电感线圈10和下电感线圈11的外侧绕组通过线圈延长线48连接到引线框架外立柱45,引线框架外立柱45在顶部有引线框架焊盘41,并且在底部连接到外部封装引脚。引线框架焊盘41不接收来自半导体芯片30的焊线42,而是通过线圈延长线48连接到电感线圈10。引线框架焊盘41除了用于封装对称性之外没有任何功能,可以删除。

59.因此,上电感线圈10和下电感线圈11在半导体芯片30的三个焊盘和外部封装管脚之间提供了并联电感。当变化的电流流过电感线圈10、11时,产生的电磁场被上铁氧体-电介质屏蔽层24(图11)屏蔽,以免在半导体芯片30中引起emi。

60.图13是另一种具有两个线圈的屏蔽式电感器半导体封装的截面图。在该变体中,如图10一样,两个电感线圈10、11被中间铁氧体-电介质屏蔽层28隔开,该中间铁氧体-电介质屏蔽层28的电介质层21夹住铁氧体层13。在该变体中,空芯14和空芯15通过一个较大的孔连接在一起,该孔延伸穿过铁氧体层12、13和电介质层20、21。尽管铁氧体层12中有一个开口,磁通量可能会从这里泄漏并在半导体芯30中引起emi,但该开口仍然是相对较小的,而且位于线圈中间,所以泄漏很小。较大的孔为连接线圈10、11提供了更多空间。中央开口允许中心柱36穿过半导体芯片30和电感线圈10之间的铁氧体层12和电介质层20。【替代实施例】

61.发明人补充了若干其他实施例。例如,半导体芯片可以是硅芯片,如标准的cmos芯片,也可以是另一衬底上的硅,或其他材料,如gaas。可以有一个以上的半导体芯片30和一个以上的电感器。可以用其他封装技术来代替,这些技术使用引线框架或类似物,或者是无引线的。

62.半导体芯30是一个集成电路(ic)或分立元件,如mosfet,并且可以是各种类型,如互补金属氧化物半导体(cmos)或bicmos。典型的ic有数以千计的晶体管,它们在衬底上的半导体材料中一起形成,这些晶体管通过集成布线(如金属迹线)连接。功率ic可能有更大但更少的晶体管,例如只有10个晶体管。半导体芯片30可以有用于电源转换器的功率晶体管,如开关模式电源(smps)。

63.虽然已经描述了将屏蔽式电感器半导体封装安装到pcb系统板上的引脚和球,但还有许多变化是可能的。引脚可以是引线、弯曲引线或弯曲引脚、平面的表面安装焊盘,并且可以安装到pcb上的孔中或pcb表面上的焊盘上。

64.虽然外部封装引脚已被描述为放置在屏蔽式电感器半导体封装的周边,但这些引脚、球或连接器中的一些或全部可以是网格或阵列,如在球栅阵列(bga)封装中。

65.虽然已经描述了塑料封装的封装,但屏蔽式电感器半导体封装可以是陶瓷封装或混合封装。pcb可以是刚性的或柔性的,也可以是系统中的一些其他类型的基板或更大的模块或支架或框架。

66.虽然在图5中电感线圈10显示为延伸超过上铁氧体-电介质屏蔽层24,但上铁氧体-电介质屏蔽层24也可以完全覆盖电感线圈10。上铁氧体-电介质屏蔽层24和下铁氧体-电介质屏蔽层26都可以延伸超过电感线圈10,并被挤压或捏在一起,相互接触,以密封电感线圈10的周边边缘。

67.虽然图11中已经显示了电感线圈10、11的并联连接,但上电感线圈10和下电感线圈11可以使用额外的引线框架元件或立柱,将上电感线圈10的外侧绕组与下电感线圈11的中心绕组连接起来,而串联连接。然后可以删除线圈立柱16,下电感线圈11的外侧绕组连接到引线框架外立柱45,进行外部连接。

68.没有使用引线框架外立柱45从电感线圈10进行外部连接,而是在封装内进行内部连接,从电感线圈10的外侧绕组返回到没有外部连接的引线框架立柱46之一,通过焊线42到半导体芯片30上的焊盘。其他内部连接也是可能的。

69.电感线圈10被认为是空芯电感器,因为平面线圈中心的空芯14没有铁氧体,即使铁氧体层12在电感线圈10的平面上方和下方,像铁氧体磁芯一样增加了线圈的电感。中心柱36可以在电感线圈10中心的空芯内。尽管中心柱36是连接到电感线圈10,但它不被认为是电感线圈10的金属芯。

70.电感线圈10是金属线圈,通过中心柱36和芯片贴装焊盘34连接到半导体芯片30,另一端通过引线框架外立柱45连接到外部封装引脚,因此电感线圈10可以被认为是封装的引线框架的一部分,同时还有引线框架焊盘40和引线框架立柱46。因此,电感线圈10是与封装引线框架集成的。

71.通过使用铁氧体层12,由流过电感线圈10的电流产生的、并被半导体芯片30上的金属迹线或其他元件接收的emi至少减少90%。电磁通量被置于电感线圈10和半导体芯片30之间的铁氧体层12阻挡。电介质层20防止电感线圈10与半导体芯片30或其他导体发生短路。

72.本发明的背景部分可以包含关于本发明问题或环境的背景资料,而不是描述他人的现有技术。因此,在背景技术部分中包含的材料并不是申请人对现有技术的承认。

73.本文描述的任何方法或过程都是机器实施的或计算机实施的,旨在由机器、计算机或其他设备来执行,而不打算在没有机器辅助的情况下仅由人类执行。产生的有形结果可以包括报告或其他机器生成的显示在诸如计算机显示器、投影设备、音频生成设备和相关媒体设备的显示设备上,可以包括也是机器生成的硬拷贝打印输出。其他机器的计算机控制是另一个有形的结果。

74.所述的任何优点和好处不一定适用于本发明的所有实施例。通常,在“装置”一词前面的一个或多个词是一个标签,目的是为了便于权利要求元素的引用,而不是为了表达结构上的限制。这种装置加功能的权利要求不仅要涵盖本文所述的用于执行该功能的结构及其结构等同物,而且要涵盖等效结构。例如,虽然钉子和螺钉具有不同的构造,但它们是

等效结构,因为它们都执行紧固功能。信号通常是电子信号,但也可以是光信号,例如可以通过光纤线路传输。

75.对本发明实施例的上述描述是为了说明和描述的目的而提出的。它并不打算是详尽的,也不打算将本发明限制在所公开的精确形式中。根据上述教学,许多修改和变化是可能的。其目的是本发明的范围不受本详细说明的限制,而是受附于权利要求书的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1