一种超结半导体器件及其制造方法与流程

1.本发明涉半导体集成电路制造领域,特别是涉及一种超结半导体器件及其制造方法。

背景技术:

2.超结(super junction)结构为n型柱和p型柱交替排列组成的结构。若以超结结构取代垂直双扩散金属-氧化物半导体场效应晶体管 (vertical double-diffused metal-oxide-semiconductor,vdmos)器件中的n型漂移区,于导通状态下通过n型柱提供导通通路,导通时p型柱不提供导通通路;于截止状态下由p型柱与n型柱共同承受反偏电压,形成超结金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,全称mosfet,简称mos)。

3.超结mosfet能在反向击穿电压与传统的vdmos器件一致的情况下,通过使用低电阻率的外延层,而使器件的导通电阻大幅降低。相关技术中的超结结构中p型柱为矩形结构,在固定其击穿电压时,其特征电阻较高。

4.相关技术中具有超结结构的半导体器件,皆需要于制程流程中,额外掺杂注入与退火制程,来提高超结结构的击穿电压,同时还能使半导体器件具有良好的抗冲击能力,另外,现有的超结结构,在相同击穿电压之下,mosfet需要降低特征电阻,在组件工作时损耗功率也会减小。

5.为此,亟待开发一种用于超结mosfet时,利于降低其特征电阻的超结结构。

技术实现要素:

6.本发明的目的旨在至少解决所述技术缺陷之一,通过蚀刻调整沟槽形成超结结构的阶梯状深沟槽,并于沟槽中填入外延,其可兼容于现行深沟槽超结结构制程中,达到相同击穿电压下,降低特征电阻之功效。

7.为此,本发明的目的在于提出一种超结半导体器件藉由阶梯状沟槽,能实现提高器件的击穿电压,降低导通电阻。

8.为了实现上述目的,本发明提供一种超结结构及其制造方法。

9.本技术实施例提供一种超结半导体器件,在所述超结半导体器件的截面上,所述超结半导体器件包括:n型外延层,所述n型外延层上形成有至少一个沟槽,在所述沟槽中填充有p型柱,所述p型柱和由所述沟槽之外的所述n型外延层构成的n型柱交替排列构成所述半导体器件的超结结构;所述沟槽至少包含自下而上依次相接的第一次沟槽、第二次沟槽和第三次沟槽,其中,所述第三次沟槽为跑道形,且所述第一次沟槽、所述第二次沟槽和所述第三次沟槽的宽度依次递增。

10.在一些实施例中,所述第一次沟槽和所述第二次沟槽中,至少有一个为矩形。

11.在一些实施例中,所述第一次沟槽、所述第二次沟槽和所述第三次沟槽的侧面高度相同。

12.在一些实施例中,沿第一方向、所述第一次沟槽、所述第二次沟槽和所述第三次沟槽具有同一对称轴,且每一所述次沟槽的侧面平行于所述对称轴,所述第一方向为所述沟槽的深度方向。

13.在一些实施例中,沿所述第一方向、相邻两个所述次沟槽的宽度之比为的2/3。

14.本技术实施例提供一种超结半导体器件的制造方法,所述超结半导体器件制造方法包括如下步骤:s1、提供n型外延层,在所述n型外延层上形成硬质掩模层,通过光刻刻蚀工艺将沟槽形成区域的所述硬质掩模层打开,打开至第一宽度;s2、以所述第一宽度的硬质掩模层为掩模刻蚀所述n型外延层至第一深度,形成第一次沟槽;s3、通过光刻刻蚀工艺将沟槽形成区域的所述硬质掩模层打开至第二宽度;s4、以所述第二宽度的硬质掩模层为掩模刻蚀所述n型外延层至第二深度,形成所述沟槽的第二次沟槽,且所述第一深度大于所述第二深度;s5、通过光刻刻蚀工艺将沟槽形成区域的所述硬质掩模层打开至第三宽度;s6、以所述第三宽度的硬质掩模层为掩模刻蚀所述n型外延层至第三深度,形成第三预次沟槽,并通过开槽器在所述预设第三次沟槽内壁两侧沿其长度方向开出跑道形槽,形成所述沟槽的第三次沟槽,且所述第二深度大于所述第三深度;s7、在所述沟槽中进行填充p型外延层形成p型柱,去除所述硬质掩模层;s8、填充于所述沟槽中的所述p型柱和由所述沟槽之外的所述n型外延层构成的n型柱交替排列构成所述半导体器件的超结结构。

15.在一些实施例中,所述第一次沟槽和所述第二次沟槽中,至少有一个为矩形。

16.在一些实施例中,每一所述次沟槽的侧面高度相同。

17.在一些实施例中,沿第一方向、所述第一次沟槽、所述第二次沟槽和所述第三次沟槽具有同一对称轴,且每一所述次沟槽的侧面平行于所述对称轴,所述第一方向为所述沟槽的深度方向。

18.在一些实施例中,沿所述第一方向、相邻两个所述次沟槽的宽度之比为的2/3。

19.本技术实施例提供的超结结构中,通过蚀刻调整沟槽形成超结结构的阶梯状深沟槽,其中包括跑道形的次沟槽,并于沟槽中填入外延,其可兼容于现行深沟槽超结结构制程中,达到相同击穿电压下,降低特征电阻之功效。

20.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

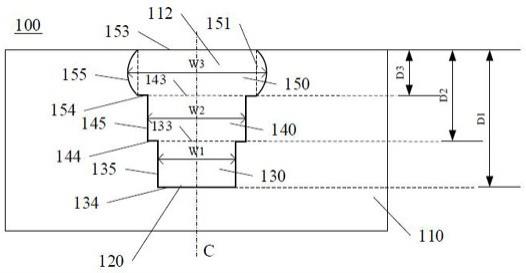

21.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:图1为本技术实施例提供的超结半导体器件的截面结构示意图一;图2为本技术实施例提供的超结半导体器件的截面示意图二;图3为本技术实施例提供的超结半导体器件的制造方法流程示意图。

具体实施方式

22.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的组件或具有相同或类似功能的组件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

23.在本说明书的描述中,参考术语「一个实施例」、「一些实施例」、 「示例」、「具体示例」、或「一些示例」等的描述意指结合所述的实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

24.本技术实施例提供一种超结半导体器件,图1为本技术实施例提供的超结半导体器件的截面结构示意图一。如图1所示,在超结半导体器件的截面上,超结半导体器件100包括,n型外延层110,所述n型外延层110上形成有至少一沟槽120,在沟槽120中填充有p型柱112,填充于沟槽120中的p型柱112和由沟槽120之外的n型外延层110构成的n型柱交替排列构成半导体器件的超结结构。

25.本技术实施例提供的所述沟槽至少包含自下而上依次相接的第一次沟槽、第二次沟槽和第三次沟槽,其中,所述第三次沟槽为跑道形,且所述第一次沟槽、所述第二次沟槽和所述第三次沟槽的宽度依次递增。

26.请参考图1,这里,沟槽120包含三个次沟槽,分别为第一次沟槽130、第二次沟槽140、第三次沟槽150。第一次沟槽130、第二次沟槽140、第三次沟槽150由下而上相邻连接排列。第一次沟槽130具有第一顶部133、第一底部134以及第一侧面135。第二次沟槽140具有第二顶部143、第二底部144以及第二侧面145。第三次沟槽150为跑道形,具有第三顶部153、第三底部154以及第三侧面155。

27.这里,所述第一次沟槽130和所述第二次沟槽140中,至少有一个为矩形。在本技术实施例中, 第一次沟槽130和第二次沟槽140均为矩形,在一些实施例中,第一次沟槽130和第二次沟槽140可以均为跑道形。

28.第一侧面135的高度与第二侧面145的高度相同。第二侧面145的高度与第三侧面155的高度相同。第一侧面135的高度与第三侧面155的高度相同。

29.沿第一方向,第一次沟槽130、第二次沟槽140以及第三次沟槽150具有同一对称轴c。对称轴c垂直于第一顶部133、第一底部134。对称轴c垂直于第二顶部143、第二底部144。对称轴c垂直于第三顶部153、第三底部154。第一次沟槽130的第一侧面135、第二次沟槽140的第二侧面145以及第三次沟槽的第三侧面155分别平行于对称轴c,第一方向为所述沟槽的深度方向。

30.沟槽120的第一次沟槽130、第二次沟槽140、第三次沟槽150由下而上相邻连接排列。第一次沟槽130位于沟槽120最底端,第一次沟槽130顶部开口连接第二次沟槽140底部。第二次沟槽140位于第一次沟槽130上方。第二次沟槽140顶部连接第三次沟槽150底部。

31.第一次沟槽130具有第一宽度w1。第二次沟槽140具有第二宽度w2。第三次沟槽150具有第三宽度w3,这里第三次沟槽150为跑道形,因此,第三次沟槽150的第三宽度w3为所述跑道形结构的特征宽度(即最大宽度)。第一次沟槽130的第一宽度w1小于相邻上方的第二次沟槽140的第二宽度w2,第一宽度w1为第二宽度w2的2/3。第二次沟槽140的第二宽度w2小于相邻上方的第三次沟槽150的第三宽度w3,第二宽度w2为第三宽度w3的2/3。

32.在一些实施例中,沟槽120包含六个次沟槽,自下而上分别为第四次沟槽、第五次沟槽、第六次沟槽、第一次沟槽、第二次沟槽和第三次沟槽,其中,第三次沟槽和第六次沟槽为跑道形,且第四次沟槽与第一次沟槽形状相同,第五次沟槽和第二次沟槽形状相同。

33.本技术实施例提供另一种超结半导体器件,图2为本技术实施例提供的超结半导体器件的截面示意图二,如图2所示,在超结半导体器件的截面上,超结半导体器件100中包含n型外延层110,所述n型外延层110上形成有至少一沟槽120,在沟槽120中填充有p型柱112,填充于沟槽120中的p型柱112和由沟槽120之外的n型外延层110构成的n型柱交替排列构成超结结构。

34.在本技术实施例中,所述沟槽120包含自下而上依次相接的第七次沟槽170、第八次沟槽180、第九次沟槽190、第一次沟槽130、第二次沟槽140、第三次沟槽150,其中,所述第三次沟槽150为跑道形,且第七次沟槽170、第八次沟槽180、第九次沟槽190、第一次沟槽130、第二次沟槽140、第三次沟槽150的宽度依次递增。

35.第七次沟槽170、第八次沟槽180、第九次沟槽190的侧面高度与第一次沟槽130、第二次沟槽140和第三次沟槽150均相等,且沿第一方向与第一次沟槽130、第二次沟槽140以及第三次沟槽150具有同一对称轴c;第七次沟槽170具有第七宽度w7,第八次沟槽180具有第八宽度w8,第九次沟槽190具有第九宽度w9,且第九宽度w9为第一宽度w1的2/3,第八宽度w8为第九宽度w9的2/3,第七宽度w7为第八宽度w8的2/3。

36.如图3所示,为本技术实施例提供的超结半导体器件的制造方法流程示意图。请参考图1及图3。超结半导体器件100,在n型外延层110上形成有至少一沟槽120。在沟槽120中填充有p型柱112,填充于沟槽120中的p型柱112和由沟槽120之外的n型外延层110组成的n型柱交替排列组成超结结构。超结半导体器件100的制造方法包括以下步骤:s1、提供n型外延层110,在n型外延层110上形成硬质掩模层,通过光刻刻蚀工艺将沟槽120形成区域的硬质掩模层打开,打开至第一宽度w1。

37.s2、以第一宽度w1的硬质掩模层为掩模,刻蚀n型外延层110至第一深度d1,形成第一次沟槽130。

38.s3、通过光刻刻蚀工艺将沟槽120形成区域的硬质掩模层打开至第二宽度w2。

39.s4、以第二宽度w2的硬质掩模层为掩模,刻蚀n型外延层110至第二深度d2,形成第二次沟槽140。且第一深度d1大于第二深度d2,第二次沟槽140的宽度为第二宽度w2,第二宽度w2大于第一宽度w1。

40.s5、通过光刻刻蚀工艺将沟槽120形成区域的硬质掩模层打开至第三宽度w3。

41.s6、以第三宽度w3的硬质掩模层为掩模,刻蚀n型外延层110至第三深度d3,形成预设第三次沟槽151,通过开槽器在预设第三次沟槽151的两侧内壁沿其长度方向开出跑道形槽,形成第三次沟槽150,第二深度d2大于第三深度d3。第三次沟槽150的宽度为第三宽度w3,第三宽度w3大于第二宽度w2。

42.s7、在沟槽120中进行填充p型外延层形成p型柱112,去除硬质掩模层。

43.s8、填充于沟槽120中的p型柱112和由沟槽120之外的n型外延层110构成的n型柱交替排列构成半导体器件的超结结构。

44.沟槽120的第一次沟槽130、第二次沟槽140、第三次沟槽150由下而上相邻连接排列。第一次沟槽130位于沟槽120最底端,第一次沟槽130顶部开口连接第二次沟槽140底部。第二次沟槽140位于第一次沟槽130上方。第二次沟槽140顶部连接第三次沟槽150底部。第一次沟槽130具有第一宽度w1。第二次沟槽140具有第二宽度w2。第三次沟槽150具有第三宽度w3,第三次沟槽的第三宽度w3为所述跑道形结构的特征宽度(即最大宽度)。第一次沟槽

130的第一宽度w1小于相邻上方的第二次沟槽140的第二宽度w2,第一宽度w1为第二宽度w2的2/3。第二次沟槽140的第二宽度w2小于相邻上方的第三次沟槽150的第三宽度w3,第二宽度w2为第三宽度w3的2/3。

45.藉由上述步骤s1至步骤s8,完成沟槽120的制程。沟槽120包含三个次沟槽,分别为第一次沟槽130、第二次沟槽140、环形的第三次沟槽150由下而上相邻连接排列。沟槽120为一跑道形阶梯状,其中,第一宽度w1小于第二宽度w2,第二宽度w2小于第三宽度w3。第一侧面135的高度与第二侧面145的高度相同。第二侧面145的高度与第三侧面155的高度相同。第一侧面135的高度与第三侧面155的高度相同。

46.第一次沟槽130、第二次沟槽140以及第三次沟槽150于水平方向共享同一对称轴c。对称轴c垂直于第一顶部133、第一底部134。对称轴c垂直于第二顶部143、第二底部144。对称轴c垂直于第三顶部153、第三底部154。第一次沟槽130的第一侧面135、第二次沟槽140的第二侧面145以及第三次沟槽的第三侧面155分别平行于对称轴c。

47.第一次沟槽130具有第一宽度w1。第二次沟槽140具有第二宽度w2。第三次沟槽150具有第三宽度w3。第一次沟槽130的第一宽度w1小于相邻上方的第二次沟槽140的第二宽度w2,第一宽度w1为第二宽度w2的2/3。第二次沟槽140的第二宽度w2小于相邻上方的第三次沟槽150的第三宽度w3,第二宽度w2为第三宽度w3的2/3。

48.尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在不脱离本发明的原理和宗旨的情况下在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。本发明的范围由所附权利要求及其等同限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1