基于硅基的双面封装方法与流程

1.本发明属于半导体封装技术领域,更具体的基于硅基的双面封装方法。

背景技术:

2.随着集成电路技术的发展,封装与晶圆制造的边界出现交叉,有相互趋近、 融合的趋势。当前及未来,封装不再仅仅是保护和引出作用,还具备了强大的 集成能力,通过封装集成,解决半导体工艺目前的困局,即所谓超越摩尔定律。 封装集成通过灵活的手段将多类型、多功能器件进行物理尺寸和性能上的整合, 实现soc希望达到但短期很难达到的高性能、低功耗、小型化的效果。

3.近年来,随着摩尔定律逐渐走到尽头,fan-out(扇出型封装)由于可以高 密度集成多功能异构芯片从而形成性能优异的微系统组件,受到越来越多的重 视。但是随着对于封装小型化和规模化封装的需求,现有的fan-out工艺由于 本身结构限制无法实现芯片堆叠和大量贴装被动器件,且容易出现翘曲问题。

技术实现要素:

4.本发明实施例提供基于硅基的双面封装方法,可以提供实现芯片堆叠工艺 的同时,也解决芯片翘边的问题。

5.本发明实施例提供基于硅基的双面封装方法,包括:

6.在dummy硅片的上表面刻蚀出凹槽,在所述凹槽内设置第一芯片,以使 所述第一芯片和所述dummy硅片的上表面具有相同的高度;

7.在所述第一芯片的上表面制备第一扇出布线层,以使所述第一扇出布线层 完全覆盖所述dummy硅片的上表面;

8.在所述第一扇出布线层的上表面倒装tsv芯片,并对所述tsv芯片进行 贴膜塑封,以使塑封材料的上表面与所述tsv芯片的上表面具有相同的高度;

9.在所述tsv芯片的上表面制备第二扇出布线层,在所述第二扇出布线层 的上表面制备多个锡球。

10.优选地,在所述第一扇出布线层的上表面倒装tsv芯片,具体包括:

11.在所述第一扇出布线层的上表面倒装tsv芯片,并间隔两个所述tsv芯 片设置一个被动元器件;

12.相邻的tsv芯片之间存在间隙,被动元器件与相邻的tsv芯片之间存在 间隙。

13.优选地,所述被动元器件的上表面与第二扇出布线层之间存在间隙。

14.优选地,所述tsv芯片上设置多个tsv金属连接孔。

15.优选地,所述在所述第二扇出布线层的上表面制备多个锡球之后,还包括:

16.将整个panel进行切割,得到多个单颗封装芯片。

17.本发明实施例提供基于硅基的双面封装方法,包括:在dummy硅片的上 表面刻蚀出凹槽,在所述凹槽内设置第一芯片,以使所述第一芯片和所述 dummy硅片的上表面具有

相同的高度;在所述第一芯片的上表面制备第一扇 出布线层,所述第一扇出布线层完全覆盖所述dummy硅片的上表面;在所述 第一扇出布线层的上表面倒装tsv芯片,并对所述tsv芯片进行贴膜塑封, 以使塑封材料的上表面与所述tsv芯片的上表面具有相同的高度;在所述tsv 芯片的上表面制备第二扇出布线层,在所述第二扇出布线层的上表面制备多个 锡球。该方法通过在dummy硅片上垂直堆叠设置第一芯片和tsv芯片的方法, 可以有效缩短信号传输路径,提高产品电性能;再者,以dummy硅片为基础 进行扇出布线,产品的塑封平整度比较好,提高产品的散热性能的同时也解决 了产品翘曲的问题。

附图说明

18.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施 例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述 中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付 出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

19.图1为本发明实施例提供的基于硅基的双面封装方法流程示意图;

20.图2a为本发明实施例提供的在dummy硅片上设置第一芯片结构示意图; 图2b为本发明实施例提供的图2a包括的单颗封装芯片放大示意图;

[0021][0022]

图3a为本发明实施例提供的在第一扇出布线层上是设置tsv芯片结构示 意图;

[0023]

图3b为本发明实施例提供的图3a包括的单颗封装芯片放大示意图;

[0024]

图4a为本发明实施例提供的制备第二扇出布线层结构示意图;

[0025]

图4b为本发明实施例提供的图4a包括的单颗封装芯片放大示意图;

[0026]

图5a为本发明实施例提供的制备锡球结构示意图;

[0027]

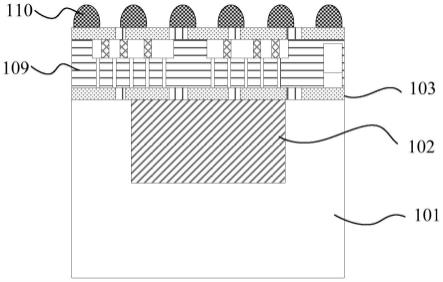

图5b为切割后单颗封装芯片结构示意图;

[0028]

其中,101~dummy硅片,102~第一芯片,103~第一次扇出布线层, 104~tsv芯片,105~被动元器件,106~tsv金属连接孔,107~tsv芯片与第 一次布线层连接线,108~第二次扇出布线层,109~塑封材料,110~锡球。

具体实施方式

[0029]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清 楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是 全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造 性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0030]

图1为本发明实施例提供的基于硅基的双面封装方法流程示意图;图2a 为本发明实施例提供的在dummy硅片上设置第一芯片结构示意图;图2b为 本发明实施例提供的图2a包括的单颗封装芯片放大示意图;图3a为本发明 实施例提供的在第一扇出布线层上是设置tsv芯片结构示意图;图3b为本发 明实施例提供的图3a包括的单颗封装芯片放大示意图;图4a为本发明实施 例提供的制备第二扇出布线层结构示意图;图4b为本发明实施例提供的图4a 包括的单颗封装芯片放大示意图;图5a为本发明实施例提供的制备锡球结构 示意图;图5b为切割后单颗封装芯片结构示意图;

[0031]

以下结合图1、图2a~图5b为例,详细介绍本发明实施例提供的基于硅 基的双面封装方法。

[0032]

具体地,如图1所示,本发明实施例提供的基于硅基的双面封装方法包括 有以下步骤:

[0033]

步骤101,在dummy硅片的上表面刻蚀出凹槽,在所述凹槽内设置第一 芯片,以使所述第一芯片和所述dummy硅片的上表面具有相同的高度;

[0034]

步骤102,在所述第一芯片的上表面制备第一扇出布线层,所述第一扇出 布线层完全覆盖所述dummy硅片的上表面;

[0035]

步骤103,在所述第一扇出布线层的上表面倒装tsv(through-silicon via, 穿过硅基板的垂直电互连)芯片,并对所述tsv芯片进行贴膜塑封,以使塑 封材料的上表面与所述tsv芯片的上表面具有相同的高度;

[0036]

步骤104,在所述tsv芯片的上表面制备第二扇出布线层,在所述第二扇 出布线层的上表面制备多个锡球。

[0037]

在步骤101中,如图2a和2b所示,在提供的dummy硅片101上根据设 定第一芯片102的位置进行刻蚀,即在dummy硅片101的上表面刻蚀出设置 第一芯片102的凹槽,然后将第一芯片102设置在凹槽内。需要说明的是,第 一芯片102在dummy硅片101上的设置位置是预先设定好的,在此,对第一 芯片102在dummy硅片101上的设置位置不做限定。

[0038]

进一步地,由于在dummy硅片101上还有制备第一次扇出布线层103, 因此,需要确定第一芯片102的上表面和dummy硅片101的上表面具有相同 的高度。在此,对设置第一芯片102的凹槽的宽度、深度均不做具体的限定, 只要确保在dummy硅片101上设置第一芯片102之后,第一芯片102的上表 面和dummy硅片101的上表面具有相同的高度即可。

[0039]

在步骤102中,在第一芯片102的上表面制备第一次扇出布线层103,确 保第一次扇出布线层103在覆盖第一芯片102的同时,也完全覆盖dummy硅 片101的上表面。需要说明的是,在图2a所示的整块panel中,dummy硅片 101上可以设置多个凹槽,为例确保切割后多个单颗封装芯片具有相同的功能, 因此,dummy硅片101上刻蚀的多个凹槽之间的间距相等,在此,对相邻的 凹槽之间的间距不做限定。

[0040]

在步骤103中,在第一扇出布线层的上表面倒装tsv芯片104和设置被 动元器件105,如图3a和3b所示,在一个单颗封装芯片上包括两个tsv芯 片104和一个被动元器件105,因此,在整块panel中,tsv芯片104和一个 被动元器件105需要间隔设置,即每设置两个tsv芯片104,则需要设置一个 被动元器件105,且两个tsv芯片104需要位于第一芯片102的上层,且被动 元器件105在垂直方向的投影与第一芯片102存在间隙,即被动元器件105在 垂直方向的投影与第一芯片102在垂直方向的投影不相交。

[0041]

在本发明实施例中,在第一次扇出布线层103的上表面埋入贴装被动元器 件105,可以实现封装系统化集成需求,同时缩短了被动元器件105与芯片之 间的传输路径,优化了产品的性能。

[0042]

在本发明实施例中,在tsv芯片104上还设置有多个tsv金属连接孔106, 通过该tsv金属连接孔106,可以与tsv芯片104上表面形成的第二次扇出 布线层连接108,实现电气连接。

[0043]

进一步地,设置在第一次扇出布线层103的上表面的tsv芯片104和被 动元器件

105之间存在间隙,在此,对间隙的具体数值不做限定。

[0044]

需要说明的是,当tsv芯片104设置在第一次扇出布线层103的上表面 时,tsv芯片104和第一次扇出布线层103之间还包括有tsv芯片与第一次 布线层连接线107。

[0045]

进一步地,对tsv芯片104、被动元器件105和第二次扇出布线层连接108的上表面进行贴膜塑封,即在第二次扇出布线层连接108的上表面设置塑 封材料109,最后确定塑封材料109的上表面与tsv芯片104的上表面具有相 同的高度,即塑封材料109不能覆盖tsv芯片104。

[0046]

如图4a、4b所示,在tsv芯片104的上表面制备第二次扇出布线层连接 108,涂覆绿油;进一步的,如图5a所示,在第二次扇出布线层连接108上制 备多个锡球110,从而得到整块panel。

[0047]

在实际应用中,将整块panel进行切割,即可以得到如图5b所示的多个 单颗封装芯片。

[0048]

综上所述,本发明实施例提供基于硅基的双面封装方法,包括:在dummy 硅片的上表面刻蚀出凹槽,在所述凹槽内设置第一芯片,以使所述第一芯片和 所述dummy硅片的上表面具有相同的高度;在所述第一芯片的上表面制备第 一扇出布线层,所述第一扇出布线层完全覆盖所述dummy硅片的上表面;在 所述第一扇出布线层的上表面倒装tsv芯片,并对所述tsv芯片进行贴膜塑 封,以使塑封材料的上表面与所述tsv芯片的上表面具有相同的高度;在所 述tsv芯片的上表面制备第二扇出布线层,在所述第二扇出布线层的上表面 制备多个锡球。该方法通过在dummy硅片上垂直堆叠设置第一芯片和tsv芯 片的方法,可以有效缩短信号传输路径,提高产品电性能;再者,以dummy 硅片为基础进行扇出布线,产品的塑封平整度比较好,提高产品的散热性能的 同时也解决了产品翘曲的问题。

[0049]

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基 本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要 求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

[0050]

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发 明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及 其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1