一种共用DBR的多波长VCSEL激光器芯片的制作方法

一种共用dbr的多波长vcsel激光器芯片

技术领域

1.本发明涉及半导体光电子技术领域,特别涉及一种共用dbr的多波长vcsel激光器芯片。

背景技术:

2.垂直腔面发射激光器芯片(vertical cavity surface emitting laser, vcsel)从诞生起就作为新一代光存储和光通信应用的核心器件,应用在光并行处理、光识别、光互联系统和光存储等领域。随着工艺、材料技术改进,vcsel器件在功耗、制造成本、集成、散热等领域的优势开始显现,逐渐应用于数据通信,工业热加工、环境监测、医疗设备等商业级应用以及3d感知等消费级应用。vcsel芯片具有良好的经济性,实用性及可靠性,为各行各业中的信息交换带来了极大的便利。

3.现有技术中,一颗vcsel芯片通常只能激射一种波长,然而在数据通讯或者激光雷达等技术领域往往需要同时实现多种波长的激射,因此只能将多颗不同波长的vcsel芯片通过封装(贴片、打线)集成在一起,使其作为具有多种波长的激光发射单元。但是这种通过封装实现集成的方式,占用空间大,封装成本高,封装过程中会带来较大的良率损失,而且还会引入过多的潜在的贴片、打线缺陷,影响整体的可靠性。

技术实现要素:

4.本发明提供一种共用dbr的多波长vcsel激光器芯片,其主要目的在于解决现有技术存在的问题。

5.本发明采用如下技术方案:一种共用dbr的多波长vcsel激光器芯片,包括衬底以及至少两个堆叠于衬底表面的vcsel单元;各所述vcsel单元自下而上包括底部n型dbr、有源区、掩埋隧穿结和顶部n型dbr;位于下层的vcsel单元的顶部n型dbr与位于上层的vcsel单元的底部n型dbr为一体式的共用dbr;与共用dbr相邻的上下两个vcsel单元的中心波长均位于该共用dbr的阻带范围内,并且位于下层的vcsel单元的中心波长大于位于上层的vcsel单元的中心波长。

6.进一步,所述共用dbr的阻带宽度的计算公式为:式中: 为阻带宽度; 为折射率差值;为位于下层的vcsel单元的中心波长;为有效折射率;则共用dbr的阻带范围为 。

7.进一步,各所述vcsel单元的中心波长的取值范围为600-2000nm。

8.进一步,所述衬底为gaas衬底,位于最下层的vcsel单元的底部n型dbr、位于最上层的vcsel单元的顶部n型dbr以及各所述共用dbr均是由al

x

ga

1-x

as/alyga

1-y

as材料周期堆

叠组成的反射镜,并且周期数均为20-70。

9.更进一步,各所述共用dbr的al

x

ga

1-x

as/alyga

1-y

as材料中,x的取值范围为0.8-1,y的取值范围为0-0.2。

10.进一步,所述衬底为inp衬底,位于最下层的vcsel单元的底部n型dbr、位于最上层的vcsel单元的顶部n型dbr以及各所述共用dbr均是由in

0.52

aliga

0.48-i

as/in

0.52

aljga

0.48-j

as或者in

0.52

alkga

0.48-k

as/inp材料周期堆叠组成的反射镜,并且周期数均为20-70。

11.更进一步,各所述共用dbr的in

0.52

aliga

0.48-i

as/in

0.52

aljga

0.48-j

as材料或in

0.52

alkga

0.48-k

as/inp材料中,i、j和k的取值范围均为0-0.48。

12.进一步,位于最下层的vcsel单元的底部n型dbr、位于最上层的vcsel单元的顶部n型dbr以及各所述共用dbr的反射率均大于99%,并且各反射镜的反射率由下至上逐渐递减。

13.进一步,各所述vcsel单元的掩埋隧穿结的直径均相等,取值范围为5-150μm。

14.进一步,所述衬底底部设有第一n型金属电极,位于最上层的vcsel单元顶部设有第二n型金属电极。

15.更进一步,各所述共用dbr顶部均设有共用电极,该共用电极包括下层vcsel单元的正电极和上层vcsel单元的负电极。

16.和现有技术相比,本发明产生的有益效果在于:本发明采用片内集成方式将至少两种不同中心波长的vcsel单元堆叠集成设计在同一颗vcsel芯片内,使得该vcsel芯片能够发射出至少两种不同的激光束,并突破性地采用共用dbr的设计构思,将位于下层的vcsel单元的顶部n型dbr与位于上层的vcsel单元的底部n型dbr设计为一体式的共用dbr,由此使得芯片的外延结构得到优化和改进,不仅降低了芯片生产难度,缩短了芯片制造周期,大大减少了芯片成本,而且降低了芯片的整体厚度,改善了芯片的散热性能,提高了芯片的工作稳定性和长期可靠性。相较于现有技术,本发明具有结构简单、集成度高、占用空间小、生产成本低、生产效率高和产品可靠性高等优点,具有明显的行业竞争优势。

附图说明

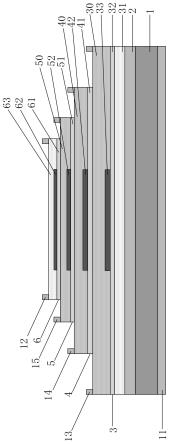

17.图1为本发明中片内集成式多波长激光器的结构示意图。

18.图2为本发明中不同材料的共用dbr的阻带范围示意图。

19.图中:1、衬底;2、gaas缓冲层;3、第一vcsel单元;31、第一底部n型dbr;32、第一有源区;33、第一掩埋隧穿结;30、第一共用dbr;4、第二vcsel单元;41、第二有源区;42、第二掩埋隧穿结;

40、第二共用dbr;5、第三vcsel单元;51、第三有源区;52、第三掩埋隧穿结;50、第三共用dbr;6、第四vcsel单元;61、第四有源区;62、第四掩埋隧穿结;63、第四顶部n型dbr;11、第一n型金属电极;12、第二n型金属电极;13、第一共用电极;14、第二共用电极;15、第三共用电极。

具体实施方式

20.下面参照附图说明本发明的具体实施方式。为了全面理解本发明,下面描述到许多细节,但对于本领域技术人员来说,无需这些细节也可实现本发明。

21.如图1所示,本发明提供一种共用dbr的多波长vcsel激光器芯片,包括衬底1以及自下而上堆叠于衬底表面的第一vcsel单元3、第二vcsel单元4、第三vcsel单元5和第四vcsel单元6。

22.如图1所示,第一vcsel单元3自下而上包括第一底部n型dbr31、第一有源区32、第一掩埋隧穿结33和第一顶部n型dbr;第二vcsel单元4自下而上包括第二底部n型dbr、第二有源区41、第二掩埋隧穿结42和第二顶部n型dbr;第三vcsel单元自下而上包括第三底部n型dbr、第三有源区51、第三掩埋隧穿结52和第三顶部n型dbr;第四vcsel单元自下而上包括第四底部n型dbr、第四有源区61、第四掩埋隧穿结62和第四顶部n型dbr63。

23.如图1所示,衬底1底部设有第一n型金属电极11,第四vcsel单元顶部6设有第二n型金属电极12,由此可同时点亮4个vcsel单元。为了实现分别调制,第一vcsel单元顶部3设有第一共用电极13,第二vcsel单元4顶部设有第二共用电极14,第三vcsel单元5顶部设有第三共用电极15;第一共用电极13、第二共用电极14和第三共用电极15均包括下层vcsel单元的正电极和上层vcsel单元的负电极。

24.如图1所示,本实施例中衬底1优选为gaas衬底,并且衬底1与第一vcsel单元3之间还设置有gaas缓冲层2。基于此,各vcsel单元的底部n型dbr和顶部n型dbr均是由al

x

ga

1-x

as/alyga

1-y

as材料周期堆叠组成的反射镜,各vcsel单元的有源层可设计为多个重叠设置的多量子阱层(mqw),且多量子阱层由gaas、algaas、gaasp和ingaas材料层叠排列而成。

25.如图1所示,第一至第四掩埋隧穿结的结构均相同,其由下至上包括p型重掺层和n型重掺层。其中,p型重掺层的材料包括但不限于ingaasp、ingaalas、alinas、gaas、algaas、gaassb,n型重掺层的材料包括但不限于algaas、gaas、gainas、inp;p型重掺层掺杂原子包括c、mg、zn或者be,n型重掺层掺杂原子包括se或者te;p型重掺层与n型重掺层掺杂浓度为

10

19-10

20

cm-3

数量级;p型重掺层厚度范围为8-50 nm,n型重掺层厚度范围为8-50 nm。第一至第四掩埋隧穿结的直径均相等,取值范围为5-150μm。

26.如图1所示,本发明中各掩埋隧穿结的作用包括:其一,通过掩埋隧穿结实现电流限制,从而克服了现有技术中采用氧化限制法所存在的生产良率低和产品一致性差等问题;其二,利用掩埋隧穿结反转了各vcsel单元中顶部n型dbr的极性,使其可替代顶部p型dbr,由此大大减少光损耗和串联电阻,有助于提高转换效率并实现高速运行;其三,用顶部n型dbr替代顶部p型dbr后,还能够克服顶部p型dbr因需要高c掺杂而引入的外延非均匀性,有效提高了外延均匀性和良率;其四,将顶部p型dbr替换为顶部n型dbr后,有利于将位于下层的vcsel单元的顶部n型dbr与位于上层的vcsel单元的底部n型dbr设计为一体式的共用dbr,为共用dbr的设计提供了必不可少的支持。

27.如图1所示,第一顶部n型dbr与第二底部n型dbr为一体式的第一共用dbr30,第二顶部n型dbr与第三底部n型dbr为一体式的第二共用dbr40,第三顶部n型dbr与第四底部n型dbr为一体式的第三共用dbr50。

28.如图1所示,本发明中共用dbr的作用包括:其一,设置共用dbr省去了上下相邻的两个vcsel单元之间的一个n型dbr反射镜,大大减少了各vcsel单元的结构材料成本、外延生长工艺成本和芯片制造工艺成本;其二,通过设置共用dbr使得多波长vcsel激光器芯片的结构得到了进一步的简化,不仅可以大大缩短芯片的生产制造工艺难度,提高生产良率,还可以大大缩短芯片的生产制造周期,整体行业竞争优势明显;其三,设置共用dbr能够大大缩减多波长vcsel激光器芯片的整体厚度,由此提高了芯片的散热性,并同步提高芯片的工作稳定性和长期可靠性。

29.如图1所示,作为优选方案:本实施例中第一底部n型dbr31、第四顶部n型dbr63、第一至第三共用dbr均是由al

x

ga

1-x

as/alyga

1-y

as材料周期堆叠组成的反射镜,并且周期数为20-70,由此可确保各反射镜的反射率均大于99%。为了确保激光器向上出光,还需保证位于下层的反射镜的反射率应大于位于上层的反射镜的反射率,因此第一底部n型dbr31、第一共用dbr30、第二共用dbr40、第三共用dbr50和第四顶部n型dbr63的周期数应逐渐递减。

30.如图1所示,本发明的设计初衷在于将4种不同中心波长的vcsel单元堆叠集成设计在同一颗vcsel芯片内,使得该vcsel芯片能够发射出4种不同的激光束,由于长波长材料对应的能带带隙比短波长材料对应的能带带隙小,因此短波长激光会被长波长材料部分吸收。基于此,本发明的设计原则为:位于下一层的vcsel单元的中心波长必须大于位于上一层的vcsel单元的中心波长,以避免短波长激光沿着激光发射方向被长波长材料的吸收,因此,第一至第四vcsel单元的中心波长的大小关系为: 。

31.共用dbr的作用是作为反射镜,同时服务于上下相邻的两个vcsel单元,因此对上下相邻的两个vcsel单元都必须有足够的反射率(一般99%以上)。但是共用dbr对于不同波长的激光的反射率是不一样的,并且芯片工作时会发热,有温漂,可能会引起中心波长的左右偏移,因此为了确保共用dbr同时为上下相邻的两个vcsel单元的提供足够的反射率,必须确保与共用dbr相邻的上下两个vcsel单元的中心波长均位于该共用dbr的阻带范围内,即第一vcsel单元3的中心波长 和第二vcsel单元4的中心波长 均位于第一共用dbr30的阻带范围内,第二vcsel单元4的中心波长和第三vcsel单元5的中心波长均位于第二共用dbr40的阻带范围内,第三vcsel单元5的中心波长和第四vcsel单元6的中心波长

均位于第三共用dbr50的阻带范围内。

32.具体地,第一共用dbr30、第一共用dbr40和第三共用dbr50的阻带宽度的计算公式为:式中: 为阻带宽度; 为折射率差值; 为位于下层的vcsel单元的中心波长; 为有效折射率。

33.则共用dbr的阻带范围为 。

34.由公式(1)可知,共用dbr的阻带宽度取决于位于下层的vcsel单元的中心波长以及al

x

ga

1-x

as与alyga

1-y

as两种材料的折射率差 。

35.关于位于下层的vcsel单元的中心波长,根据实际需求,我们设定第一至第四vcsel单元的中心波长的取值范围均为600-2000nm。

36.关于折射率差 ,其主要影响因素为组成共用dbr的两种材料al

x

ga

1-x

as/alyga

1-y

as。经过反复试验后我们得出以下结论,当x的取值范围为0.8-1,y的取值范围为0-0.2时,能够确保共用dbr的上下两个vcsel单元的中心波长均位于该共用dbr的阻带范围内。

37.作为一个具体的实施方案:我们设定其中某一共用dbr的周期数为40,位于该共用dbr下层的vcsel单元的中心波长=850nm,那么当x和y的取值不同时,共用dbr的阻带宽度和阻带范围也有所不同,如表1及图2所示。

38.表1 不同材料的共用dbr阻带宽度变化表假设经过仿真试验后,我们确认x=0.87,y=0.06为最优取值,那么位于该共用dbr上层的vcsel单元的中心波长的取值范围应在813.5-886.5nm之间。由于要遵循

ꢀ“

位于下层的vcsel单元的中心波长大于位于上层的vcsel单元的中心波长”这一设计原则,因此位于该共用dbr上层的vcsel单元的中心波长的取值范围应进一步控制在813.5-850nm之间。以此类推进行反复试验,便可得出多波长vcsel激光器芯片的全部设计参数。

39.可见,实际应用中,多波长vcsel激光器芯片的相关设计参数的计算流程为:1、首先根据多波长vcsel激光器芯片的实际波长需求,初步确认某一vcsel单元的中心波长;2、通过调节与该vcsel单元相邻的某一共用dbr的al

x

ga

1-x

as/alyga

1-y

as材料的x和y取值,从而确认该共用dbr的折射率差 ;3、利用公式(1)求取该共用dbr的阻带宽度和阻带范围,并通过微调x、y的取值以及该共用dbr的上下两个vcsel单元的中心波长,由此进行设计仿真和反复试验,从而确保上下两个vcsel单元的中心波长均位于该共用dbr的阻带范围内;

4、重复上述步骤直至求解出该多波长vcsel激光器芯片的所有vcsel单元的中心波长及所有共用dbr的al

x

ga

1-x

as/alyga

1-y

as材料的x和y取值。

40.需要说明的是,在实际开发和应用中,除了采用gaas材料体系外,本发明的共用dbr的设计构思同样适用于inp材料体系等。例如,当衬底设计为inp衬底时,位于最下层的vcsel单元的底部n型dbr、位于最上层的vcsel单元的顶部n型dbr以及各共用dbr均采用由in

0.52

aliga

0.48-i

as/in

0.52

aljga

0.48-j

as或者in

0.52

alkga

0.48-k

as/inp材料周期堆叠组成的反射镜,并且周期数均为20-70。我们经过仿真试验证明,基于inp材料体系时,各共用dbr的in

0.52

aliga

0.48-i

as/in

0.52

aljga

0.48-j

as材料或in

0.52

alkga

0.48-k

as/inp材料中,i、j和k的取值范围均为0-0.48,由此能够确保共用dbr的上下两个vcsel单元的中心波长均位于该共用dbr的阻带范围内。

41.综上可知,本实施例将4种不同中心波长的vcsel单元堆叠集成设计在同一颗vcsel芯片内,使得该vcsel芯片能够发射出4种不同的激光束,并突破性地采用共用dbr的设计构思,将位于下层的vcsel单元的顶部n型dbr与位于上层的vcsel单元的底部n型dbr设计为一体式的共用dbr,由此使得芯片的外延结构得到优化和改进,不仅降低了芯片生产难度,缩短了芯片制造周期,大大减少了芯片成本,而且降低了芯片的整体厚度,改善了芯片的散热性能,提高了芯片的工作稳定性和长期可靠性。相较于现有技术,本实施例具有结构简单、集成度高、占用空间小、生产成本低、生产效率高和产品可靠性高等优点,具有明显的行业竞争优势。

42.上述仅为本发明的具体实施方式,但本发明的设计构思并不局限于此。凡是利用本发明的设计构思对本发明进行非实质性的改动,均应属于侵犯本发明保护范围的行为。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1