一种扇出型多芯片三维集成光敏系统封装方法及结构与流程

1.本发明涉及集成电路封装技术领域,特别涉及一种扇出型多芯片三维集成光敏系统封装方法及结构。

背景技术:

2.环境光传感器可集成在很多电子产品中以提供环境光感测的功能。消费电子市场近年来发展迅速,为用户提供更好的感官体验,成为消费电子发展的趋势之一。环境光传感器在消费电子上的应用就是提高用户视觉体验的一个举措,已日趋成熟,应用于智能手机、平板电脑、游戏机等的环境光传感器通过感测人眼可见光的强度来调整显示设备亮度,在提高用户视觉体验的同时还节省了功耗。目前环境光传感器也被用于汽车电子,医疗电子及航天航空等诸多领域。

3.在芯片的封装上,由于光敏传感器芯片结构布局比常规芯片多了光感窗口,且光电传感区域与信号pad分布在同一面,从而在很大程度上限制了后期的封装设计布局。光感窗口不能遮挡,传统的封装方式是芯片正贴在基板上,通过打线完成与基板的互连,这种封装方式体积大,引线外漏可靠性低,结构设计受限。

4.在多芯片的小型化高密度封装集成上,光敏传感器芯片的集成成为棘手难题,为此,亟需一种新型的扇出型多芯片三维集成光敏系统封装方法,以有效解决上述问题。

技术实现要素:

5.本发明的目的在于提供一种扇出型多芯片三维集成光敏系统封装方法及结构,以解决背景技术中的问题。

6.为解决上述技术问题,本发明提供了一种扇出型多芯片三维集成光敏系统封装方法,包括如下步骤:

7.提供硅晶圆,在其第一面刻蚀盲孔,并电镀填孔形成tsv铜柱;

8.在硅晶圆的第一面刻蚀出芯片腔,并装入光敏传感器芯片;

9.减薄硅晶圆的第二面至露出tsv铜柱;

10.在硅晶圆的第二面,将tsv转接芯片与tsv铜柱对位倒装焊接,并进行底填,在硅晶圆上贴装异构芯片;

11.用树脂塑封料将异构芯片和tsv转接芯片进行灌封固化形成硅-树脂多层重构晶圆;

12.对硅-树脂多层重构晶圆进行减薄,露出tsv转接芯片的铜柱和异构芯片的铜柱;

13.使用晶圆级多层再布线工艺在减薄后的表面形成多层再布线;

14.将带有再布线的玻璃基板与光敏传感器芯片和tsv铜柱进行回流键合,并做底填;

15.最后,在多层再布线处形成焊球,再进行划片形成最终的封装体。

16.在一种实施方式中,所述芯片腔的腔内涂覆有导热胶,所述光敏传感器芯片通过装片机装入腔内与所述导热胶粘贴,并且所述光敏传感器芯片的凸点朝外。

17.在一种实施方式中,所述光敏传感器芯片的衬底材料包括si、gaas、gan、sic;

18.所述光敏传感器芯片、所述异构芯片和所述tsv转接芯片生长有凸点,其材料包括cu、cusn、cunisn、cunisnag、snpb和snagcu中的一种。

19.在一种实施方式中,所述异构芯片通过导热胶贴装在所述硅晶圆上。

20.在一种实施方式中,所述tsv转接芯片与所述tsv铜柱的倒装焊接方式包括回流焊和热压焊;

21.所述底填的方式包括压干膜工艺和点胶工艺,通过底填胶将倒装焊接的凸点之间的缝隙填实。

22.在一种实施方式中,所述树脂塑封料的厚度大于所述异构芯片和所述tsv转接芯片的厚度。

23.在一种实施方式中,所述晶圆级多层再布线工艺为金属层和钝化层多次交叠的布线工艺,所述多层再布线的层数最少包括1层金属层和1层钝化层;所述钝化层的厚度大于所述金属层,且所述钝化层包覆所述金属层。

24.在一种实施方式中,所述金属层的厚度不小于1μm,所述钝化层厚度不小于3μm。

25.在一种实施方式中,形成焊球的工艺包括晶圆级植球、单芯片植球和印刷锡膏;所述焊球的成分为snpb或snagcu。

26.本发明还提供了一种扇出型多芯片三维集成光敏系统封装结构,包括:

27.硅晶圆,所述硅晶圆的第一面设有tsv铜柱和芯片腔,所述芯片腔中装有光敏传感器芯片,所述tsv铜柱贯穿所述硅晶圆;

28.玻璃基板,所述玻璃基板带有再布线,与所述光敏传感器芯片和所述tsv铜柱键合;

29.异构芯片和tsv转接芯片,所述异构芯片贴装于所述硅晶圆的第二面,所述tsv转接芯片与所述tsv铜柱倒装焊接;

30.树脂塑封料,包覆所述异构芯片和所述tsv转接芯片,并露出其铜柱;所述树脂塑封料的表面形成有多层再布线,所述多层再布线上形成有焊球。

31.本发明提供的一种扇出型多芯片三维集成光敏系统封装方法及结构,具有以下有益效果:

32.(1)在晶圆级封装的基础上,完成多芯片的封装,实现了晶圆级封装与系统级封装的相互结合,实用性更强;

33.(2)相对于传统的光敏芯片打线键合,该封装结构采用倒装方式,尺寸更小,可靠性更高;

34.(3)基于晶圆级扇出的封装形式,其生产效率更高,成本优势更大,应用更广。

附图说明

35.图1是在硅晶圆中形成tsv铜柱的结构示意图。

36.图2是在硅晶圆中刻蚀出芯片腔的结构示意图。

37.图3是在芯片腔中装入光敏传感器芯片的结构示意图。

38.图4是减薄硅晶圆至露出tsv铜柱的结构示意图。

39.图5是贴装tsv转接芯片和异构芯片的结构示意图。

40.图6是用树脂塑封料包覆异构芯片和tsv转接芯片的结构示意图。

41.图7是减薄至露出tsv转接芯片的铜柱和异构芯片的铜柱的结构示意图。

42.图8是在减薄后的表面上形成多层再布线的结构示意图。

43.图9是玻璃基板与光敏传感器芯片和tsv铜柱进行键合的结构示意图。

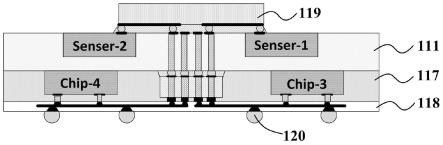

44.图10是在多层再布线处形成焊球再进行划片形成最终的封装体的结构示意图。

具体实施方式

45.以下结合附图和具体实施例对本发明提出的一种扇出型多芯片三维集成光敏系统封装方法及结构作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

46.本发明提供了一种扇出型多芯片三维集成光敏系统封装方法及结构,包括如下步骤:

47.如图1所示,在硅晶圆111的正面刻蚀盲孔,在盲孔内电镀填孔并长出一定高度的铜柱,制成tsv铜柱112;

48.如图2所示,在所述硅晶圆111上刻蚀出芯片腔113,所述芯片腔113与所述tsv铜柱112位于所述硅晶圆111的同一侧;在所述芯片腔113内涂覆导热胶(图中未示出);

49.如图3所示,将长好凸点的光敏传感器芯片114(即图3中的senser-1和senser-2)通过装片机装入所述芯片腔113内,并与所述芯片腔113内部的导热胶粘贴;所述光敏传感器芯片114的衬底材料为si、gaas、gan、sic中的一种;

50.如图4所示,将所述硅晶圆111的背面减薄至露出所述tsv铜柱112;

51.如图5所示,将长好凸点的tsv转接芯片115通过装片机在所述硅晶圆111的背面与所述tsv铜柱112精准对位放置后回流,并做底填,然后通过装片机贴装长好凸点的异构芯片116(即图5中的chip-3和chip-4)到所述硅晶圆111的背面;其中所述光敏传感器芯片114、所述异构芯片116和所述tsv转接芯片115生长有凸点,其材料为cu、cusn、cunisn、cunisnag、snpb和snagcu中的一种;

52.如图6所示,利用晶圆级塑封工艺,用树脂塑封料117将贴装在所述硅晶圆111上的异构芯片116和tsv转接芯片115进行灌封固化,形成硅-树脂多层重构晶圆;

53.如图7所示,将硅-树脂多层重构晶圆进行树脂减薄,露出所述tsv转接芯片115的铜柱和所述异构芯片116的铜柱;

54.如图8所示,使用晶圆级再布线工艺在减薄后的表面上形成多层再布线118;

55.如图9所示,将带有再布线的玻璃基板119与所述硅晶圆111正面的光敏传感器芯片114和tsv铜柱112进行回流键合,并做底填;

56.最后如图10所示,在所述多层再布线118处形成焊球120,再进行划片形成最终的封装体;其中所述焊球120的成分为snpb或snagcu。

57.通过上述方法制备出的扇出型多芯片三维集成光敏系统封装结构,如图10所示,包括硅晶圆111、tsv铜柱112、光敏传感器芯片114、tsv转接芯片115、异构芯片116、树脂塑封料117、多层再布线118、玻璃基板119和焊球120。所述tsv铜柱112位于所述硅晶圆111中,并贯穿所述硅晶圆111;所述光敏传感器芯片114通过导热胶粘贴在所述硅晶圆111第一面

的芯片腔中;所述玻璃基板119带有再布线,与所述光敏传感器芯片114和所述tsv铜柱112键合;所述异构芯片116贴装在所述硅晶圆111第二面的外表面,所述tsv转接芯片115与所述tsv铜柱对位倒装焊接;所述树脂塑封料117包覆所述tsv转接芯片115和所述异构芯片116,并露出所述tsv转接芯片115的铜柱和所述异构芯片116的铜柱;所述多层再布线118形成于所述树脂塑封料117的表面,所述焊球120形成于所述多层再布线118上。

58.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1