栅极阵列结构一体化器件及其制备方法

1.本发明属于半导体器件技术领域,具体涉及一种栅极阵列结构一体化器件及其制备方法。

背景技术:

2.天线作为接收和发射电磁波信号的元器件,是手机等一些终端设备的核心配件;其中,5g作为新一代通信技术,随着频段的增多,带来了许多技术和标准的革新,使天线的设计和制造增加了难度,进一步使天线向复杂度和集成化高的方向发展。

3.现有技术中,随着射频前端开关电路复杂度的提升,以及面积增大,隔离度和插入损耗会有一定程度的恶化;同时,器件沟道载流子迁移率的退化也使射频前端器件的线性度恶化。

4.因此,亟需解决现有技术中开关功放端器件数量多,面积大,开关速度慢,信号线性度恶化的问题。

技术实现要素:

5.为了解决现有技术中存在的上述问题,本发明提供了一种栅极阵列结构一体化器件及其制备方法。本发明要解决的技术问题通过以下技术方案实现:

6.第一方面,本技术提供一种栅极阵列结构一体化器件,包括:

7.衬底;

8.缓冲层,位于衬底的一侧;

9.沟道层,位于缓冲层背离衬底的一侧;

10.势垒层,位于沟道层背离衬底的一侧;

11.钝化层,位于势垒层背离衬底的一侧;

12.第一沟槽,沿垂直于衬底的方向贯穿钝化层和势垒层,以及至少部分沟道层;

13.第二沟槽,沿垂直于衬底的方向贯穿钝化层和势垒层;第二沟槽位于第一沟槽之间,且第一沟槽和第二沟槽连通;

14.第一栅极,位于缓冲层背离衬底的一侧,第一栅极为射频栅;第一栅极包括第一支部和第二支部,第一支部位于沟道层的第一沟槽内,第二支部位于第二沟槽内,第一支部和第二支部形成阵列结构;

15.第二栅极,位于所述势垒层背离所述衬底的一侧,所述第二栅极为直流栅;所述第二栅极沿第一方向延伸,且所述第二栅极与所述第一栅极沿第二方向间隔排布;所述第二栅极包括第三支部和第四支部,所述第三支部位于第三沟槽,所述第四支部覆盖于所述第三支部上;所述第一方向与所述第二方向相交。

16.第二方面,本技术还提供一种栅极阵列结构一体化器件的制备方法,应用于本技术提供的栅极阵列结构一体化器件,该方法包括:

17.提供一衬底;

18.在衬底上依次制作缓冲层、沟道层、势垒层和钝化层;

19.在钝化层和势垒层上刻蚀沟槽,并制作源极和漏极;

20.在钝化层上刻蚀第一沟槽和第二沟槽,并在第一沟槽制作第一栅极的第一支部,在第二沟槽内制作第一栅极的第二支部。

21.本发明的有益效果:

22.本发明提供的一种栅极阵列结构一体化器件及其制备方法,一方面,将第一栅极和第二栅极集成在同一器件,即将射频开关和功率放大器(power amplifier,pa)通过双栅极结构集成在同一器件上;第一栅极为射频栅,采用阵列结构,起到功放作用,第二栅极为直流栅,采用t型或i型结构,其结构包括栅和栅帽,起到开关作用;将射频开关和功率放大器集成在同一器件上,能够减少射频前端器件的数量,减少芯片面积,提升开关速度;此外,相对于单个开关器件,一体化器件的隔离度等性能也非常优异。另一方面,将射频栅设置为阵列结构,在保证良好的开关特性和功放特性的基础上,由于侧墙栅对于沟道处载流子的栅控附加作用,能抑制因器件沟道载流子迁移率退化所引起的漏极电流密度随着栅极电压的线性增加而非线性增加的行为,从而提高跨导线性度,放大器的频率参数的线性度也随之得到极大改善;此外,因为大规模天线的通道数非常多,双栅结构的一体化器件能够很大程度地减少射频前端器件的数量,能够有效减少射频前端的芯片面积,并且射频开关的隔离度得到了很大的提高。

附图说明

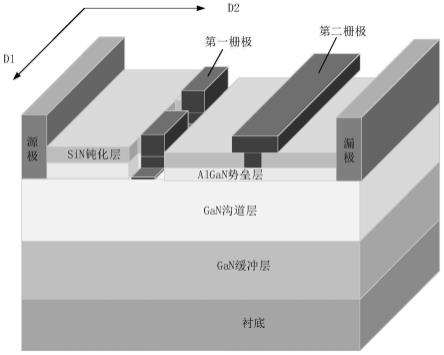

23.图1是本发明实施例提供的栅极阵列结构一体化器件的一种结构示意图;

24.图2是本发明实施例提供的栅极阵列结构一体化器件的另一种结构示意图;

25.图3是本发明实施例提供的栅极阵列结构一体化器件的另一种结构示意图;

26.图4是本发明实施例提供的栅极阵列结构一体化器件信号处理的一种示意图;

27.图5是本发明实施例提供的制备栅极阵列结构一体化器件的一种流程图;

28.图6是本发明实施例提供的制备过程的一种结构示意图;

29.图7是本发明实施例提供的制备过程的另一种结构示意图。

具体实施方式

30.下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

31.相关技术中,大规模天线技术均使用大量的射频开关,其中,射频开关在电路中实现控制微波信号通道转换的作用,在射频收发前端扮演重要的角色。射频收发前端的结构基本是通过射频开关将功率放大器和低噪声放大器连接,射频开关的隔离度、插入损耗和线性度等性能指标决定射频接受信号的效果,射频开关的发展在一定程度上映射了射频集成电路的发展。

32.从工作原理上分类,射频微波开关可分为机电开关和固态开关,机电开关是通过机械接触触发开关性能;固态开关包括两大类,分别为场效应晶体管(field effect transistor,fet)和pin二极管,fet开关是形成一个通道,让电流从fet的漏极流向源极,以此形成开通状态;pin二极管则是在高掺杂的正极性和负极性电荷材料之间,插入高阻性介

质层,来组成开关状态。现有研究中,因为gan hemt的优越性,其被广泛运用于射频器件制造中。2007年mark yu等人首次报道了在硅衬底上使用algan/gan异质结构场效应晶体管开发的高功率单刀四掷混合开关;2008年jim m.carroll将氮化镓场效应晶体管用于大功率射频开关;2018年corrado florian描述了射频gan-on-sic hemt开关由于电荷俘获而导致的性能下降是由工作状态下的高电压触发的;2019年sinan osmanoglu在x波段描述了三种不同拓扑结构的基于高功率、低损耗和高隔离gan hemt的单刀双掷射频开关,并将它们做了对比分析。

33.通常情况下,射频开关通常与功率放大器连接,对于功放器件的研究也得到许多开展,特别是器件的线性度方面;2006年roberto pena等人于集成非线性微波和毫米波电路国际研讨会上提出在蓝宝石衬底上生长的实验性gan hemt用于电阻混频器的设计和测试,选择栅极至源极偏置电压以优化转换损耗,使用较小的漏极至源极偏置值有助于提高其线性度;2016年dragan gecan在24届电信论坛上提到使用动态栅极偏置操作来设计功率放大器使pa性能的线性度显著提高;近年来,从事半导体器件研究的人员对阵列结构与线性度关系进行了大量研究,阵列结构广泛运用在集成电路生产当中;阵列场效应晶体管器件相比传统的平面晶体管来说有明显优势。由此可见,阵列场效应晶体管的沟道大多是轻掺杂的,可以避免离散的掺杂原子引起散射,载流子迁移率会提高,不仅如此,与传统的平面cmos相比,阵列场效应晶体管器件可以有效地抑制亚阈值电流和栅极漏电流。

34.有鉴于此,本技术提供一种栅极阵列结构一体化器件,基于氮化镓高电子迁移率场效应晶体管(gan hemt),采用双栅的结构制备多功能可调节的一体化器件,且将射频栅设置为阵列结构,使信号线性度得到明显优化。

35.请参见图1~3,图1是本发明实施例提供的栅极阵列结构一体化器件的一种结构示意图,图2是本发明实施例提供的栅极阵列结构一体化器件的另一种结构示意图,图3是本发明实施例提供的栅极阵列结构一体化器件的另一种结构示意图,本技术所提供的一种栅极阵列结构一体化器件,包括:

36.衬底;

37.缓冲层,位于衬底的一侧;

38.沟道层,位于缓冲层背离衬底的一侧;

39.势垒层,位于沟道层背离衬底的一侧;

40.钝化层,位于势垒层背离衬底的一侧;

41.第一沟槽,沿垂直于衬底的方向贯穿钝化层和势垒层,以及至少部分沟道层;

42.第二沟槽,沿垂直于衬底的方向贯穿钝化层和势垒层;第二沟槽位于第一沟槽之间,且第一沟槽和第二沟槽连通;

43.第一栅极,位于缓冲层背离衬底的一侧,第一栅极为射频栅;第一栅极包括第一支部和第二支部,第一支部位于沟道层的第一沟槽内,第二支部位于第二沟槽内,第一支部和第二支部形成阵列结构;

44.第二栅极,位于所述势垒层背离所述衬底的一侧,所述第二栅极为直流栅;所述第二栅极沿第一方向d1延伸,且所述第二栅极与所述第一栅极沿第二方向d2间隔排布;所述第二栅极包括第三支部和第四支部,所述第三支部位于第三沟槽,所述第四支部覆盖于所述第三支部上;所述第一方向d1与所述第二方向d2相交。

45.具体而言,请继续参考图1~图3,本实施例中提供的一种栅极阵列结构一体化器件,依次设置有衬底、缓冲层、沟道层、势垒层和钝化层,在缓冲层背离衬底的一侧设置有第一栅极,第一栅极即为射频栅,第一栅极部分位于沟道层,部分位于势垒层和钝化层,且第一栅极为阵列结构,其第一支部和第二支部交替排布,第一支部位于沟道层,第二支部位于势垒层和钝化层,沿垂直于衬底的方向,第一支部与第二支部无交叠区域;在势垒层背离衬底的一侧设置有第二栅极,第二栅极为直流栅,第一栅极与第二栅极间隔排布,第二栅极包括第三支部和第四支部,第三支部位于第三沟槽,第四支部覆盖在第三支部上;第一方向d1与第二方向d2相交,可选地,第一方向d1与第二方向d2垂直。本实施例中,一方面,将第一栅极和第二栅极集成在同一器件,即将射频开关和功率放大器(power amplifier,pa)通过双栅极结构集成在同一器件上;第一栅极为射频栅,采用阵列结构,起到功放作用,第二栅极为直流栅,采用t型或i型结构,其结构包括栅和栅帽,起到开关作用;将射频开关和功率放大器集成在同一器件上,能够减少射频前端器件的数量,减少芯片面积,提升开关速度;此外,相对于单个开关器件,一体化器件的隔离度等性能也非常优异。另一方面,将射频栅设置为阵列结构,在保证良好的开关特性和功放特性的基础上,由于侧墙栅对于沟道处载流子的栅控附加作用,能抑制因器件沟道载流子迁移率退化所引起的漏极电流密度随着栅极电压的线性增加而非线性增加的行为,从而提高跨导线性度,放大器的频率参数的线性度也随之得到极大改善;此外,因为大规模天线的通道数非常多,双栅结构的一体化器件能够很大程度地减少射频前端器件的数量,能够有效减少射频前端的芯片面积,并且射频开关的隔离度得到了很大的提高。

46.在本技术的一种可选地实施例中,当发射端处于阻断状态,在直流栅上施加一个负值较大的电压vg2,耗尽载流子使沟道夹断,天线中的信号无法通过功率放大器,从而起到关闭功能;当发射端处于导通状态,一体化器件在充当射频开关的同时,也作为功率放大器进行工作。向一体化器件中的射频栅上施加电压vg1用来输入射频信号,射频栅可于电路的两侧控制电路的接通与断开,同时直流栅上施加正向电压vg2,用来控制沟道开启与关闭;改变直流栅的正向电压vg2的大小,以此控制沟道开启程度,使放大程度改变,信号增益不同;信号经过一体化器件的放大功能后可以直接传导到天线处发射。

47.需要说明的是,图1所示实施例仅示意性示出了器件中各膜层的位置关系,并不代表实际尺寸,其中,第一沟槽和第二沟槽的尺寸也并不代表实际,在制作过程中可以调整其尺寸;图2所示实施例仅示意性示出了第一栅极的位置示意图,并不代表其实际尺寸;图3所示实施例仅示意性示出了第一栅极的位置示意图,并不代表其实际尺寸。

48.需要说明的是,请参见图4,图4是本发明实施例提供的栅极阵列结构一体化器件信号处理的一种示意图,采用本实施例提供的一体化器件,将射频开关和功率放大器通过双栅极结构集成在同一器件上,输入端pin输入一信号,该信号仅包括一种幅值,经过一体化器件的处理,在输出端pout输出一信号,该信号包括多个幅值;如此,采用本实施例提供的一体化器件,可实现增益可调。

49.请继续参见图1~图3所示,在本技术的一种可选地实施例中,第一支部与第二支部沿第一方向d1交替排布。

50.具体而言,请继续参见图1~图3所示,本实施例中的第一支部于第二支部沿第一方向d1交替排布,形成阵列结构的第一栅极,进一步形成高线性一体化器件的功率放大器,

使用阵列结构的射频栅,在保证良好的开关特性和功放特性的基础上,由于侧墙栅对于沟道处载流子的栅控附加作用,使功放频率参数的线性度也因此得到改善。

51.在本技术的一种可选地实施例中,沿垂直于衬底的方向,第三支部在衬底上的正投影与第四支部在衬底上的正投影重叠。

52.具体而言,本实施例提供的第二栅极为i型栅,能够有效减小一体化器件的寄生电容,提高隔离度。

53.请继续参见图1~图3所示,在本技术的一种可选地实施例中,沿垂直于衬底的方向,第三支部在衬底上的正投影位于第四支部在衬底上的正投影。

54.具体而言,请继续参见图1~图3所示,本实施例提供的第二栅极为t型栅,在直流栅上施加大于阈值电压的电压,随着施加的电压不同,异质结界面处,即势垒层与沟道层交界处二维电子气层的能带弯曲不同,势阱深度改变,使沟道二维电子气浓度改变,从射频栅进来的信号经过二维电子气层电流放大的程度也不一样。

55.在本技术的一种可选地实施例中,位于沟道层的第一沟槽沿垂直于衬底的方向的深度小于20nm。

56.具体而言,本实施例中提供地第一沟槽至少部分位于沟道层,且位于沟道层的深度小于20nm,能够保证第一栅极的阵列结构实现良好的功能。

57.请继续参见图1~图3所示,在本技术的一种可选地实施例中,还包括:源极和漏极,均位于沟槽层背离衬底的一侧,源极与漏极间隔排布,且第一栅极和第二栅极位于源极和漏极之间。

58.基于同一发明构思,请参见图5,图5是本发明实施例提供的制备栅极阵列结构一体化器件的一种流程图,本技术还提供一种栅极阵列结构一体化器件的制备方法,应用于本技术上述实施例提供的栅极阵列结构一体化器件,一体化器件的实施例可参考上述,在此不再赘述,该方法包括:

59.提供一衬底;

60.在衬底上依次制作缓冲层、沟道层、势垒层和钝化层;

61.在钝化层和势垒层上刻蚀沟槽,并制作源极和漏极;

62.在钝化层上刻蚀第一沟槽和第二沟槽,并在第一沟槽制作第一栅极的第一支部,在第二沟槽内制作第一栅极的第二支部。

63.具体而言,图6是本发明实施例提供的制备过程的一种结构示意图,图7是本发明实施例提供的制备过程的另一种结构示意图,请继续参见图5所示,并结合图6和图7所示,本实施例中采用以下步骤实现一体化器件的制备。

64.s101、提供一sic衬底。

65.s102、在衬底上依次制作buffer层/gan沟道层/algan势垒层。

66.s103、在algan势垒层上进行源极和漏极欧姆金属制备。

67.s104、在algan势垒层上通过pecvd进行sin钝化层生长。

68.s105、进行阵列结构射频栅制备,使用ebl电子束光刻机,对钝化层sin部分进行光刻曝光,使用icp刻蚀设备在钝化层sin表面进行f基刻蚀,请参见图6所示,刻蚀深度为sin钝化层的厚度;然后使用ebl电子束光刻机,对algan层部分进行光刻曝光;再使用icp刻蚀设备进行cl基刻蚀,请参见图7所示,刻蚀至algan势垒层和gan沟道层异质结界面下方

10nm;再使用stepper光刻机,光刻工艺进行双层胶工艺,光刻出栅图形,最后射频栅金属蒸发,形成射频栅。

69.s106、进行直流栅制备,先进行直流栅凹槽制备,使用stepper光刻机,光刻工艺使用epi621光刻胶,凹槽刻蚀,在钝化层sin使用icp刻蚀设备进行f基刻蚀;然后进行直流栅栅帽制备,光刻工艺使用双层胶,光刻出栅图形,最后直流栅金属蒸发。

70.s107、进行金属互联和空气桥制备,形成栅极阵列结构一体化器件。

71.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1