BCD工艺中可自由调控击穿电压的齐纳二极管的制作方法

bcd工艺中可自由调控击穿电压的齐纳二极管

技术领域

1.本技术涉及半导体技术领域,具体涉及一种bcd工艺中可自由调控击穿电压的齐纳二极管。

背景技术:

2.齐纳二极管(zener diode)是利用其雪崩击穿效应的面接触型晶体二极管,也叫稳压二极管。齐纳二极管是利用pn结工作在反向击穿状态时,击穿电压附近的电流变化很大,电压变化却很小的原理。它是一种直到临界反向击穿电压前都具有很高电阻的半导体器件。在反向击穿时,在一定的电流范围内(或者说在一定功率损耗范围内)端电压几乎不变,表现出稳压特性。齐纳二极管的反向电压增加到某个特殊值,对于一个微小偏压的变化,就会使电流产生一个可观的增加。在这临界击穿点上,反向电阻降低到一个很小的数值,在这个低阻区中电流增加而电压则保持恒定。引起这种效应的电压称为“击穿”电压或“齐纳”电压,广泛应用于稳压电源与限幅电路之中。

3.齐纳二极管在稳压电源中广泛应用于基准电压源或在过电保护电路中作为保护二极管,在低压电路中常常用作电压调节器。同时也用作浪涌保护、过压保护、电弧抑制、串联型稳压,能用在抑制瞬态干扰与抑制极高速度脉冲干扰的场合。齐纳二极管还广泛应用于led发光二极管上,如在制作大功率led时可以并联一个齐纳二极管抗esd,或串联一个齐纳二极管帮助稳压,避免led元件被电流破坏。

4.bcd工艺是一种可以将双极晶体管、cmos和dmos器件同时集成到单芯片上的技术,其基本工序标准化,混合工艺由这些基本工序组合而成,本领域普通技术人员可以根据实际需要增减相应的工艺步骤。

5.在bcd工艺中,可以通过开关型n型横向扩散金属氧化物半导体(switch nldmos,snldmos)器件的p型体区(p-body)结构来制作纵向齐纳二极管。

6.由于p型体区结构同时用于制作snldmos以及其它ldmos的源区,所以通过改变p型体区结构的注入参数来调整齐纳二极管的击穿电压,同样影响到ldmos器件的性能,例如击穿电压(bv)、导通电阻(rsp)等。

技术实现要素:

7.鉴于以上所述现有技术的缺点,本技术的目的在于提供一种bcd工艺中可自由调控击穿电压的齐纳二极管,包括:

8.n型埋层和p型埋层,位于p型衬底中,p型衬底上形成有p型外延层;

9.p阱和n阱,位于n型埋层之上、p型外延层之中,p阱底部和n阱底部与n型埋层相接触;

10.多个隔离部件,分布于p型外延层的表面;

11.三个p型体区,位于p阱中,其中,位于中间的p型体区中形成有第一n+注入区,位于左右两侧的p型体区中形成有第一p+注入区;

12.栅极结构,位于p阱的表面上;

13.第二n+注入区,位于n阱中;

14.第二p+注入区,位于p型埋层之上、p型外延层之中。

15.优选的,第一n+注入区和位于中间的p型体区构成纵向齐纳二极管。

16.优选的,通过增加第一p+注入区的注入类型或者调整栅极结构的特征尺寸来调控齐纳二极管的击穿电压。

17.优选的,增加第一p+注入区的注入类型包括增加5v p型轻掺杂漏。

18.优选的,增加5v p型轻掺杂漏的工艺参数:注入能量10kev-30kev,注入剂量1e13cm-2-1e14cm-2

。

19.优选的,通过减小所述栅极结构的宽度来降低所述齐纳二极管的击穿电压。

20.优选的,三个p型体区的注入参数相同。

21.另一方面,本技术还提供一种bcd工艺中可自由调控击穿电压的齐纳二极管,包括:

22.n型埋层和p型埋层,位于p型衬底中,p型衬底上形成有p型外延层;

23.p阱和n阱,位于n型埋层之上、p型外延层之中,p阱底部和n阱底部与n型埋层相接触;

24.多个隔离部件,分布于p型外延层的表面;

25.两个p型体区,位于p阱中,其中,两个p型体区之间的p阱中形成有第一n+注入区,两个p型体区中形成有第一p+注入区;

26.栅极结构,位于p阱的表面上;

27.第二n+注入区,位于n阱中;

28.第二p+注入区,位于p型埋层之上、p型外延层之中。

29.优选的,第一n+注入区与p型体区以及第一p+注入区构成横向齐纳二极管。

30.优选的,通过调整栅极结构的特征尺寸来调控齐纳二极管的击穿电压。

31.优选的,通过增大所述栅极结构的宽度来升高所述齐纳二极管的击穿电压。

32.优选的,两个p型体区的注入参数相同。

33.如上所述,本技术提供的bcd工艺中可自由调控击穿电压的齐纳二极管,具有以下有益效果:通过增加第一p+注入区的注入类型或者调整栅极结构的特征尺寸来调控齐纳二极管的击穿电压,不改变p型体区的掺杂情况,从而不影响在同一bcd工艺平台制作的ldmos器件的性能。

附图说明

34.为了更清楚地说明本技术具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它附图。

35.图1显示为采用现有技术在bcd工艺平台制作的齐纳二极管的剖面结构示意图;

36.图2显示为本技术实施例提供的bcd工艺中可自由调控击穿电压的齐纳二极管的剖面结构示意图;

37.图3显示为本技术另一实施例提供的bcd工艺中可自由调控击穿电压的齐纳二极管的剖面结构示意图。

具体实施方式

38.以下通过特定的具体实例说明本技术的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本技术的其它优点与功效。本技术还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

39.下面将结合附图,对本技术中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本技术保护的范围。

40.在本技术的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

41.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电气连接;可以是直接相连,也可以通过中间媒介间接相连,还可以是两个元件内部的连通,可以是无线连接,也可以是有线连接。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本技术中的具体含义。

42.此外,下面所描述的本技术不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

43.请参阅图1,其示出了采用现有技术在bcd工艺平台制作的齐纳二极管的剖面结构示意图。

44.提供p型衬底100,其上形成有n型埋层101和p型埋层102。p型衬底100上还形成有p型外延层(p-epi)103,覆盖整个p型衬底100。

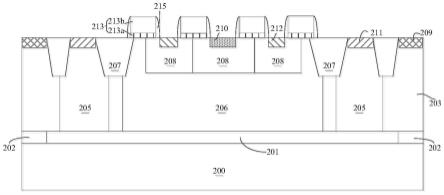

45.p型外延层103中形成有n阱105和p阱106,n阱105底部和p阱106底部与n型埋层101相接触。

46.p型外延层103中形成有多个隔离部件107,分布于p型外延层103的表面。作为示例,隔离部件107为浅沟槽隔离(sti)。

47.p型外延层103中还形成有p型体区108和第二p+注入区109,p型体区108中形成有第一n+注入区110,n阱105中形成有第二n+注入区111,p阱106中形成有第一p+注入区112。

48.第一n+注入区110的两侧的p型外延层103上形成有栅极结构113,作为示例,栅极结构113包括自下而上层叠的栅极氧化层113a和栅极材料层113b。

49.第一n+注入区110和p型体区108构成齐纳二极管,第一p+注入区112作为p型体区108的引出端。

50.隔离部件107实现p型体区108与第一p+注入区112之间、第一p+注入区112与第二n

+注入区111之间、第二n+注入区111与第二p+注入区109之间的表面隔离。

51.在调控如图1所示的齐纳二极管的击穿电压时,需要调整p型体区108的注入参数。在现有的bcd工艺平台中,p型体区108与ldmos的p型体区的注入使用同一掩模,因此,调整p型体区108的注入参数也会改变ldmos的p型体区的掺杂情况,从而影响ldmos的性能。

52.请参阅图2,其示出了本技术实施例提供的bcd工艺中可自由调控击穿电压的齐纳二极管的剖面结构示意图。

53.提供p型衬底200,其上形成有n型埋层201和p型埋层202。p型衬底200上还形成有p型外延层203,覆盖整个p型衬底200。

54.p型外延层203中形成有n阱205和p阱206,n阱205底部和p阱206底部与n型埋层201相接触。

55.p型外延层203中形成有多个隔离部件207,分布于p型外延层203的表面。作为示例,隔离部件207为浅沟槽隔离。

56.p型外延层203中还形成有第二p+注入区209,n阱205中形成有第二n+注入区211,p阱206中形成有三个p型体区208,位于中间的p型体区208中形成有第一n+注入区210,位于左右两侧的p型体区208中形成有第一p+注入区212。

57.三个p型体区208的注入参数相同,区别仅是位于左右两侧的p型体区208的宽度和位于中间的p型体区208的宽度不同。通常,位于左右两侧的p型体区208的宽度小于位于中间的p型体区208的宽度。

58.隔离部件207实现p型体区208与第二n+注入区211之间、第二n+注入区211与第二p+注入区212之间的表面隔离。

59.p阱206的表面上形成有栅极结构213,作为示例,栅极结构213包括自下而上层叠的栅极氧化层213a和栅极材料层213b。栅极结构213的两侧形成有侧墙结构215。

60.制作如图2所示的齐纳二极管的过程中,以栅极结构213为掩模,通过两次离子注入工艺形成p型体区208。通常,第二次p型离子注入的注入能量小于第一次p型离子注入的注入能量,第二次p型离子注入的注入剂量大于第一次p型离子注入的注入剂量,注入角度第二次p型离子注入也大一些。

61.以形成有侧墙结构215的栅极结构213为掩模,通过离子注入工艺分别形成第一n+注入区210和第一p+注入区212。

62.栅极结构213之间的间距决定了形成p型体区208的离子注入工艺的注入窗口特征尺寸的大小。由于栅极结构213之间的间距的特征尺寸较小,因此,位于左右两侧的p型体区208和位于中间的p型体区208会有部分重叠。

63.第一n+注入区210和位于中间的p型体区208构成纵向齐纳二极管。

64.齐纳二极管的击穿电压通常在5.7v左右,如图2所示的齐纳二极管适用于击穿电压偏高的情况。

65.在调控如图2所示的齐纳二极管的击穿电压时,为了避免影响ldmos的性能,不改变p型体区208的注入参数,通过增加第一p+注入区212的注入类型或者调整栅极结构213的特征尺寸,实现降低击穿电压的目的。

66.作为示例,增加第一p+注入区212的注入类型可以是增加5v p型轻掺杂漏(pldd),其工艺参数:注入能量10kev-30kev,注入剂量1e13 cm-2-1e14cm-2

。

67.调整栅极结构213的特征尺寸是指减小栅极结构213的宽度,从而缩短第一n+注入区210和第一p+注入区212之间的间距,降低击穿电压。

68.请参阅图3,其示出了本技术另一实施例提供的bcd工艺中可自由调控击穿电压的齐纳二极管的剖面结构示意图。

69.提供p型衬底300,其上形成有n型埋层301和p型埋层302。p型衬底300上还形成有p型外延层303,覆盖整个p型衬底300。

70.p型外延层303中形成有n阱305和p阱306,n阱305底部和p阱306底部与n型埋层301相接触。

71.p型外延层303中形成有多个隔离部件307,分布于p型外延层303的表面。作为示例,隔离部件307为浅沟槽隔离。

72.p型外延层303中还形成有第二p+注入区309,n阱305中形成有第二n+注入区311,p阱306中形成有注入参数相同的两个p型体区308,两个p型体区308之间的p阱306中形成有第一n+注入区310,p型体区308中形成有第一p+注入区312。

73.隔离部件307实现p型体区308与与第二n+注入区311之间、第二n+注入区311与第二p+注入区312之间的表面隔离。

74.p阱306的表面上形成有栅极结构313,作为示例,栅极结构313包括自下而上层叠的栅极氧化层313a和栅极材料层313b。栅极结构313的两侧形成有侧墙结构315。

75.制作如图3所示的齐纳二极管的过程中,以栅极结构313为掩模,通过两次离子注入工艺形成p型体区308。通常,第二次p型离子注入的注入能量小于第一次p型离子注入的注入能量,第二次p型离子注入的注入剂量大于第一次p型离子注入的注入剂量,注入角度第二次p型离子注入也大一些。

76.以形成有侧墙结构315的栅极结构313为掩模,通过离子注入工艺分别形成第一n+注入区310和第一p+注入区312。

77.栅极结构313之间的间距决定了形成p型体区308的离子注入工艺的注入窗口特征尺寸的大小。

78.第一n+注入区310与p型体区308以及第一p+注入区312构成横向齐纳二极管。

79.齐纳二极管的击穿电压通常在5.7v左右,如图3所示的齐纳二极管适用于击穿电压偏低的情况。

80.在调控如图3所示的齐纳二极管的击穿电压时,为了避免影响ldmos的性能,不改变p型体区308的注入参数,通过调整栅极结构313的特征尺寸,实现升高击穿电压的目的。

81.调整栅极结构313的特征尺寸是指增大栅极结构313的宽度,从而加大第一n+注入区210和第一p+注入区212之间的间距,升高击穿电压。

82.需要说明的是,本实施例中所提供的图示仅以示意方式说明本技术的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

83.综上所述,本技术提供的bcd工艺中可自由调控击穿电压的齐纳二极管,具有以下有益效果:通过增加第一p+注入区的注入类型或者调整栅极结构的特征尺寸来调控齐纳二极管的击穿电压,不改变p型体区的掺杂情况,从而不影响在同一bcd工艺平台制作的ldmos

器件的性能。所以,本技术有效克服了现有技术中的种种缺点而具高度产业利用价值。

84.上述实施例仅例示性说明本技术的原理及其功效,而非用于限制本技术。任何熟悉此技术的人士皆可在不违背本技术的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本技术的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1