一种含有量子阱的外延片、Micro-LED阵列芯片及其制备方法

一种含有量子阱的外延片、micro-led阵列芯片及其制备方法

技术领域

1.本发明属于半导体技术领域,具体涉及一种含有量子阱的外延片、micro-led阵列芯片及其制备方法。

背景技术:

2.micro-led作为第三代显示技术具有高对比度、高响应速度、宽色域以及低功耗和长寿命等优点,被认为是实现ar/vr的理想显示技术。gan基micro-led理论上可以实现全可见光波长的辐射,是制备全彩色micro-led显示器的理想材料。但随着led发光波长的增加,gan中in含量增加,这会导致发光有源区的量子阱与量子垒之间发生晶格失配,从而产生多种结构缺陷,如点缺陷、杂质、位错、v形缺陷等,且in浓度越高,缺陷数目越多。这些缺陷会充当srh复合的复合中心,增加非辐射复合几率,从而降低了绿光波段gan led的内量子效率。过且高的in含量不仅带来了更多的缺陷,还在量子阱内引入了更大的极化电场,导致量子阱能带被拉伸变形,减少了空穴与电子的复合几率,这种现象被称为量子受限斯塔克效应(qcse)。此外,由于inn和gan之间的混溶性差,in成分的增加也导致ingan阱层的化学不均匀性。相分离使得难以实现均匀的ingan合金,甚至导致ingan/gan mqw有源区的退化。

技术实现要素:

3.针对现有技术的不足,本发明提供了一种高量子效率gan基蓝光与绿光micro-led阵列芯片及其制备方法。该制备方法可以生长出含有阶梯结构的量子阱,相比与常规结构的量子阱其具有更高mciro-led的量子效率和发光功率,且阵列结构的micro-led显示芯片也具有更好的光电、波长以及亮度一致性。

4.为解决上述技术问题,本发明提供以下技术方案:

5.第一方面,本发明提供一种含有量子阱的外延片,包括:由下至上依次设置的蓝宝石衬底、第一掺杂层、多量子阱层和第二掺杂层;其中,所述蓝宝石衬底上设置有若干个阵列分布的岛状结构,相邻的岛状结构之间形成凹陷结构,所述第一掺杂层、多量子阱层和第二掺杂层设置在所述凹陷结构内。

6.进一步的,所述多量子阱层包括十个周期的量子阱,前三个所述周期的量子阱为低温量子阱,后七个所述周期的量子阱用于负责电子与空穴的复合;其中,每个所述周期的量子阱的阱宽为3.5nm,垒宽为15nm。

7.进一步的,所述第一掺杂层包括由下至上依次设置的低温gan缓冲层、无掺杂gan层和n型掺杂n-gan层;第二掺杂层包括p型掺杂p-gan层。

8.进一步的,所述岛状结构在垂直于蓝宝石衬底所在平面上的高度为1.5mm~1.7mm,所述岛状结构的包底部长度为2.4mm~2.8mm;相邻的两个岛状结构的中心距离为3mm,且相邻的两个岛状结构的边缘的底部距离为0.6mm~0.2mm;所述低温gan缓冲层的厚度为10nm~20nm,所述无掺杂gan层的厚度为2μm~5μm,所述n型掺杂n-gan层的厚度为1μm~3μm,si掺杂浓度为2.6

×

10

19

cm-3

;所述p型掺杂p-gan层的厚度为100nm~200nm,mg掺杂

浓度为2.2

×

10

20

cm-3

。

9.第二方面,本发明还提供了含有量子阱的外延片的制备方法,该制备方法包括以下步骤,预处理蓝宝石衬底:对蓝宝石衬底进行打磨处理和抛光处理,之后在所述蓝宝石衬底进行图形化处理,以形成若干个阵列分布的所述岛状结构;生长第一掺杂层:在所述蓝宝石衬底上生长所述第一掺杂层;生长多量子阱层:以蓝光量子阱的in组分掺杂含量为17%,绿光量子阱的in组分掺杂含量为28%,多量子阱层的周期数为10,其中前三周期量子阱为低温量子阱,后七周期量子阱负责电子与空穴的复合的参数,在所述所述第一掺杂层上生长所述多量子阱层;生长第二掺杂层:在所述多量子阱层上生长所述第二掺杂层,得到所述含有量子阱的外延片。

10.进一步的,在所述蓝宝石衬底上生长所述第一掺杂层的步骤中,具体包括:先在所述蓝宝石衬底上生长低温gan缓冲层,之后提高温度至1000℃~1100℃,在低温gan缓冲层上生长无掺杂gan层,再利用sih4作为mo源、在1100℃的温度下,在所述无掺杂gan层上生长n型掺杂n-gan层;在所述多量子阱层上生长所述第二掺杂层的步骤中,具体包括:所述多量子阱层上先生长低mg掺杂浓度的p-gan层;然后保持高温高压的状态下通入三甲基铝,再在所述低mg掺杂浓度的p-gan层上生长4周期~9周期的algan/p-gan层;将温度升高至1000℃,在所述algan/p-gan层上生长高温p掺杂层(high temperature p-doped layer,htp);在所述高温p掺杂层上生长重掺杂p型gan层,mg离子的掺杂浓度量级为10

20

cm-3

。

11.进一步的,在生长多量子阱层的步骤中,具体包括:生长常规结构的蓝光量子阱,在关闭tmin气阀的情况下,控制生长温度为853℃,生长量子垒;之后降温至788℃时,打开tmin气阀放出in源生长势阱层,此时载气流量为1300sccm;其中,3.5nm厚的量子阱需要生长240s,之后关闭tmin阀并升高温度生长量子垒,完成一个周期的量子阱和量子垒生长;生长含有阶梯阱边的量子阱:通过稳定tmin的流量,控制生长温度的方法来调控量子阱中的in组分,在量子垒生长完成后,降低温度的同时打开tmin阀,生长in含量渐进的阶梯量子阱;其中,绿光势垒温度为796℃,势阱生长温度为746℃,载气流量为2000sccm,生长3nm量子阱需200s。

12.第三发面,本发明又一种micro-led阵列芯片该micro-led阵列芯片包括:如上述含有量子阱的外延片,以及to光罩板、mesa光罩板、iso光罩板、n-pad光罩板、pv光罩板和p-pad光罩板。

13.进一步的,该micro-led阵列芯片的分辨率为16

×

16,单颗像素尺寸为80μm

×

80μm,每颗所述像素采用正装结构;其中,发光有源区尺寸为50μm

×

60μm,像素间距为86μm,阵列尺寸为1.37mm

×

1.37mm。

14.第四方面,本发明也提供micro-led阵列芯片的制备方法,包括以下步骤,外延片前清洗:前清洗所用的清洗溶液为硫酸、双氧水以及清水按5:1:1比例的混合液,通过淋浴和喷头对外延片进行水洗10分钟,之后使用甩干机甩干,去除表面残留液体;

15.ito光刻:在外延片p-gan表面镀ito薄膜,之后使用ito光罩板,进行光刻处理,得到ito溅镀并进行光刻后的样品;

16.mesa光刻:采用了感应耦合等离子体(icp)刻蚀,对ito溅镀并进行光刻后的样品进行刻蚀,制备所用的icp刻蚀气体为cl2(刻蚀气体)和bcl3(保护气体),在刻蚀中的流量分别为115sccm和5sccm;腔内压力为6mtorr,上下电极的加载功率分别为400w和120w,反射功

率为0.1w和0w,刻蚀深度约为设定刻蚀时间为600s;之后进行内缩腐蚀,采用ito刻蚀液在45℃下腐蚀80s;然后将其在90℃的温度下分别在四个装有胶液ak-1018的清洗槽中进行去胶,每一个槽清洗600s,得到mesa(台面隔离)光刻后的样品;

17.iso刻蚀:对mesa(台面隔离)光刻后的样品进行iso光刻,在各个像素之间形成沟槽,用来在外延片上划分阵列的各个像素,并利用蓝宝石衬底的不导电性使各个像素之间电气绝缘;其中,iso的光刻胶采用egp567,匀胶厚度为10万之后用123℃的热板进行软烤3分钟,采用300j/cm2曝光强度,曝光45s,曝光完成后进行显影180s,得到iso光刻后的样品;

18.n-pad蒸镀:对iso光刻后的样品进行电极蒸镀,蒸镀n-pad电极,采用电子束蒸镀(pvd)沉积,得到n-pad蒸镀后的样品;

19.pv光刻:对n-pad蒸镀后的样品铺一层绝缘膜来进行正负极的电气隔离,通过pv(passivation)掩膜板对绝缘层进行开窗处理;其中,pv采用氧化铝进行电气隔离,采用pecvd技术在220℃的温度下在外延片表面沉积的氧化硅,得到pv光刻后的样品;

20.p-pad蒸镀:对pv光刻后的样品进行p-pad蒸镀,补充部分开窗位置处的n-pad,之后采用电子束蒸镀沉积蒸镀p-pad电极,之后在合金炉内、在280℃的温度下将n-pad和p-pad的金属叠层做出合金,得到p-pad蒸镀后的样品;

21.裂片:对p-pad蒸镀后的样品切割成独立的阵列芯片,得到所述micro-led阵列芯片。

22.与现有技术相比,本发明的有益效果至少包括:

23.1.本发明通过控制量子阱生长温度制备了阶梯阱量子阱。由于in含量渐进使得量子阱壁变得平缓,减少了相邻薄层的晶格失配率骤降,缓解了内部极化电场,使得阱内电子与空穴的复合几率增加,从而增加了micro-led的内量子效率。

24.2.本发明中设计的micro-led阵列可以实现将更多的像素集成在同一块芯片上,且每个像素可以做到几十微米甚至更小,大大提升了micro-led显示的分辨率。

25.3.由于micro-led阵列是通过微纳工艺和新型半导体工艺在同一芯片上加工集成的,因此相比巨量转移后的micro-led显示器件就有更高的一致性、紧凑性以及更短的制备周期与成品可靠性。

附图说明

26.一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,除非有特别申明,附图中的图不构成比例限制。

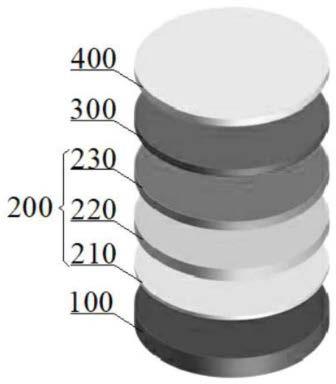

27.图1为本发明实施例1制备的含有量子阱的外延片的结构示意图;

28.图2为本发明实施例1制备的含有量子阱的外延片中蓝宝石衬底上gan两步法生长的过程示意图;

29.图3为本发明实施例1制备的含有量子阱的外延片中多量子阱层的结构示意图;

30.图4为本发明实施例1制备的含有量子阱的外延片的过程中不同量子阱结构对应外量子效率随电流强度变化示意图;

31.图5为本发明实施例1制备的含有量子阱的外延片不同量子阱结构对应单颗led亮

度随工作电流变化示意图;

32.图6为本发明实施例2制备micro-led阵列芯片过程中芯片设计结构示意图;

33.图7为本发明实施例2制备micro-led阵列芯片过程中阵列显示芯片整体工艺流程设计示意图。

34.图中,100-蓝宝石衬底,200-第一掺杂层,210-低温gan缓冲层,220-无掺杂gan层,230-n型掺杂n-gan层,300-多量子阱层,400-第二掺杂层(p型掺杂p-gan层)。

具体实施方式

35.为了解决背景技术中的问题,本发明通过控制量子阱生长温度制备了阶梯阱量子阱,由于in含量渐进使得量子阱壁变得平缓,减少了相邻薄层的晶格失配率骤降,缓解了内部极化电场,使得阱内电子与空穴的复合几率增加,从而增加了micro-led的内量子效率。

36.此外,对于传统的micro-led显示器件,其每个像素都是由单独的micro-led芯片通过巨量转移技术逐个键合在驱动电路基板上,因此其单颗像素难以突破限制,在有限的显示尺寸下难以提高分辨率。且巨量转移技术目前仍是micro-led领域未解决的两大瓶颈之一,其高昂的转移设备与转移成本、复杂的工艺流程以及尚未达标的转移精度和良率都一定程度上限制了micro-led显示的发展。而micro-led阵列可以实现将更多的像素集成在同一块芯片上,且每个像素可以做到几十微米甚至更小,大大提升了micro-led显示的分辨率。由于micro-led阵列是通过微纳工艺和新型半导体工艺在同一芯片上加工集成的,因此相比巨量转移后的micro-led显示器件就有更高的一致性、紧凑性以及更短的制备周期与成品可靠性。

37.本发明提供一种含有量子阱的外延片,如图1所示,包括:由下至上依次设置的蓝宝石衬底(100)、第一掺杂层(200)、多量子阱层(300)和第二掺杂层(400);其中,所述蓝宝石衬底(100)上设置有若干个阵列分布的岛状结构,相邻的岛状结构之间形成凹陷结构,所述第一掺杂层(200)、多量子阱层(300)和第二掺杂层(400)设置在所述凹陷结构内。

38.进一步的,所述第一掺杂层(200)包括由下至上依次设置的低温gan缓冲层(210)、无掺杂gan层(220)和n型掺杂n-gan层(230);第二掺杂层(400)包括p型掺杂p-gan层。

39.下面将结合具体实施例和说明书附图进行详细描述。

40.实施例1

41.本实施例提供一种含有量子阱的外延片的制备方法,该外延片结构如图1所示。制备外延片的具体步骤如下:

42.第一步为蓝宝石衬底的打磨与抛光,并在蓝宝石衬底上进行图形衬底工艺,使之表面结构形成有序阵列分布特征的小岛,岛高在1.5mm~1.7mm之间,岛与岛中心距离一般为3mm,其包底部长约2.4mm~2.8mm,岛与相邻岛边缘的底部距离则在0.6mm~0.2mm间变化;第二步为生长低温gan缓冲层,低温gan缓冲层厚度为15nm,生长时间需要约半小时;第三步为非掺杂(u-)gan层的生长,在生长完低温gan缓冲层后提高温度到1000~1100℃高速生长高质量的非掺杂gan外延层,u-gan层总厚度约为3.5μm,生长过程如图2所示;第四步为n型掺杂n-gan层的生长,采用sih4作为mo源,通过在1100℃的温度下向反应仓内通入sih4;第五步为多量子阱层的生长,蓝光量子阱的in含量为17%,而绿光量子阱的in含量为28%。多量子阱层的周期数为10,其中前三周期量子阱为低温量子阱,后七周期量子阱负责电子

与空穴的复合。其中每周期阱宽3.5nm,垒宽15nm。设计的几种不同量子阱结构如图3所示,不同量子阱结构对应的外量子效率和亮度随电流的变化如图4和图5所示;第六步为p型掺杂p-gan层的生长。

43.实施例2

44.本实施例提供的一种正装micro-led阵列芯片,其结构如图6所示。该阵列芯片的制备方法如图7所示,包括以下步骤:

45.(1)外延片前清洗,前清洗所用的清洗溶液为硫酸、双氧水以及清水按5:1:1比例的混合液,通过淋浴和喷头对外延片进行水洗10分钟,之后使用甩干机甩干,去除表面残留液体;

46.(2)ito光刻,在外延片p-gan表面镀ito薄膜,之后使用ito光罩板,进行光刻处理;

47.(3)mesa光刻,采用了感应耦合等离子体(icp)刻蚀。制备所用的icp刻蚀气体主要为cl2(刻蚀气体)和bcl3(保护气体),其在刻蚀中的流量分别为115和5sccm。腔内压力为6mtorr,上下电极的加载功率分别为400w和120w,反射功率为0.1w和0w。刻蚀深度约为设定刻蚀时间为600s。之后对其进行内缩腐蚀,采用ito刻蚀液在45℃下腐蚀80s。然后将其在90℃的温度下分别在四个装有胶液ak-1018的清洗槽中进行去胶,每一个槽清洗600s;

48.(4)iso刻蚀,iso的光刻胶采用egp567,匀胶厚度为10万之后用123℃的热板进行软烤3分钟,采用300j/cm2曝光强度,曝光45s。曝光完成后进行显影180s;

49.(5)n-pad蒸镀,在iso刻蚀完,需要蒸镀第一层电极n电极,各层金属采用电子束蒸镀(pvd)沉积;

50.(6)pv光刻,pv采用氧化铝来对led的阴极与阳极进行隔离,同样采用pecvd技术在220℃的温度下在外延片表面沉积的氧化硅;

51.(7)p-pad蒸镀,同时补充部分“开窗”位置的n-pad,整个流程与n-pad制备流程相同,最后还需一步还需在合金炉中在280℃的高温下将n-pad和p-pad的金属叠层做出合金。

52.(8)裂片,将完成光刻的外延片切割成独立的阵列芯片。

53.按照上述方案,所述ito光刻工艺,制备过程中采用磁控溅镀的方式沉积ito薄膜,采用厚的ito层,在ito层上热镀一层厚的铝膜,用来和ito形成合金。ito光刻采用正胶rd-2100,光刻胶采用旋涂的方式,厚度为3万旋涂结束后,用110℃的温度软烤3分钟。用波长为365nm的紫外汞灯通过75m j/cm2的曝光量进行曝光20s。完成后拿到显影槽,采用正胶显影液对其显影70s,然后对其用含氮清水冲洗及甩干。然后拿到烘箱中,在130℃的高温下硬烤30分钟来制作坚膜。ito湿法腐蚀在45℃的环境下腐蚀300s。

54.按照上述方案,所述n-pad蒸镀工艺,通过蓝膜进行多次撕金剥离。pad使用的光刻胶匀的是负胶,将n-pad的光罩板在曝光设备中与外延片上mesa层的标记点对齐,在120j/cm2曝光强度下曝光。通过丙酮溶液来去除外延片表面的光刻胶,在去胶机中以90℃的温度去胶35分钟。

55.本领域的普通技术人员可以理解,上述各实施方式是实现本技术的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本技术的精神和范围。任何本领域技术人员,在不脱离本技术的精神和范围内,均可作各自更动与修改,因此本申

请的保护范围应当以权利要求限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1