沟槽栅极金属氧化物半导体场效应晶体管及其制造方法与流程

本公开涉及金属氧化物半导体(metal oxide semiconductor,mos)场效应晶体管(field effect transistor,fet)领域,更具体地,涉及用于这种mosfet的静电放电(electrostatic discharge,esd)保护。

背景技术:

1、沟槽栅极mosfet通常包括朝向mosfet的第一主表面的源极区和形成在与第一主表面相对的第二主表面上的漏极区。源极区和漏极区具有相同的导电类型。

2、在源极区和漏极区之间设置沟道容纳区(即主体区),该沟道容纳区的导电类型与源极区和漏极区的导电类型不同。在源极区和漏极区之间构造导电沟道以确保mosfet导通。为了便于形成这种沟道,提供了接近沟道容纳区但不与其电接触的沟槽栅极。

3、典型的沟槽栅mosfet是电流从一个表面竖直地传导到另一个表面,以便实现高驱动能力。这可以通过在芯片上封装沟槽来实现,沟槽足够深以穿过顶表面下方的相反掺杂的主体区(即沟道容纳区)。

4、栅极沟槽通常设置有某种氧化物,以确保栅极与沟道容纳区电隔离。在栅极沟槽处提供偏压将产生电场,该电场延伸到沟道容纳区中,并因此局部耗尽沟道容纳区和/或使沟道容纳区反转(invert)。

5、沟槽栅极mosfet能够应付例如在100v或以上的范围的高电压操作。此外,这种mosfet能够应付源极区和漏极区之间的高反向偏置电压,而mosfet不会击穿通过任何显著的反向电流。

6、以上设置通常通过在漏极区和沟道容纳区之间引入漂移区来实现,其中,漂移区的导电类型与源极区和漏极区的导电类型相同。然而,漂移区通常具有较低的掺杂浓度。漏极区在与沟道容纳区的界面处形成pn结,以阻挡该反向偏置电流。

7、对于n沟道mosfet,漏极区相对于源极区是正的。如果源极区相对于漏极区是正的,则主体-漏极结(body-drain junction)可以变得偏置,并且电流可以经由漏极区和源极区传导。替代地,对于p沟道mosfet,漏极区相对于源极区是负的。如果源极区相对于漏极区是负的,则主体-漏极结可以再次传导电流。击穿电压取决于漂移区的厚度,厚度越大,击穿电压越高。

8、当比较更传统的横向mosfet与竖直沟槽栅极mosfet时,如上所述,很明显,在竖直沟槽栅极mosfet中,沟道区是沿着沟槽的竖直壁设计的,而不是横向设计的。这允许器件的每单位面积具有高密度的沟道,即每个沟槽两个沟道。

9、mosfet的一个缺点是它们可能易于遭受esd。

技术实现思路

1、下面阐述了本文公开的某些示例的方面的概述。应当理解,这些方面仅被呈现以向读者提供这些特定实施例的简要概述,并且这些方面不旨在限制本公开的范围。实际上,本公开可以涵盖可能未阐述的各种方面和/或方面的组合。

2、本公开的目的是提供一种mosfet,其具有固有的静电放电esd保护。

3、本公开的另一个目的是提供相关的方法和分立封装的mosfet。

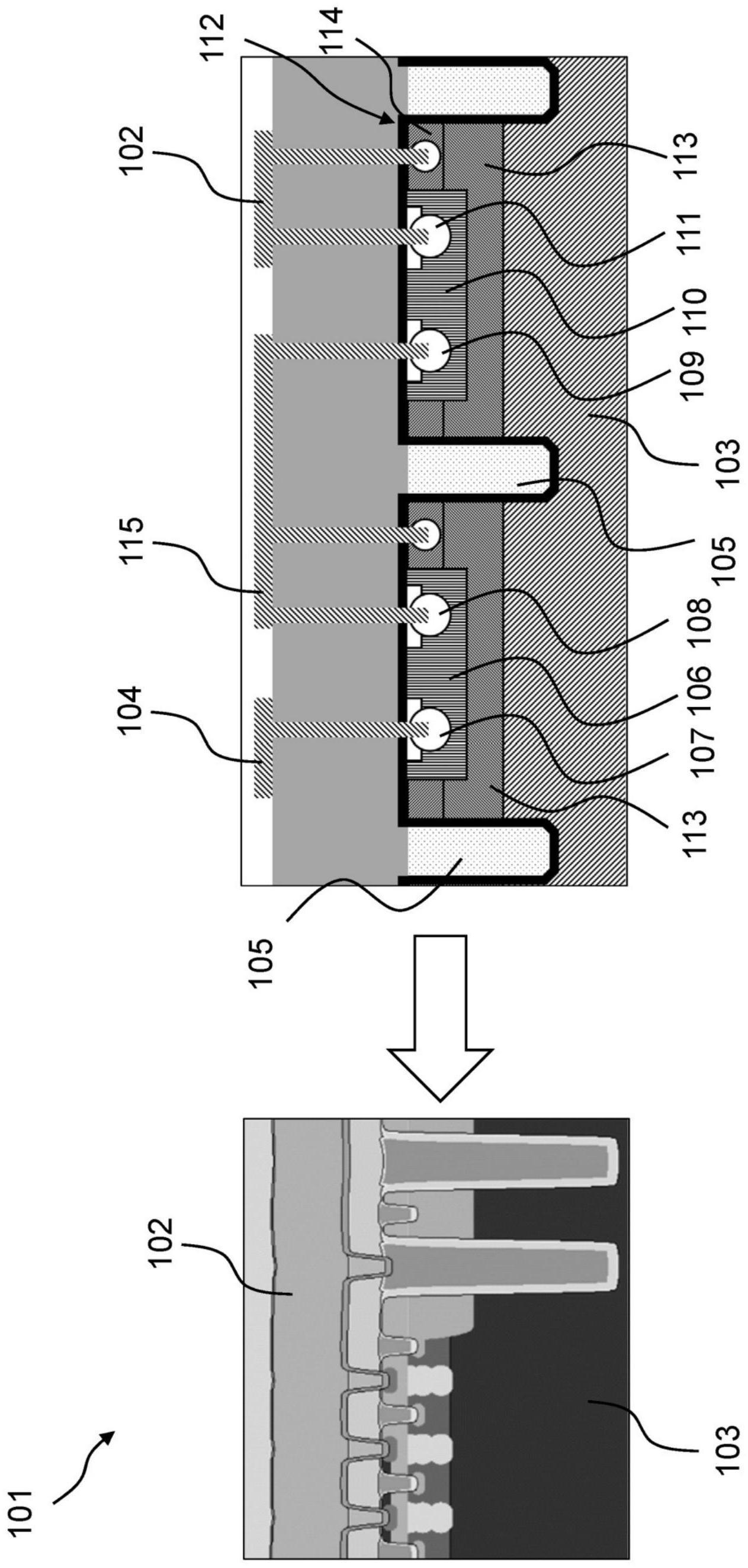

4、在第一方面,提供一种mosfet,包括具有第一主表面的半导体主体,以及从第一主表面延伸到半导体主体中并连接到栅极区的沟槽,半导体主体包括:具有第一导电类型的源极区,其在第一主表面处与沟槽的侧壁相邻;具有第一导电类型的漏极区,其在远离源极区的位置与沟槽相邻;具有与第一导电类型相反的第二导电类型的沟道容纳区,其与沟槽的侧壁相邻并位于源极区和漏极区之间,其中,半导体主体还包括具有第一导电类型的esd区,其与沟槽间隔开并且从第一主表面朝向漏极区延伸但不延伸到漏极区中,其中,esd区包括具有第二导电类型的第一区,其中,第一区连接到栅极区。

5、应当注意,源极触点可以电连接到源极区,漏极触点可以电连接到漏极区,并且栅极触点可以电连接到栅极区。

6、源极区的邻接沟槽的一侧与源极区的邻接沟道容纳区的一侧可以彼此相对。

7、发明人已经发现,将esd保护并入半导体主体中是有益的。优点之一是,可以保持为非常低的漏电流,例如几纳安培。

8、通过在半导体主体内部引入至少一个“部件”来提供esd保护,该“部件”具有在两种半导体材料类型(例如p型和n型)之间的界面或边界。

9、为了实现这种esd保护,半导体主体包括具有第一导电类型的esd区。esd区应当与沟槽间隔开,以便不会过多地干扰mosfet的正常操作。esd区也不应该延伸到漏极区中,因为那样也会干扰mosfet的正常操作。

10、此外,在esd区内,设置有具有第二导电类型的第一区,其中,第一区连接到栅极区。因此,栅极区连接到具有第二导电类型的第一区,第一区位于具有第一导电类型的esd区中。因此,这可以形成pn结等,以用作esd保护。

11、根据本公开,mosfet可以包括多个栅极沟槽,其中,esd区设置在栅极沟槽之间。

12、在一个示例中,esd区还包括具有第二导电类型的第二区,其中,第二区与第一区间隔开,并且其中,第二区连接到主体区(即沟道容纳区)。

13、由于在两种半导体材料类型之间存在两个界面或边界,因此上述结构有效地在栅极区和主体区之间引入两个背对背的二极管。二极管的取向是二极管的阴极彼此连接,这是通过esd区以及esd区内的第一区和第二区的布局实现的。

14、在本公开的实施例的更详细的示例中,半导体主体还包括具有第一导电类型的第二esd区,其与沟槽间隔开并且从第一主表面朝向漏极区延伸但不延伸到漏极区中,其中,第二esd区包括具有第二导电类型的第三区,其中,第三区连接到源极区。

15、第二esd区与第一esd区相似,不同之处在于第二esd区内的第三区连接到源极区,而在第一esd区中的第一区连接到栅极区。

16、第二esd区和第一esd区可以彼此分开,或者可以不彼此分开。第二esd区和第一esd区可以组合在一个单个esd区中。优选地,第二esd区和第一esd区彼此分开。

17、典型地,根据本公开的mosfet包括多个沟槽,其中,上述各esd区设置在这些沟槽中的任何沟槽之间。

18、在更详细的示例中,第二esd区还包括具有第二导电类型的第四区,其中,第四区与第三区间隔开,并且其中,第四区连接到主体区(即沟道容纳区)。

19、该优选示例有效地公开了连接在栅极区和源极区之间的四个背对背的二极管。两个二极管背对背地放置在栅极区和主体区之间。两个二极管背对背地放置在主体区和源极区之间。

20、在另一示例中,esd区延伸到沟道容纳区中。

21、典型地,第一导电类型是n型,并且其中,第二导电类型是p型。

22、在另一示例中,半导体主体还包括:具有第一导电类型的漂移区,其中,漂移区位于漏极区和沟道容纳区之间。

23、漂移区尤其确定mosfet的反向击穿电压。漂移区通常是轻掺杂的,使得mosfet具有高的反向击穿电压。

24、在又一示例中,esd区从第一主表面朝向漂移区延伸,但不延伸到漂移区中。

25、在另一示例中,沟槽从第一主表面延伸到漂移区中。

26、在本公开的第二方面中,提供了一种制造上述实施例中的mosfet的方法,其中,该方法包括以下步骤:形成半导体主体,半导体主体包括:具有第一导电类型的源极区,其在第一主表面处与沟槽的侧壁相邻;具有第一导电类型的漏极区,其在远离源极区的位置与沟槽相邻;具有与第一导电类型相反的第二导电类型的沟道容纳区,其与沟槽的侧壁相邻并位于源极区和漏极区之间;形成沟槽,沟槽从第一主表面延伸到半导体主体中并且连接到栅极区;形成具有第一导电类型的esd区,esd区与沟槽间隔开并且从第一主表面朝向漏极区延伸但不延伸到漏极区中,其中,esd区包括具有第二导电类型的第一区,其中,第一区连接到栅极区。

27、应当注意,参考本公开的第一方面(即mosfet)所解释的优点也适用于本公开的第二方面(即制造这种mosfet的方法)。

28、在一个示例中,该方法还包括以下步骤:在esd区中形成具有第二导电类型的第二区,其中,第二区与第一区间隔开,并且其中,第二区连接到主体区(即沟道容纳区)。

29、在进一步的示例中,该方法还包括以下步骤:形成具有第一导电类型的第二esd区,其与沟槽间隔开,并且从第一主表面朝向漏极区延伸,但不延伸到漏极区中,其中,第二esd区包括具有第二导电类型的第三区,其中,第三区连接到源极区。

30、在一个示例中,该方法还包括以下步骤:在所二esd区中形成具有第二导电类型的第四区,其中,第四区与第三区间隔开,并且其中,第四区连接到主体区(即沟道容纳区)。

31、在另一示例中,第一导电类型是n型,并且其中,第二导电类型是p型。

32、在本公开的第三方面中,提供一种分立封装的mosfet,其包括根据如上提供的任何示例的mosfet。

33、结合附图描述本公开。要强调的是,根据工业中的标准实践,各种特征没有按比例绘制。事实上,为了清楚讨论,各种特征的尺寸可以任意地增加或减小。

34、在附图中,类似的部件和/或特征可以具有相同的参考标记。此外,相同类型的各种组件可通过在参考标记之后加上连接线和区分类似组件的第二标记来进行区分。如果在说明书中仅使用第一参考标记,则该描述适用于具有相同第一参考标记的类似部件中的任一个,而与第二参考标记无关。

35、参考下文描述的示例,本公开的上述和其他方面将是显而易见的并且将被阐明。

- 还没有人留言评论。精彩留言会获得点赞!