集成电路制造用的硬掩膜结构以及集成电路器件制造方法

1.本公开涉及芯片制造过程中的图形转移技术领域,尤其涉及一种集成电路制造用的硬掩膜结构以及集成电路器件制造方法。

背景技术:

2.贵金属拥有极佳的化学稳定性,在图形转移过程中,尤其是精细图形,不会产生失真,因此贵金属薄膜是一种理想的图形转移硬掩膜材料。

3.但是,因贵金属离子会对集成电路器件性能造成杀伤,故在集成电路制造领域并未使用。目前仅在对贵金属离子不敏感的芯片制造领域,会使用其作为硬掩膜,比如非易失性磁性随机存储器(mram)的制造。

技术实现要素:

4.鉴于上述问题,本公开提供了一种集成电路制造用的硬掩膜结构以及集成电路器件制造方法,使贵金属薄膜可用于大规模集成电路的制造。

5.本公开一方面提供了一种集成电路制造用的硬掩膜结构,包括自上而下叠置的第一硬掩膜层和第二硬掩膜层,其中:所述第一硬掩膜层表面用于形成贵金属,并作为图形转移牺牲层,所述第二硬掩膜层作为保护层,用于对待转移的图形材料进行刻蚀;所述第一硬掩膜层和第二硬掩膜层采用不同的材料,且均耐受去除所述贵金属的强氧化性化学液腐蚀;所述第二硬掩膜层耐受湿法腐蚀去除所述第一硬掩膜层的化学液腐蚀,且保证对所述第一硬掩膜层具有预设的腐蚀速率选择比;其中,贵金属包括金、银、钌、铑、钯、锇、铱、铂中的一种或多种薄膜组合。

6.可选地,所述第一硬掩膜层和第二硬掩膜层构成一组二次硬掩膜,所述硬掩膜结构包括依次叠置的多组所述二次硬掩膜。

7.可选地,所述第一硬掩膜层采用非金属介质材料,包括硅、氧化硅、氮化硅、多晶硅、非晶硅、氮氧化硅、掺杂硼或磷的氧化硅、碳化硅、氮化镓、磷化铟、氧化铝或氮化钛中的至少一种;或者所述第一硬掩膜层采用有机材料,包括可旋涂碳膜、非晶碳薄膜、富硅抗反射层或者富碳抗反射层。

8.可选地,所述第二硬掩膜层采用非金属的介质材料,包括硅、氧化硅、氮化硅、多晶硅、非晶硅、氮氧化硅、掺杂硼或磷的氧化硅、碳化硅、氮化镓、磷化铟、氧化铝或氮化钛中的至少一种;或者所述第二硬掩膜层采用有机材料,包括可旋涂碳膜、非晶碳薄膜、富硅抗反射层或者富碳抗反射层。

9.可选地,所述强氧化性化学液包括王水;或者所述强氧化性化学液中的高纯hcl、高纯hno3和h2o的比例范围依次是(0~1)∶(0~1)∶(0~1)。

10.可选地,所述第一硬掩膜层和第二硬掩膜层的材料为两种不同薄膜组合,具体包括以下中的任意一种:所述第一硬掩膜层和第二硬掩膜层的材料分别为si3n4和sio2;所述第一硬掩膜层和第二硬掩膜层的材料分别为富硅抗反射层和可旋涂碳膜;所述第一硬掩膜

层和第二硬掩膜层的材料分别为多晶硅和sio2。

11.本公开另一方面提供了一种应用上述集成电路制造用的硬掩膜结构的集成电路器件制造方法,包括以下步骤:在待转移的图形材料上依次形成第二硬掩膜层、第一硬掩膜层和贵金属层,在所述贵金属层表面涂覆光刻胶进行光刻,形成掩膜图案;离子束刻蚀所述贵金属层,离子束或反应离子刻蚀所述第一硬掩膜层,以将所述掩膜图案转移至所述第二硬掩膜层表面;腐蚀去除所述贵金属层后,离子束或反应离子刻蚀所述第二硬掩膜层,以将所述掩膜图案转移至所述待转移的图形材料表面;腐蚀去除所述第一硬掩膜层后,根据所述掩膜图案对所述待转移的图形材料进行刻蚀;腐蚀去除第二硬掩膜层后,对刻蚀后的产物进行清洗,获得所需的集成电路器件。

12.可选地,所述反应离子刻蚀所述第一硬掩膜层之后,还包括:去除光刻胶。

13.可选地,所述腐蚀去除所述第一硬掩膜层包括以下方式中的任意一种:所述第一硬掩膜层和第二硬掩膜层的材料分别为si3n4和sio2,其中,使用160℃的h3po4腐蚀去除所述第一硬掩膜层;所述第一硬掩膜层和第二硬掩膜层的材料分别为富硅抗反射层和可旋涂碳膜,其中,使用室温稀释氟化氢腐蚀去除所述第一硬掩膜层;所述第一硬掩膜层和第二硬掩膜层的材料分别为多晶硅和sio2,其中,使用室温四甲基氢氧化铵腐蚀去除所述第一硬掩膜层。

14.可选地,在腐蚀去除所述第一硬掩膜层中,腐蚀速率小于1nm/min。

15.与现有技术相比,本公开提供的集成电路制造用的硬掩膜结构以及集成电路器件制造方法,至少具有以下有益效果:

16.(1)可以避免贵金属离子对器件的杀伤,使贵金属薄膜可用于大规模集成电路的制造;

17.(2)二次硬掩膜结构在确保可完成图形准确转移的基础上,可耐受去除贵金属所需的强氧化性化学液腐蚀过程,即在强酸湿法腐蚀过程中二次硬掩膜材料不损失、形貌不变形;并通过至少由两层不同材料组成的二次硬掩膜结构,保护待图形转移材料不被贵金属离子沾污。

附图说明

18.通过以下参照附图对本公开实施例的描述,本公开的上述以及其他目的、特征和优点将更为清楚,在附图中:

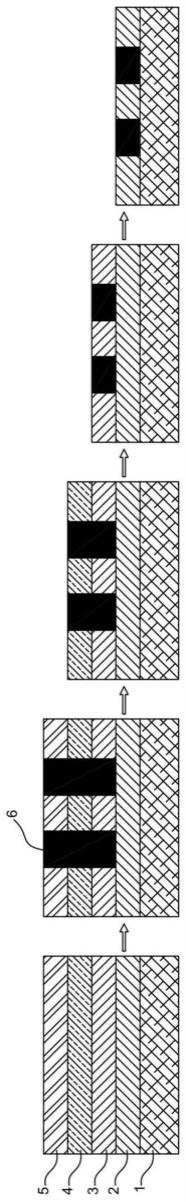

19.图1示意性示出了根据本公开实施例的集成电路制造用的硬掩膜结构的工艺流程图;

20.图2示意性示出了根据本公开实施例的集成电路器件制造方法的流程图。

21.【附图标记说明】

22.1-待转移的图形材料;2-第二硬掩膜层;3-第一硬掩膜层;4-贵金属层;5-光刻胶;6-掩膜图案。

具体实施方式

23.为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。显然,所描述的实施例是本公开一部分实施例,而不是全

部的实施例。基于本公开中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

24.在此使用的术语仅仅是为了描述具体实施例,而并非意在限制本公开。在此使用的术语“包括”、“包含”等表明了所述特征、步骤、操作和/或部件的存在,但是并不排除存在或添加一个或多个其他特征、步骤、操作或部件。

25.在此使用的所有术语(包括技术和科学术语)具有本领域技术人员通常所理解的含义,除非另外定义。应注意,这里使用的术语应解释为具有与本说明书的上下文相一致的含义,而不应以理想化或过于刻板的方式来解释。

26.图1示意性示出了根据本公开实施例的集成电路制造用的硬掩膜结构的工艺流程图。

27.请参阅图1,本公开实施例提供了一种集成电路制造用的硬掩膜结构,包括自上而下叠置的第一硬掩膜层3和第二硬掩膜层2,其中:

28.第一硬掩膜层3表面用于形成贵金属4,并作为图形转移牺牲层,其中,贵金属包括金、银、钌、铑、钯、锇、铱、铂中的一种或多种薄膜组合。第二硬掩膜层2作为保护层,用于对待转移的图形材料1进行刻蚀;

29.第一硬掩膜层3和第二硬掩膜层2采用不同的材料,且均耐受去除贵金属的强氧化性化学液腐蚀;

30.第二硬掩膜层2耐受湿法腐蚀去除第一硬掩膜层3的化学液腐蚀,且保证对第一硬掩膜层3具有预设的腐蚀速率选择比。

31.通过上述结构,该硬掩膜结构可以避免贵金属离子对器件的杀伤,使贵金属薄膜可用于大规模集成电路的制造。并且,该硬掩膜结构在确保可完成图形准确转移的基础上,可耐受去除贵金属所需的强氧化性化学液腐蚀过程,即在强酸湿法腐蚀过程中二次硬掩膜材料不损失、形貌不变形;并通过至少由两层不同材料组成的二次硬掩膜结构,保护待图形转移材料不被贵金属离子沾污。

32.需要说明的是,腐蚀速率选择比可以根据实际需要进行具体的设置,只需满足第二硬掩膜层2对第一硬掩膜层3有很高的腐蚀速率选择比即可。

33.本公开实施例中,第一硬掩膜层3和第二硬掩膜层2构成一组二次硬掩膜,硬掩膜结构包括依次叠置的多组二次硬掩膜。由此,该硬掩膜结构至少由2层不同材料组成,且二层结构的膜质都可耐受强氧化性化学液腐蚀。根据图形转移需要,可以基于上述原则,增加不同材质膜层,形成3层或4层的二次硬掩膜结构。

34.本公开实施例中,第一硬掩膜层3可以采用非金属介质材料,包括且不限于硅、氧化硅、氮化硅、多晶硅、非晶硅、氮氧化硅、掺杂硼(b)或磷(p)的氧化硅、碳化硅、氮化镓、磷化铟、氧化铝或氮化钛中的至少一种。或者,第一硬掩膜层3还可以采用有机材料,包括且不限于可旋涂碳膜(soc)、非晶碳薄膜、富硅抗反射层(sibacr)或者富碳抗反射层(barc)。

35.第一硬掩膜层3和第二硬掩膜层2采用不同的材料。在此基础上,第二硬掩膜层2可以采用非金属的介质材料,包括且不限于硅、氧化硅、氮化硅、多晶硅、非晶硅、氮氧化硅、掺杂b(硼)或p(磷)的氧化硅、碳化硅、氮化镓、磷化铟、氧化铝或氮化钛中的至少一种。或者,第二硬掩膜层2也可以采用有机材料,包括且不限于可旋涂碳膜(soc)、非晶碳薄膜、富硅抗反射层(sibacr)或者富碳抗反射层(barc)。

36.本公开实施例中,强氧化性化学液包括王水;或者,强氧化性化学液中的高纯盐酸(hcl)、高纯硝酸(hno3)和水(h2o)的比例范围依次是(0~1)∶(0~1)∶(0~1)。

37.由此,去除贵金属的强氧化性化学液通常以类王水为主,高纯hcl、高纯hno3和h2o的比例范围依次是(0~1)∶(0~1)∶(0~1)。进而,第一硬掩膜层3和第二硬掩膜层2都可以耐受以类王水为主的强氧化性化学液,腐蚀速率小于1nm/min。

38.本公开实施例中,第一硬掩膜层3和第二硬掩膜层2的材料为两种不同薄膜组合,具体包括以下中的任意一种:

39.第一硬掩膜层3和第二硬掩膜层2的材料分别为si3n4和sio2;

40.第一硬掩膜层3和第二硬掩膜层2的材料分别为富硅抗反射层(sibacr)和可旋涂碳膜(soc);

41.第一硬掩膜层3和第二硬掩膜层2的材料分别为poly si(多晶硅)和sio2。

42.基于上述公开内容,第一硬掩膜层3作为图形转移牺牲层,通过贵金属在形成掩膜图案后,去掉贵金属层;然后使用第一硬掩膜层3进行第二硬掩膜层2的图形转移,完成后,去掉第一硬掩膜层3,这样可避免第一硬掩膜层3中的贵金属离子残留,并且,将晶圆表面的贵金属离子痕量降至可应用水平。在此过程中,第二硬掩膜层2作为保护层,保护待图形转移材料免受去除贵金属使用的强氧化性化学液腐蚀,并保护待图形转移材料表面不受贵金属离子沾污。

43.上述过程完成后,再使用第二硬掩膜层2对最终待图形转移材料进行刻蚀;完成后,再去掉第二硬掩膜层2,获得最终所需的精细图形。

44.图2示意性示出了根据本公开实施例的集成电路器件制造方法的流程图。

45.请参阅图1和图2,根据该实施例的集成电路器件制造方法,可以包括操作s210~操作s250。

46.在操作s210,在待转移的图形材料上依次形成第二硬掩膜层2、第一硬掩膜层3和贵金属层4,在贵金属层4表面涂覆光刻胶5进行光刻,形成掩膜图案。

47.在操作s220,离子束刻蚀(ibe)贵金属层4,离子束或反应离子刻蚀第一硬掩膜层3,以将掩膜图案转移至第二硬掩膜层2表面。

48.可选地,反应离子刻蚀第一硬掩膜层3之后,还可以包括去除光刻胶5。

49.在操作s230,腐蚀去除贵金属层4后,离子束或反应离子刻蚀第二硬掩膜层2,以将掩膜图案转移至待转移的图形材料表面。

50.在操作s240,腐蚀去除第一硬掩膜层3后,根据掩膜图案对待转移的图形材料进行刻蚀。

51.在操作s250,腐蚀去除第二硬掩膜层2后,对刻蚀后的产物进行清洗,获得所需的集成电路器件。

52.示例性地,在第一硬掩膜层3和第二硬掩膜层2的材料分别为si3n4和sio2时,两者都可耐受类王水强腐蚀化学液。此时,可以使用160℃的h3po4腐蚀去除第一硬掩膜层3,也即si3n4。而sio2在此环境下腐蚀速率非常慢,不会被腐蚀破坏。

53.示例性地,在第一硬掩膜层3和第二硬掩膜层2的材料分别为富硅抗反射层(sibacr)和可旋涂碳膜(soc)时,两者都可耐受类王水强腐蚀化学液。此时,可以使用室温稀释氟化氢(hf)腐蚀去除第一硬掩膜层3。由于soc在此环境下腐蚀速率很慢,不会被腐蚀

破坏。

54.示例性地,在第一硬掩膜层3和第二硬掩膜层2的材料分别为poly si(多晶硅)和sio2时,两者都可耐受类王水强腐蚀化学液。此时,可以使用室温tmah(四甲基氢氧化铵)腐蚀去除poly si,而sio2在此环境下基本不被腐蚀。

55.本公开实施例中,在腐蚀去除第一硬掩膜层3中,腐蚀速率小于1nm/min。

56.通过本公开的实施例,获得准确的图形转移结构。在避免贵金属离子对器件的杀伤,使贵金属薄膜可用于大规模集成电路的制造。

57.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。因此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本公开的描述中,“多个”的含义是至少两个,例如两个、三个等,除非另有明确具体的限定。此外,位于元件之前的单词“一”或“一个”不排除存在多个这样的元件。

58.以上所述的具体实施例,对本公开的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本公开的具体实施例而已,并不用于限制本公开,凡在本公开的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1