高维持低阻均匀导通双向可控硅静电防护器件及制作方法与流程

1.本发明涉及静电防护领域,尤其涉及一种高维持低阻均匀导通双向可控硅静电防护器件及其制作方法。

背景技术:

2.随着半导体制程工艺的进步,静电释放(electro-static discharge,esd)造成集成电路芯片以及电子产品失效的情况愈加严重了。对电子产品以及集成电路芯片进行esd防护成为了产品工程师们面临的主要难题之一。

3.传统的可控硅器件(silicon controlled rectifier,scr)与其他esd器件相比,其自身具有双电导调制机构,单位面积泄放效率高,单位寄生电容小,能够用较小的面积达到非常高的鲁棒性等优点。但是传统可控硅器件存在着触发电压过高,器件触发之后的维持电压过低等缺点,触发电压过高会导致防护器件不能及时地保护内核电路,维持电压过低会引起器件出现闩锁效应,导致esd防护器件作用无法正常发挥作用,无法保证i/o端口传输信号的完整性。

4.双向可控硅器件是在传统可控硅基础上改良而来的,具有对称的结构布局,其工作原理与传统单向可控硅相同,可以分别在正反两个方向对电压进行箝位。传统的双向可控硅静电防护器件的剖面图见图1,其等效电路图见图2。当esd脉冲加在双向scr阳极时,n型阱与第三浮空p+注入区形成反偏pn节。当这个脉冲电压高于这个pn结的雪崩击穿电压的时候,器件的内部就会产生大量的雪崩电流,电流的流通路径为经过第二p阱寄生电阻流向了另一端,既阴极。当这个寄生的阱电阻两端的电压高于纵向npn三极管的正向的导通电压的时候,此三极管开启。此三极管开通后,为横向pnp三极管提供基极电流,横向pnp三极管也开启后,也为纵向npn三极管提供基极电流,构成正反馈回路。当两个寄生三极管完全开启后,低阻的scr通路也会完全开启并参与泄放esd电流。双向scr为一个对称结构,当阴极出现esd脉冲的时候,n型深阱与第二p+注入区产生的pn结雪崩击穿,使得pnp三极管与npn三极管先后导通泄放静电。但是传统scr存在着触发电压高、导通电阻高以及低维持电压的缺点,触发电压高和导通电阻高会导致器件容易超出设计窗口,维持电压低容易发生闩锁效应。

技术实现要素:

5.本发明提供了结构简单的高维持低阻均匀导通双向可控硅静电防护器件及其制作方法。

6.为达到上述目的,本发明实施例的技术方案是这样实现的:

7.本发明实施例提供的一种高维持低阻均匀导通双向可控硅静电防护器件,包括p型衬底;

8.所述p型衬底中设有n型埋层;

9.所述n型埋层上方中间为n型阱;

10.所述n型埋层左侧设有第一p阱,所述n型埋层右侧设有第二p阱;

11.所述第一p阱内设有第一p+注入区、所述第一n+注入区、第二n+注入区与第三n+注入区,其中,所述第一p+注入区位于所述第一p阱左侧,所述第一n+注入区位于所述第一p+注入区右侧并贴合在一起,所述第二n+注入区位于所述第一n+注入区的右侧,所述第三n+注入区位于所述第二n+注入区的右侧;

12.所述第二p阱内设有第二p+注入区、第四n+注入区、第五n+注入区与第六n+注入区,其中,所述第二p+注入区位于所述第二p阱右侧,所述第六n+注入区位于所述第二p+注入区左侧并贴合在一起,所述第五n+注入区位于所述第六n+注入区的左侧,所述第四n+注入区位于所述第五n+注入区的左侧;

13.所述第一p阱和所述第二p阱之间设有n型阱,所述n型阱中间位置设有浮空n+注入区,同时,第二浮空p+注入区横跨在所述第一p阱和n阱之间,第三浮空p+注入区横跨在所述n阱和第二p阱之间;所述第一栅极和第二栅极分别在n阱上方的两侧;

14.所述n型埋层的上方的左侧和右侧分别设有第一高压n阱和第二高压n阱;

15.所述第一p+注入区和所述第一n+注入区、第二n+注入区与第三n+注入区连接在一起并作为器件的阳极,所述第四n+注入区、第五n+注入区与第六n+注入区和所述第二p+注入区连接在一起并作为器件的阴极。

16.其中,所述第一场氧隔离区左侧与所述p型衬底左侧边缘接触,所述第一场氧隔离区右侧与所述第一p+注入区左侧接触,所述第一p+注入区右侧与所述第一n+注入区左侧连接,所述第一n+注入区右侧与所述第二场氧隔离区左侧接触,所述第二场氧隔离区右侧与所述第二n+注入区左侧接触,所述第二n+注入区的右侧与所述第三场氧隔离区左侧接触,所述第三场氧隔离区右侧与所述第三n+注入区左侧接触,所述第三n+注入区的右侧与所述第四场氧隔离区左侧接触,所述第四场氧隔离区右侧与所述第一浮空p+注入区左侧接触,所述第一浮空p+注入区的右侧与所述第五场氧隔离区左侧接触,所述第五场氧隔离区右侧与所述第二浮空p+注入区左侧接触,所述第二浮空p+注入区横跨在第一p阱和所述n阱之间;所述第二浮空p+注入区的右侧与所述第一栅极左侧接触,所述第一栅极的右侧与浮空n+注入区左侧接触,所述浮空n+注入区右侧与第二栅极左侧接触,所述第二栅极右侧与第三浮空p+注入区左侧接触,所述第三浮空p+注入区横跨在所述n阱和第二p阱之间;所述第三浮空p+注入区右侧与所述第六场氧隔离区左侧接触,所述第六场氧隔离区的右侧与所述第四浮空p+注入区左侧接触,所述第四浮空p+注入区右侧与所述第七场氧隔离区左侧接触,所述第七场氧隔离区右侧与所述第四n+注入区左侧连接,所述第四n+注入区右侧与所述第八场氧隔离区左侧接触,所述第八场氧隔离区右侧与所述第五n+注入区左侧接触,所述第五n+注入区的右侧与所述第九场氧隔离区左侧接触,所述第九场氧隔离区右侧与所述第六n+注入区左侧接触,所述第六n+注入区右侧与所述第二p+注入区左侧连接,所述第十场氧隔离区右侧与所述p型衬底右侧边缘接触。

17.其中,所述第一场氧隔离区的左部位于所述p型衬底的表面,所述第一场氧隔离区右部位于所述第一p阱的表面;所述第十场氧隔离区左部位于所述第二p阱的表面,所述第十场氧隔离区右部位于所述p型衬底的表面;所述第二场氧隔离区、所述第三场氧隔离区、第四场氧隔离区和所述第五场氧隔离区位于所述第一p阱的表面,所述第六场氧隔离区、第七场氧隔离区、第八场氧隔离区和所述第九场氧隔离区位于所述第二p阱的表面。

18.其中,当高压esd脉冲到达器件的阳极,器件的阴极接低电位时,所述第一n+注入区、所述第一p阱、所述n型阱构成了纵向npn型三极管,所述第一p阱、所述n型阱、所述第二p阱构成横向pnp型三极管结构,所述第二n+注入区、所述第二p阱、所述n型阱构成了纵向npn型三极管,所述第一p阱、所述n型埋层、所述第二p阱构成横向pnp型三极管。

19.其中,当高压esd脉冲到达器件的阳极时,器件阴极接低电位,esd电流沿着所述第一p+注入区流入所述第一p阱、所述n阱、所述第二p阱再到所述第二p+注入区,当esd电流增大到一定的值时,所述n阱和第三浮空p+注入区组成的反向pn结发生雪崩击穿,esd电流通过所述第三浮空p+注入区大量流入所述第二p阱,并在所述第二p阱的等效电阻上形成电压降,当电压降达到0.7v时,右侧纵向npn型三极管导通并为左侧横向pnp三极管提供基极电流进而促进其导通,形成正反馈效应,此时器件被成功触发。

20.本发明实施例还提供了一种高维持低阻均匀导通双向可控硅静电防护器件的制作方法,所述方法包括:

21.步骤一:在p型衬底中形成n型埋层;

22.步骤二:在n型埋层上方中间生成n型阱;

23.步骤三:在所述p型衬底中从左至右依次生成第一场氧隔离区、第二场氧隔离区、第三场氧隔离区、第四场氧隔离区、第五场氧隔离区、第六场氧隔离区、第七场氧隔离区、第八场氧隔离区、第九场氧隔离区、第十场氧隔离区;

24.步骤四:在所述n型埋层上方两侧分别生成第一高压n阱、第二高压n阱、第一p阱和第二p阱;

25.步骤五:在所述n型阱上方两侧分别生成第一栅极和第二栅极;

26.步骤六:在所述第一p阱中从左至右依次形成第一p+注入区、第一n+注入区、第二n+注入区、第三n+注入区和第一浮空p+注入区、第二浮空p+注入区,且所述第二浮空p+注入区横跨在第一p阱和所述n阱之间,在所述n阱中从左至右依次形成第二浮空p+注入区、浮空n+注入区和第三浮空p+注入区,且所述第三浮空p+注入区横跨在所述n阱和第二p阱之间,在所述第二p阱中从左至右依次形成第三浮空p+注入区、第四浮空p+注入区和第四n+注入区、第五n+注入区、第六n+注入区、第二p+注入区,同时在所述n阱内形成浮空n+注入区;且所述第一场氧隔离区左侧与所述p型衬底左侧边缘接触,所述第一场氧隔离区右侧与所述第一p+注入区左侧接触,所述第一p+注入区右侧与所述第一n+注入区左侧连接,所述第一n+注入区右侧与所述第二场氧隔离区左侧接触,所述第二场氧隔离区右侧与所述第二n+注入区左侧接触,所述第二n+注入区的右侧与所述第三场氧隔离区左侧接触,所述第三场氧隔离区右侧与所述第三n+注入区左侧接触,所述第三n+注入区的右侧与所述第四场氧隔离区左侧接触,所述第四场氧隔离区右侧与所述第一浮空p+注入区左侧接触,所述第一浮空p+注入区的右侧与所述第五场氧隔离区左侧接触,所述第五场氧隔离区右侧与所述第二浮空p+注入区左侧接触,所述第二浮空p+注入区横跨在第一p阱和所述n阱之间;所述第二浮空p+注入区的右侧与所述第一栅极左侧接触,所述第一栅极的右侧与浮空n+注入区左侧接触,所述浮空n+注入区右侧与第二栅极左侧接触,所述第二栅极右侧与第三浮空p+注入区左侧接触,所述第三浮空p+注入区横跨在所述n阱和第二p阱之间;所述第三浮空p+注入区右侧与所述第六场氧隔离区左侧接触,所述第六场氧隔离区的右侧与所述第四浮空p+注入区左侧接触,所述第四浮空p+注入区右侧与所述第七场氧隔离区左侧接触,所述第七场氧

隔离区右侧与所述第四n+注入区左侧连接,所述第四n+注入区右侧与所述第八场氧隔离区左侧接触,所述第八场氧隔离区右侧与所述第五n+注入区左侧接触,所述第五n+注入区的右侧与所述第九场氧隔离区左侧接触,所述第九场氧隔离区右侧与所述第六n+注入区左侧接触,所述第六n+注入区右侧与所述第二p+注入区左侧连接,所述第十场氧隔离区右侧与所述p型衬底右侧边缘接触;

27.步骤七:对所述第一p+注入区、所述第一n+注入区、所述第二n+注入区、第三n+注入区和第一浮空p+注入区、横跨在第一p阱和所述n阱之间的第二浮空p+注入区、n型阱中的所述浮空n+注入区、横跨在所述n阱和第二p阱之间的第三浮空p+注入区、第四浮空p+注入区和第四n+注入区、第五n+注入区、第六n+注入区、第二p+注入区进行退火处理,消除杂质在注入区进行的迁移;

28.步骤八:将所述第一p+注入区和所述第一n+注入区、第二n+注入区与第三n+注入区连接在一起并作为器件的阳极,将所述第四n+注入区、第五n+注入区与第六n+注入区和所述第二p+注入区连接在一起并作为器件的阴极。

29.其中,所述方法前还包括:

30.在所述p型衬底上生长一层二氧化硅薄膜,之后淀积一层氮化硅;旋涂光刻胶层于晶圆上,加掩膜版对其进行曝光以及显影,形成隔离浅槽;将二氧化硅、氮化硅和隔离浅槽进行刻蚀,去除光刻胶层,淀积一层二氧化硅,然后进行化学机抛光,直到氮化硅层为止,去除掉氮化硅层。

31.本发明实施例提供了一种高维持低阻均匀导通双向可控硅静电防护器件及其制作方法,有益效果在于:

32.1、本发明可以在器件版图面积不增加的情况下,通过对器件内部结构层次的变化以及接线的变化来实现降低触发电压和导通电阻、提高维持电压的目的,第一p+注入区、第一n+注入区、第二n+注入区与第三n+注入区通过导线直接相连并作为器件的阳极,第二p+注入区、第四n+注入区、第五n+注入区与第六n+注入区通过导线直接相连并作为器件的阴极,该设计能够在保证器件高维持电压的基础上,有效地提高器件的导通均匀性;第一浮空p+注入区设置于第一p阱内的第三n+注入区右侧,第四浮空p+注入区设置于第二p阱内的第四n+注入区左侧,该浮空p+注入的设计作用在于提高维持电压。

33.2、本发明的第一p阱和第二p阱之间设有n型阱,n型阱中间位置设有浮空n+注入区,同时,第二浮空p+注入区和第三浮空p+注入区分别设置横跨在第一p阱、n型阱和第二p阱中间位置,并且,第二浮空p+注入区和浮空n+注入区之间设有第一栅极,第三浮空p+注入区和浮空n+注入区之间设有第二栅极,该浮空双栅结构的设计能够降低器件的导通电阻,促进scr路径的开启。

34.3、本发明的第一p阱中的第二场氧隔离区以及第三场氧隔离区和第二p阱的第八场氧隔离区以及第九场氧隔离区的尺寸s2可调,当增大s2时,寄生三极管基极的宽度增加,使得寄生三极管的放大倍数降低,从而减弱scr的正反馈,使得器件的维持电压上升。同时,随着s2的增大,器件的面积得以增加,使得器件的散热能力增加,进而增加了器件的失效电流。

附图说明

35.图1为目前已知的双向scr静电防护器件的剖面图;

36.图2为目前已知的双向scr静电防护器件的等效电路图;

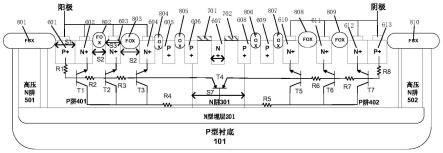

37.图3为本发明一实施例提供的高维持低阻均匀导通双向可控硅静电防护器件的剖面图;

38.图4为本发明一实施例提供的高维持低阻均匀导通双向可控硅静电防护器件的等效电路图;

39.图5为本发明一实施例提供的高维持低阻均匀导通双向可控硅静电防护器件的总电流密度分布仿真图。

具体实施方式

40.以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

41.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

42.如图3所示,一种高维持低阻均匀导通双向可控硅静电防护器件,包括p型衬底101;所述p型衬底101中设有n型埋层201;所述n型埋层201上方中间为n型阱301;所述n型埋层201左侧设有第一p阱401,所述n型埋层201右侧设有第二p阱402;所述第一p阱401内设有第一p+注入区601、第一n+注入区602,第二n+注入区603和第三n+注入区604,其中,所述第一p+注入区601位于所述第一p阱401左侧,所述第一n+注入区602位于所述第一p+注入区601右侧并贴合在一起,所述第二n+注入区603位于所述第一n+注入区602的右侧,所述第三n+注入区604位于所述第二n+注入区603的右侧;

43.所述第二p阱402内设有第二p+注入区613、第四n+注入区610、第五n+注入区611和第六n+注入区612,其中,所述第二p+注入区613位于所述第二p阱402右侧,所述第六n+注入区612位于所述第二p+注入区613左侧并贴合在一起,所述第五n+注入区611位于所述第六n+注入区612的左侧,所述第四n+注入区610位于所述第五n+注入区611的左侧,同时,所述第三n+注入区604与所述第二n+注入区603通过金属导线直接连接;

44.所述第一p阱401和所述第二p阱402之间设有n型阱301,所述n型阱301中间位置设有浮空n+注入区607,同时,第一浮空p+注入区605设置于第一p阱401内的第三n+注入区604右侧,第四浮空p+注入区609设置于第二p阱402内的第四n+注入区610左侧;所述第二浮空p+注入区606和第三浮空p+注入区608分别设置横跨在第一p阱401、n型阱301和第二p阱402中间位置;

45.所述n型埋层201的上方的左侧和右侧分别设有第一高压n阱501和第二高压n阱502;

46.所述第二浮空p+注入区606和浮空n+注入区607之间设有第一栅极701,第三浮空p+注入区608和浮空n+注入区607之间设有第二栅极702;

47.所述第一p+注入区601、第一n+注入区602、第二n+注入区603与第三n+注入区604通过导线直接相连并作为器件的阳极,第二p+注入区613、第四n+注入区610、第五n+注入区

611与第六n+注入区612通过导线直接相连并作为器件的阴极。

48.所述第一p+注入区601左侧与所述p型衬底101左侧边缘之间设有第一场氧隔离区801,所述第一p+注入区601右侧与所述第一n+注入区602左侧连接,所述第一n+注入区602右侧与所述第二n+注入区603左侧设有第二场氧隔离区802,所述第二n+注入区603右侧与所述第三n+注入区604左侧设有第三场氧隔离区803;所述第二p+注入区613左侧与所述p型衬底101右侧边缘之间设有第十场氧隔离区810,所述第二p+注入区613左侧与所述第六n+注入区612右侧连接,所述第六n+注入区612左侧与所述第五n+注入区611右侧设有第九场氧隔离区809,所述第五n+注入区611左侧与所述第四n+注入区610右侧设有第八场氧隔离区808;所述第三n+注入区604右侧与所述第一浮空p+注入区605左侧设有第四场氧隔离区804;所述第一浮空p+注入区605右侧与所述第二浮空p+注入区606左侧设有第五场氧隔离区805;所述第四n+注入区610左侧与所述第四浮空p+注入区609右侧设有第七场氧隔离区807;所述第四浮空p+注入区609左侧与所述第三浮空p+注入区608右侧设有第六场氧隔离区806。

49.所述第一场氧隔离区801的左部位于所述p型衬底101的表面,所述第一场氧隔离区801右部位于所述第一p阱401的表面;所述第十场氧隔离区810左部位于所述第二p阱402的表面,所述第十场氧隔离区810右部位于所述p型衬底101的表面;所述第二场氧隔离区802、所述第三场氧隔离区803、所述第四场氧隔离区804和所述第五场氧隔离区805位于所述第一p阱401的表面,所述第九场氧隔离区809、所述第八场氧隔离区808、所述第七场氧隔离区807和所述第六场氧隔离区806位于所述第二p阱402的表面。

50.如图4所示,当高压esd脉冲到达器件的阳极,器件的阴极接低电位时,所述第一n+注入区602、所述第一p阱401、所述n型阱301构成了纵向npn型三极管,所述第二n+注入区603、所述第一p阱401、所述n型阱301构成了纵向npn型三极管,所述第三n+注入区604、所述第一p阱401、所述n型阱301构成了纵向npn型三极管,所述第四n+注入区610、所述第二p阱402、所述n型阱301构成了纵向npn型三极管,所述第五n+注入区611、所述第二p阱402、所述n型阱301构成了纵向npn型三极管,所述第一p阱401、所述n型阱301、所述第二p阱402构成横向pnp型三极管结构,所述第六n+注入区612、所述第二p阱402、所述n型阱301构成了纵向npn型三极管,所述第一p阱401、所述n型埋层201、所述第二p阱402构成横向pnp型三极管。第一p阱401里面的纵向寄生npn管和第二p阱402里的纵向寄生纵向npn管可以两两组合与横向pnp管构成双向scr结构。

51.当高压esd脉冲到达器件的阳极时,器件阴极接低电位,esd电流沿着所述第一p+注入区601流入所述第一p阱401、所述n阱、所述第二p阱402再到所述第二p+注入区613,当esd电流增大到一定的值时,n阱和第三浮空p+注入区608组成的反向pn结发生雪崩击穿,esd电流通过所述第三浮空p+注入区608大量流入所述第二p阱402,由等效电路图图4可以看出,当雪崩电流在第二p阱402寄生电阻上产生的压降足够大时,寄生三极管t5开启,寄生三级管t5开启后会为寄生三极管t2的基极提供电流,两者形成正反馈回路,正向的scr结构被导通泄放静电。由器件总电流密度分布仿真图图5可以看出,第一p+注入区601和第四n+注入区610的下方电流密度分布最为密集,说明该路径为主泄放路径,同时,电流在n型埋层201也较为密集,该泄放路径能够引导电流流向器件深处,能够有效地提高器件的维持电压和失效电流。同理,当阴极出现正向esd脉冲的时候,n阱和第二浮空p+注入区606组成的反

向pn结发生雪崩击穿,雪崩电流流经第一p阱401寄生电阻流入阳极,由等效电路图图4可以看出,当雪崩电流在第一p阱401寄生电阻上产生的压降足够大时,寄生三极管t3开启,寄生三级管t3开启后会为寄生三极管t2的基极提供电流,两者形成正反馈回路,反向的scr结构被导通泄放静电。

52.与传统双向可控硅静电防护器件相比,本器件改变传统可控硅的触发路径,esd脉冲在触发器件的阶段所经过的金属导线路径的寄生电阻非常小,能够有效减小器件的导通电阻,n阱和第三浮空p+注入区608、n阱和第二浮空p+注入区606组成的反偏pn结使得器件能够拥有更低的触发电压,同时,中间浮空n+注入区607能够提高中间n型阱301的掺杂浓度,增加器件可控硅路径的寄生pnp三极管的基区浓度,进而提高器件的维持电压。

53.所述第一浮空p+和第四浮空p+能够增加器件的阴阳极间距,能够有效提高器件的维持电压,n型埋层201能够将可控硅的主要结构与p型衬底101完全隔离,有效地提高了器件的防漏电能力。

54.所述第一p阱401中的第二场氧隔离区802以及第三场氧隔离区803和第二p阱402的第八场氧隔离区808以及第九场氧隔离区809的尺寸s2可调,当增大s2时,如图4所示,寄生三极管t2、寄生三极管t3、寄生三极管t5、寄生三极管t6的基极的宽度增加,使得寄生三极管的放大倍数降低,从而减弱scr的正反馈,使得器件的维持电压上升。同时,随着s2的增大,器件的面积得以增加,使得器件的散热能力增加,进而增加了器件的失效电流。

55.本发明实施例还提供了一种高维持低阻均匀导通双向可控硅静电防护器件的制作方法,包括以下步骤:

56.步骤一:在p型衬底101中形成n型埋层201;

57.步骤二:在n型埋层201上方中间生成n型阱301;

58.步骤三:在所述p型衬底101中从左至右依次生成第一场氧隔离区801、第二场氧隔离区802、第三场氧隔离区803、第四场氧隔离区804、第五场氧隔离区805、第六场氧隔离区806、第七场氧隔离区807、第八场氧隔离区808、第九场氧隔离区809、第十场氧隔离区810;

59.步骤四:在所述n型埋层201上方两侧分别生成第一高压n阱501、第二高压n阱502、第一p阱401和第二p阱402;

60.步骤五:在所述n型阱301上方两侧分别生成第一栅极701和第二栅极702;

61.步骤六:在所述第一p阱401中从左至右依次形成第一p+注入区601、第一n+注入区602、第二n+注入区603、第三n+注入区604和第一浮空p+注入区605、第二浮空p+注入区606,且所述第二浮空p+注入区606横跨在第一p阱401和所述n阱301之间,在所述n阱301中从左至右依次形成第二浮空p+注入区606、浮空n+注入区607和第三浮空p+注入区608,且所述第三浮空p+注入区608横跨在所述n阱301和第二p阱402之间,在所述第二p阱402中从左至右依次形成第三浮空p+注入区608、第四浮空p+注入区609和第四n+注入区610、第五n+注入区611、第六n+注入区612、第二p+注入区613,同时在所述n阱301内形成浮空n+注入区607;且所述第一场氧隔离区801左侧与所述p型衬底101左侧边缘接触,所述第一场氧隔离区801右侧与所述第一p+注入区601左侧接触,所述第一p+注入区601右侧与所述第一n+注入区602左侧连接,所述第一n+注入区602右侧与所述第二场氧隔离区802左侧接触,所述第二场氧隔离区802右侧与所述第二n+注入区603左侧接触,所述第二n+注入区603的右侧与所述第三场氧隔离区803左侧接触,所述第三场氧隔离区803右侧与所述第三n+注入区604左侧接

触,所述第三n+注入区604的右侧与所述第四场氧隔离区804左侧接触,所述第四场氧隔离区804右侧与所述第一浮空p+注入区605左侧接触,所述第一浮空p+注入区605的右侧与所述第五场氧隔离区805左侧接触,所述第五场氧隔离区805右侧与所述第二浮空p+注入区606左侧接触,所述第二浮空p+注入区606横跨在第一p阱401和所述n阱301之间;所述第二浮空p+注入区606的右侧与所述第一栅极701左侧接触,所述第一栅极701的右侧与浮空n+注入区607左侧接触,所述浮空n+注入区607右侧与第二栅极702左侧接触,所述第二栅极702右侧与第三浮空p+注入区608左侧接触,所述第三浮空p+注入区608横跨在所述n阱301和第二p阱402之间;所述第三浮空p+注入区608右侧与所述第六场氧隔离区806左侧接触,所述第六场氧隔离区806的右侧与所述第四浮空p+注入区609左侧接触,所述第四浮空p+注入区609右侧与所述第七场氧隔离区807左侧接触,所述第七场氧隔离区807右侧与所述第四n+注入区610左侧连接,所述第四n+注入区610右侧与所述第八场氧隔离区808左侧接触,所述第八场氧隔离区808右侧与所述第五n+注入区611左侧接触,所述第五n+注入区611的右侧与所述第九场氧隔离区809左侧接触,所述第九场氧隔离区809右侧与所述第六n+注入区612左侧接触,所述第六n+注入区612右侧与所述第二p+注入区613左侧连接,所述第十场氧隔离区810右侧与所述p型衬底101右侧边缘接触;

62.步骤七:对所述第一p+注入区601、所述第一n+注入区602、所述第二n+注入区603、第三n+注入区604和第一浮空p+注入区605、横跨在第一p阱401和所述n阱301之间的第二浮空p+注入区606、n型阱301中的所述浮空n+注入区607、横跨在所述n阱301和第二p阱402之间的第三浮空p+注入区608、第四浮空p+注入区609和第四n+注入区610、第五n+注入区611、第六n+注入区612、第二p+注入区613进行退火处理,消除杂质在注入区进行的迁移;

63.步骤八:将所述第一p+注入区601和所述第一n+注入区602、第二n+注入区603与第三n+注入区604连接在一起并作为器件的阳极,将所述第四n+注入区610、第五n+注入区611与第六n+注入区612和所述第二p+注入区613连接在一起并作为器件的阴极。

64.可选的,所述方法前还包括:

65.在所述p型衬底101上生长一层二氧化硅薄膜,之后淀积一层氮化硅;旋涂光刻胶层于晶圆上,加掩膜版对其进行曝光以及显影,形成隔离浅槽;将二氧化硅、氮化硅和隔离浅槽进行刻蚀,去除光刻胶层,淀积一层二氧化硅,然后进行化学机抛光,直到氮化硅层为止,去除掉氮化硅层。

66.本发明高维持低阻均匀导通双向可控硅静电防护器件的制作方法过程简单、操作方便。制作出的双向可控硅静电防护器件结构,拥有较低击穿电压的反向雪崩击穿面,能够有效降低器件的触发电压,拥有寄生电阻较低的触发路径,能够有效降低器件的导通电阻。同时,浮空的n+注入的加入能够有效提高器件的维持电压。本器件可根据不同应用场景下esd设计窗口的要求,通过控制击穿面n+注入区的尺寸大小来调节器件的触发电压。本器件能够运用在esd保护设计中,有效地保护了内部芯片,远离闩锁的风险。本发明实例器件采用0.25μm的bcdmos工艺。

67.以上所述仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内所作的任何修改、等同替换、改进等,均包含在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1