半导体封装结构及其制备方法与流程

本公开涉及半导体,尤其涉及一种半导体封装结构及其制备方法。

背景技术:

1、半导体封装是将多个半导体器件以纵向堆叠或者横向并排的方式排布于封装结构中,并利用封装结构对半导体器件形成保护效果,被广泛地应用到半导体设备或装置中。

2、半导体封装包括封装基板、待封装半导体器件和封装层。待封装半导体器件可以为多个芯片,多个芯片堆叠或者并排排布于封装基板上,多个芯片的外部通过封装层进行封装,避免芯片外露,保证对芯片的保护效果。其中,不同芯片之间设置有硅中介层(siinterposer)作为金属互连结构,实现不同芯片之间的信号连接。硅中介层中设置有硅通孔结构(through silicon vias,简称tsv)和深槽电容(deep trench capacitor,简称dtc)。

3、然而,上述的硅中介层中的深槽电容的结构较为复杂,制备难度较大,且电容量有待提高。

技术实现思路

1、本公开提供一种半导体封装结构及其制备方法,能够有效简化半导体封装结构中的电容的结构,减小其制备难度,同时提高电容量。

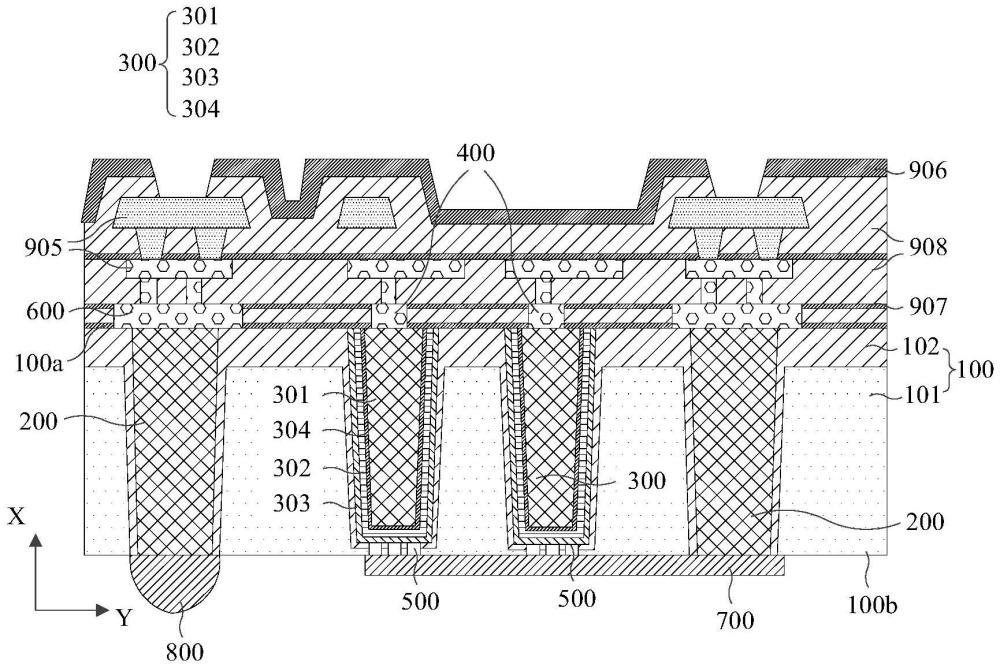

2、第一方面,本公开提供一种半导体封装结构,包括中介层、导电通孔和电容;

3、中介层包括沿厚度方向相对的第一面和第二面,导电通孔和电容间隔设置于中介层中;

4、导电通孔的相对两端分别延伸至第一面和第二面;电容包括依次层叠的第一电极层、电容介质层和第二电极层;至少部分第一电极层靠近第一面,且通过第一导电结构,经由第一面电引出中介层;至少部分第二电极层靠近第二面,且通过第二导电结构,经由第二面电引出中介层。

5、在上述的半导体封装结构中,可选的是,电容包括多个,多个电容间隔排布于所述中介层中。

6、在上述的半导体封装结构中,可选的是,第一电极层靠近第一面的一端、导电通孔的靠近第一面的一端以及第一面齐平。

7、在上述的半导体封装结构中,可选的是,还包括第三导电结构,导电通孔的靠近第一面的一端与第三导电结构连接,且通过第三导电结构电引出中介层;

8、第一导电结构和第三导电结构同层同材料。

9、在上述的半导体封装结构中,可选的是,靠近第二面的第二电极层与第二面之间具有间距,第二导电结构嵌设于位于第二面和第二电极层之间的中介层中,第二导电结构的一端与第二电极层连接,第二导电结构的另一端引至第二面。

10、在上述的半导体封装结构中,可选的是,还包括第四导电结构,第四导电结构位于第二面,第二导电结构与第四导电结构连接;

11、当电容有多个时,多个电容的第二电极层均通过第二导电结构与同一个第四导电结构连接;或,第四导电结构有多个,多个电容的第二电极层通过对应的第二导电结构与不同的第四导电结构连接。

12、在上述的半导体封装结构中,可选的是,还包括第五导电结构,第五导电结构位于第二面,导电通孔的靠近第二面的一端与第二面齐平,并与第五导电结构连接,且通过第五导电结构电引出中介层。

13、在上述的半导体封装结构中,可选的是,中介层包括中介本体层和电介质层,电介质层靠近中介层的第一面分布,中介本体层靠近中介层的第二面分布;

14、且,至少部分电介质层分布于导电通孔和中介本体层之间;和/或,至少部分电介质层分布于电容与中介本体层之间。

15、第二方面,本公开提供一种半导体封装结构的制备方法,包括:

16、提供中介层,中介层包括沿厚度方向相对的第一面和第二面;

17、在中介层中形成导电通孔和电容,导电通孔和电容间隔排布,导电通孔的相对两端分别延伸至第一面和第二面,电容包括依次层叠的第一电极层、电容介质层和第二电极层;至少部分第一电极层靠近第一面,且通过第一导电结构,经由第一面电引出中介层;至少部分第二电极层靠近第二面,且通过第二导电结构,经由第二面电引出中介层。

18、在上述的半导体封装结构的制备方法中,可选的是,形成导电通孔和电容,包括:

19、在中介层中形成导电通孔;

20、在中介层中形成电容沟槽,电容沟槽的槽底与导电通孔的底部均与中介层的底部具有间距,且电容沟槽的槽底与中介层的底部之间的间距,大于导电通孔的底部与中介层的底部之间的间距;

21、在电容沟槽中形成电容。

22、在上述的半导体封装结构的制备方法中,可选的是,在电容沟槽中形成电容,包括:

23、形成第二电极层,第二电极层位于电容沟槽中,第二电极层中形成第一沟槽;

24、形成电容介质层,电容介质层位于第一沟槽中,电容介质层中形成第二沟槽;

25、形成第一电极层,第一电极层位于第二沟槽中,第一电极层、电容介质层和第二电极层共同形成电容。

26、在上述的半导体封装结构的制备方法中,可选的是,形成电容之后,还包括:

27、平坦化处理导电通孔的顶部、电容的顶部以及中介层的顶部,以使导电通孔的顶面、电容的顶面以及中介层的顶面齐平,中介层的顶面形成第一面;

28、形成第一导电结构和第三导电结构,第一导电结构与第一电极层连接,第三导电结构与导电通孔的顶部连接,第一导电结构和第三导电结构同层同材料。

29、在上述的半导体封装结构的制备方法中,可选的是,形成第一导电结构和第三导电结构之后,还包括:

30、处理中介层的底部,以使导电通孔的底部暴露;被处理后的中介层的底面形成第二面;

31、形成第四沟槽,第四沟槽位于电容的底部的中介层中,并暴露电容的第二电极层;

32、形成第二导电结构,第二导电结构位于第四沟槽中,并与暴露的第二电极层连接;

33、形成第四导电结构,第四导电结构位于中介层的底部,并与第二导电结构连接;

34、形成第五导电结构,第五导电结构位于中介层的底部,并与导电通孔暴露的底部连接。

35、在上述的半导体封装结构的制备方法中,可选的是,电容有多个,多个电容间隔排布于中介层中;

36、多个电容的第二电极层均通过第二导电结构与同一个第四导电结构连接;或,第四导电结构有多个,多个电容的第二电极层通过对应的第二导电结构与不同的第四导电结构连接。

37、在上述的半导体封装结构的制备方法中,可选的是,提供中介层包括:

38、形成中介本体层;

39、形成电介质层,电介质层位于中介本体层上,中介本体层和电介质层共同形成中介层,电介质层靠近中介层的第一面分布,中介本体层靠近中介层的第二面分布;

40、且,至少部分电介质层分布于导电通孔和中介本体层之间;和/或,至少部分电介质层分布于电容与中介本体层之间。

41、本公开提供的半导体封装结构及其制备方法,通过在半导体封装结构中设置中介层、导电通孔和电容,导电通孔和电容间隔设置于中介层中,中介层可以对两者起到保护效果。通过将导电通孔的两端分别延伸至中介层的第一面和第二面,便于通过导电通孔连接位于中介层两侧的元件,实现不同元件之间的信号传输。电容可以有效抑制导电通孔的电路噪声,降低电路电压对通过该半导体封装结构封装的元件的影响。通过将电容的第一电极层和第二电极层分别靠近第一面和第二面设置,并且通过不同的导电结构分别由第一面和第二面引出中介层,可以有效简化电容的结构,降低其制备难度,有助于提高电容的电容量,优化该半导体封装结构的性能。

42、本公开的构造以及它的其他发明目的及有益效果将会通过结合附图而对优选实施例的描述而更加明显易懂。

- 还没有人留言评论。精彩留言会获得点赞!