一种共栅共源型多通道氮化镓HEMT器件及制造方法与流程

一种共栅共源型多通道氮化镓hemt器件及制造方法

技术领域

1.本发明涉及半导体功率器件领域,具体涉及一种共栅共源型多通道氮化镓hemt器件及制造方法。

背景技术:

2.algan/gan异质结场效应晶体管(hetero-junction field effect transisitor,hfet)也称高电子迁移率晶体管(high electron mobility transisitor,hemt),又称二维电子气场效应管(two dimensional electron gas field effect transisitor,2-degfet)。由于二维电子气(2-deg)的存在,常规hemt器件均为耗尽型(常开型)。器件工作时,通过外加偏置电压来调制二维电子气的浓度和迁移率,偏置电压不同,器件有不同的工作状态。栅源极偏压vgs控制器件的开启和关断,漏源电压vds形成横向电场,使二维电子气沿沟道输运形成源漏电流ids。

3.氮化镓(gan)半导体器件因其宽频带隙和高击穿场在高压领域的应用得到了广泛的关注,而能够实现3kv以上高耐压的gan器件都是耗尽型(d-mode)hemt,具有较高的导通电阻r

on

。且常开耗尽型器件在实际应用中会带来较多问题。由于器件常开,需要给器件施加负电压使得器件保持关断,这导致在器件不使用的期间增加额外的功耗,引起能源的浪费。

技术实现要素:

4.有鉴于此,本发明提供了一种共栅共源型多通道氮化镓hemt器件和制造方法,采用了d-mode的多通道gan/algan异质结结构有效地降低导通电阻r

on

,并通过e-mode栅极控制对其进行控制。

5.为达上述目的,本发明采用了如下技术方案:

6.一种共栅共源型多通道氮化镓hemt器件,包括:衬底基板、缓冲层、第一异质结结构、第二异质结结构、第一电极、金属连接部、第二电极和栅电极。

7.所述缓冲层位于衬底基板一侧,所述第一异质结结构及第二异质结结构位于所述缓冲层远离所述衬底基板一侧,所述第一异质结结构包括至少一个algan/gan异质结,所述第二异质结结构包括多个沿第一方向叠加的algan/gan异质结,其中第一方向为垂直于所述衬底基板方向。

8.所述第一电极与所述第一异质结结构一端连接;所述金属连接部与所述第一异质结结构另一端连接,且与所述第二异质结结构的一端连接;所述第二电极与所述第二异质结结构的另一端连接;所述栅电极位于所述第一异质结结构远离所述衬底基板的一侧。

9.由于二维电子气导电沟道较薄,algan/gan异质结构通常显示出较高的串联电阻。因此采用多通道结构,垂直堆叠了多个algan/gan异质结,以形成多个平行的二维电子气导电沟道,以减小串联电阻。

10.进一步的,所述栅电极与所述第一异质结结构之间设有第一p型掺杂gan层。

11.进一步的,所述第二异质结结构远离所述衬底基板的一侧设有第二p型掺杂gan

层。

12.进一步的,所述第一异质结结构在所述衬底基板上的投影与所述第二异质结结构在所述衬底基板上的投影不交叠。

13.本发明中通过将增强型hemt器件和耗尽型hemt器件组合起来,使得耗尽型hemt器件具有增强型hemt器件的常关性能,还具有简化的栅极驱动。同时,可以实现低压的增强型hemt器件在高压下工作,在器件关闭时高压主要降落在耗尽型hemt器件两端,并且通过串联的增强型hemt器件实现在零偏压下器件处于关闭状态,有效提高增强型hemt器件的可靠性。

14.进一步的,所述第一异质结结构远离所述衬底基板的一侧还包括algan掺杂层,所述algan掺杂层在所述衬底基板上的投影与所述栅电极在所述衬底基板上的投影不交叠;所述algan掺杂层远离所述衬底基板的一侧包括第三电极。

15.进一步的,所述algan掺杂层包括p型掺杂区和n型掺杂区;所述p型掺杂区与所述第三电极连接,所述n型掺杂区与所述金属连接部连接。

16.进一步的,所述第一电极与所述第三电极电连接。通过在栅极区采用结场板,以提高p-gan栅极区的击穿电压。

17.同时,本发明还公开了一种共栅共源型多通道氮化镓hemt器件的制造方法,包括以下步骤:

18.提供衬底基板。

19.在所述衬底基板上生长gan缓冲层,所述gan缓冲层包括第一表面,所述第一表面为所述gan缓冲层远离所述衬底基板的一侧表面。

20.在所述第一表面上沿第一方向依次生长形成n层algan/gan异质结结构,其中第一方向为垂直于所述衬底基板方向。

21.对所述n层algan/gan异质结结构进行选择性刻蚀,以形成第一异质结结构和第二异质结结构,其中,所述第一异质结结构包括至少一个algan/gan异质结,所述第二异质结结构包括n个沿第一方向叠加的algan/gan异质结。

22.在algan/gan异质结结构远离所述衬底基板的一侧外延p型掺杂gan层。

23.对所述p型掺杂gan层进行选择刻蚀以形成第一p型掺杂gan层和第二p型掺杂gan层,所述第一p型掺杂gan层位于所述第一异质结结构远离所述衬底基板的一侧,所述第二p型掺杂gan层位于所述第二异质结结构远离所述衬底基板的一侧。

24.沉积第一电极、第二电极、金属连接部和栅电极,其中,所述第一电极与所述第一异质结结构一端连接,所述金属连接部与所述第一异质结结构另一端连接,且与所述第二异质结结构的一端连接,所述第二电极与所述第二异质结结构的另一端连接,所述栅电极位于所述第一p型掺杂gan层远离所述衬底基板的一侧。

25.进一步的,在所述沉积第一电极、第二电极、金属连接部和栅电极的步骤之前,还包括以下步骤:

26.在所述第一异质结结构远离所述衬底基板的一侧表面选择性外延p型掺杂algan层,所述p型掺杂algan层在所述衬底基板上的投影与所述第一p型掺杂gan层在所述衬底基板上的投影不交叠。

27.在所述p型掺杂algan层上选择性离子注入,得到n型掺杂区,所述n型掺杂区位于

所述p型掺杂algan层远离所述栅电极的一侧。

28.进一步的,所述沉积第一电极、第二电极、金属连接部和栅电极的步骤,还包括:

29.同时在所述p型掺杂algan层远离所述衬底基板的一侧沉积第三电极,所述第三电极在所述衬底基板上的投影与所述n型掺杂区在所述衬底基板上的投影不交叠,并将所述第一电极和所述第三电极进行电连接。

30.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所指出的结构来实现和获得。

附图说明

31.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

32.图1示出了本发明一实施例提供的一种共栅共源型多通道氮化镓hemt器件示意图;

33.图2示出了本发明另一实施例提供的一种共栅共源型多通道氮化镓hemt器件示意图;

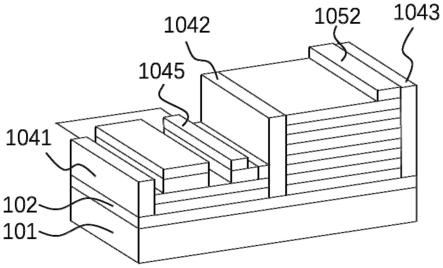

34.图3示出了本发明一实施例提供的一种共栅共源型多通道氮化镓hemt器件立体示意图;

35.图4示出了本发明一实施例提供的一种共栅共源型多通道氮化镓hemt器件制造方法步骤示意图;

36.图5示出了本发明另一实施例提供的一种共栅共源型多通道氮化镓hemt器件制造方法步骤示意图。

具体实施方式

37.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地说明,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.需要说明的是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”、“若干个”的含义是两个或两个以上,除非另有明确具体的限定。

39.本发明中的术语“和/或”,仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,单独存在b,和同时存在a和b这三种情况。显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。

40.通常情况下,algan的禁带宽度为3.95ev,而gan的禁带宽度为3.4ev,由于algan和gan禁带宽度的不同,这两种材料构成的接触面形成了异质结,异质结接触面处半导体材料

费米能级突变,电子会从algan向gan方向转移,而电子的转移使异质结接触面处的电场发生变化,algan失去电子形成耗尽层,阻止距离异质结较远的电子的运动,而gan的电子势能较低,会束缚电子、驱赶空穴,在异质结接触面的gan半导体材料一侧形成存在自由电子的势阱区域,从而随着自由电子在势阱中的积累,形成二维电子气(two dimensional electron gas,2deg),二维电子气受到两侧半导体的约束,只能在平行于异质结接触面的方向移动。由于二维电子气脱离了提供它的algan进入gan,不再收到电离杂质散射作用控制,因而呈现出很高的电子迁移率。具有高电子迁移率的二维电子气,可以在异质结面上高速移动,从而构成导电沟道,因此此类氮化镓功率器件也被称为氮化镓hemt(high electron mobility transistor,高电子迁移率晶体管)。

41.本发明提供了一种共栅共源型多通道氮化镓hemt器件100,图1为本发明实施例提供的一种共栅共源型多通道氮化镓hemt器件示意图,如图1所示,包括:衬底基板101、缓冲层102、异质结结构层103和金属电极层104。其中所述异质结结构层103包括第一异质结结构1031和第二异质结结构1032,所述金属电极层104包括第一电极1041、金属连接部1042、第二电极1043和栅电极1044。

42.所述缓冲层102位于衬底基板101一侧,所述第一异质结结构1031及第二异质结结构1032位于所述缓冲层102远离所述衬底基板101一侧,所述第一异质结结构1031包括至少一个algan/gan异质结,所述第二异质结结构1032包括多个沿第一方向叠加的algan/gan异质结,其中第一方向为垂直于所述衬底基板101的方向。

43.所述第一电极1041与所述第一异质结结构1031一端连接;所述金属连接部1042与所述第一异质结结构1031另一端连接,且与所述第二异质结结构1032的一端连接;所述第二电极1043与所述第二异质结结构1032的另一端连接;所述栅电极1044位于所述第一异质结结构1031远离所述衬底基板101的一侧。

44.由于二维电子气导电沟道较薄,algan/gan异质结构通常显示出较高的串联电阻。因此采用多通道结构,垂直堆叠了多个algan/gan异质结,以形成多个平行的二维电子气导电沟道,以减小串联电阻。

45.进一步的,所述栅电极1044与所述第一异质结结构1031之间设有第一p型掺杂gan层1051。所述第一p型掺杂gan层1051可以拉升algan层的势垒高度提升至费米能级之上,是原来处于三角形势阱内的二维电子气耗尽,从而实现增强型。当栅电极1044加正压时,沟道的电势会逐渐下降,当下降到费米能级以下时,沟道逐渐开启,器件逐渐导通,源漏电流逐渐增大。也即第一异质结结构1031所在的区域,可以通过控制栅电极上的电压来控制器件的开通关断,相当于增强型(e-mode)hemt器件。

46.进一步的,所述第二异质结结构1032远离所述衬底基板101的一侧设有第二p型掺杂gan层1052。所述第二p型掺杂gan层1052的一端与所述第二电极1043接触,能够均匀漏极区的电场,提升漏极区的击穿电压。

47.作为一种优选的实施方式,所述第一p型掺杂gan层1051和所述第二p型掺杂gan层1052同层同材料,此处的同层指的是同一工艺步骤制备。

48.第二异质结结构1032所在的区域,相当于耗尽型(d-mode)hemt器件。本发明中通过将增强型hemt器件和耗尽型hemt器件组合起来,使得耗尽型hemt器件具有增强型hemt器件的常关性能,还具有简化的栅极驱动。同时,可以实现低压的增强型hemt器件在高压下工

作,在器件关闭时高压主要降落在耗尽型hemt器件两端,并且通过串联的增强型hemt器件实现在零偏压下器件处于关闭状态,有效提高增强型hemt器件的可靠性。

49.进一步的,所述第一异质结结构1031在所述衬底基板101上的投影与所述第二异质结结构1032在所述衬底基板101上的投影不交叠。

50.进一步的,图2为本发明另一实施例提供的一种共栅共源型多通道氮化镓hemt器件示意图,如图2所示,所述第一异质结结1031构远离所述衬底基板101的一侧还包括algan掺杂层106,所述algan掺杂层106在所述衬底基板101上的投影与所述栅电极1044在所述衬底基板101上的投影不交叠;所述algan掺杂层106远离所述衬底基板101的一侧包括第三电极1045。

51.进一步的,所述algan掺杂层106包括p型掺杂区和n型掺杂区;所述p型掺杂区与所述第三电极1045连接,所述n型掺杂区与所述金属连接部1042连接。

52.进一步的,图3为本发明一实施例提供的一种共栅共源型多通道氮化镓hemt器件立体示意图。如图3所示,所述第一电极1041与所述第三电极1045电连接,通过在栅极区采用结场板,以提高p-gan栅极区的击穿电压。

53.下面介绍以下本发明提供的一种共栅共源型多通道氮化镓hemt器件的导通方式。

54.当第二电极1043端施加正向电压,栅电极1044端施加正向电压时,器件在栅电极1044下端积累电子,器件处于开启状态;当第二电极1043端施加正向电压,栅电极1044端处于零偏压状态时,器件处于关断状态,通过多通道高耐压的耗尽型hemt结构和异质结场板共同承担反向电压,保护栅极不受高电场的影响。

55.可以理解的是,在半导体器件的结构设计中,可以控制器件的长宽高以及掺杂浓度等设计参数来提升半导体器件的性能。

56.图4为本发明一实施例提供的一种共栅共源型多通道氮化镓hemt器件制造方法步骤示意图。如图4所示,本发明还提供了一种共栅共源型多通道氮化镓hemt器件的制造方法,包括以下步骤:

57.提供衬底基板101。

58.在所述衬底基板101上生长gan缓冲层102,所述gan缓冲层102包括第一表面,所述第一表面为所述gan缓冲层102远离所述衬底基板101的一侧表面。

59.在所述第一表面上沿第一方向依次生长形成n层algan/gan异质结结构,其中第一方向为垂直于所述衬底基板方向。

60.对所述n层algan/gan异质结结构进行选择性刻蚀,以形成第一异质结结构1031和第二异质结结构1032,其中,所述第一异质结结构1031包括至少一个algan/gan异质结,所述第二异质结结构1032包括n个沿第一方向叠加的algan/gan异质结。作为一种可选的结构,所述第一异质结结构1031仅包括一个algan/gan异质结。

61.在algan/gan异质结结构远离所述衬底基板101的一侧外延p型掺杂gan层105。

62.对所述p型掺杂gan层105进行选择刻蚀以形成第一p型掺杂gan层1051和第二p型掺杂gan层1052,所述第一p型掺杂gan层1051位于所述第一异质结结构1031远离所述衬底基板101的一侧,所述第二p型掺杂gan层1052位于所述第二异质结结构1032远离所述衬底基板101的一侧。

63.沉积第一电极1041、第二电极1043、金属连接部1042和栅电极1044,其中,所述第

一电极1041与所述第一异质结结构1031一端连接,所述金属连接部1042与所述第一异质结结构1031另一端连接,且与所述第二异质结结构1032的一端连接,所述第二电极1043与所述第二异质结结构1043的另一端连接,所述栅电极1044位于所述第一p型掺杂gan层1051远离所述衬底基板101的一侧。

64.本发明中通过将增强型hemt器件和耗尽型hemt器件组合起来,使得耗尽型hemt器件具有增强型hemt器件的常关性能,还具有简化的栅极驱动。同时,可以实现低压的增强型hemt器件在高压下工作,在器件关闭时高压主要降落在耗尽型hemt器件两端,并且通过串联的增强型hemt器件实现在零偏压下器件处于关闭状态,有效提高增强型hemt器件的可靠性。

65.图5示出了本发明另一实施例提供的一种共栅共源型多通道氮化镓hemt器件制造方法步骤示意图。进一步的,如图5所示,在所述沉积第一电极1041、第二电极1043、金属连接部1042和栅电极1044的步骤之前,还包括以下步骤:

66.在所述第一异质结结构1031远离所述衬底基板101的一侧表面选择性外延p型掺杂algan层1061,所述p型掺杂algan层1061在所述衬底基板101上的投影与所述第一p型掺杂gan层1061在所述衬底基板101上的投影不交叠。

67.在所述p型掺杂algan层1061上选择性离子注入,得到n型掺杂区1062,所述n型掺杂区1062位于所述p型掺杂algan层1061远离所述栅电极1044的一侧。

68.进一步的,所述沉积第一电极1041、第二电极1043、金属连接部1042和栅电极1044的步骤,还包括:

69.同时在所述p型掺杂algan层1061远离所述衬底基板101的一侧沉积第三电极1045,所述第三电极1045在所述衬底基板101上的投影与所述n型掺杂区1062在所述衬底基板上的投影不交叠,将所述第一电极1041和所述第三电极1045进行电连接。通过在栅极区采用结场板,以提高p-gan栅极区的击穿电压。

70.本发明实施例还提供一种电子设备,包括如上述的共栅共源型多通道氮化镓hemt器件。

71.电子设备的半导体器件为上述的共栅共源型多通道氮化镓hemt器件时,通过多通道高耐压d-mode结构和异质结场板共同承担反向电压,保护栅极不受高电场的影响,可以有效提升半导体器件的工作可靠性。

72.该电子设备可以是终端,也可以为除终端之外的其他设备。示例性的,电子设备可以为手机、平板电脑、笔记本电脑、掌上电脑、车载电子设备、移动上网装置(mobile internet device,mid)、增强现实(augmented reality,ar)/虚拟现实(virtual reality,vr)设备、机器人、可穿戴设备、超级移动个人计算机(ultra-mobile personal computer,umpc)、上网本或者个人数字助理(personal digital assistant,pda)等,还可以为服务器、网络附属存储器(network attached storage,nas)、个人计算机(personal computer,pc)、电视机(television,tv)、柜员机或者自助机等,本发明实施例不作具体限定。

73.尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1