带有P+沟槽结构的碳化硅MOSFET器件及制作方法与流程

本公开涉及芯片制造,尤其涉及带有p+沟槽结构的碳化硅mosfet器件及制作方法。

背景技术:

1、sic mosfet具有低导通电阻、开关速度快、耐高温等特点,在高压变频、新能源汽车、轨道交通等领域具有巨大的应用优势。

2、为提高sic mosfet电流能力,常通过自对准工艺技术缩减沟道长度。沟道自对准工艺中,当p+源极区域不进行掩膜保护时,由于源极n+注入区域表面浓度高,p+源极注入后,较低的p型离子激活率使得p+有效掺杂浓度降低,导致补偿后的p+区域掺杂浓度进一步下降,不利于p+源极欧姆接触,源电极与p-base之间的存在基区压降差,在导通状态下容易导致寄生npn晶体管误开启。当在沟道自对准工艺中对p+源极区域进行掩膜保护时,则在进行p+注入时,需去除自对准掩膜,重新对源极p+进行光刻。额外的光刻工艺步骤引入了p+的对准偏差,特别是在小尺寸元胞中,影响n+源极的接触面积的均匀性和元胞内电流流通的均匀性,增加了失效风险。

技术实现思路

1、有鉴于此,本公开实施例提供了带有p+沟槽结构的碳化硅mosfet器件及制作方法,以解决现有技术中不进行掩膜保护时易导致npn晶体管误开启,进行掩膜保护时偏差较大的问题。

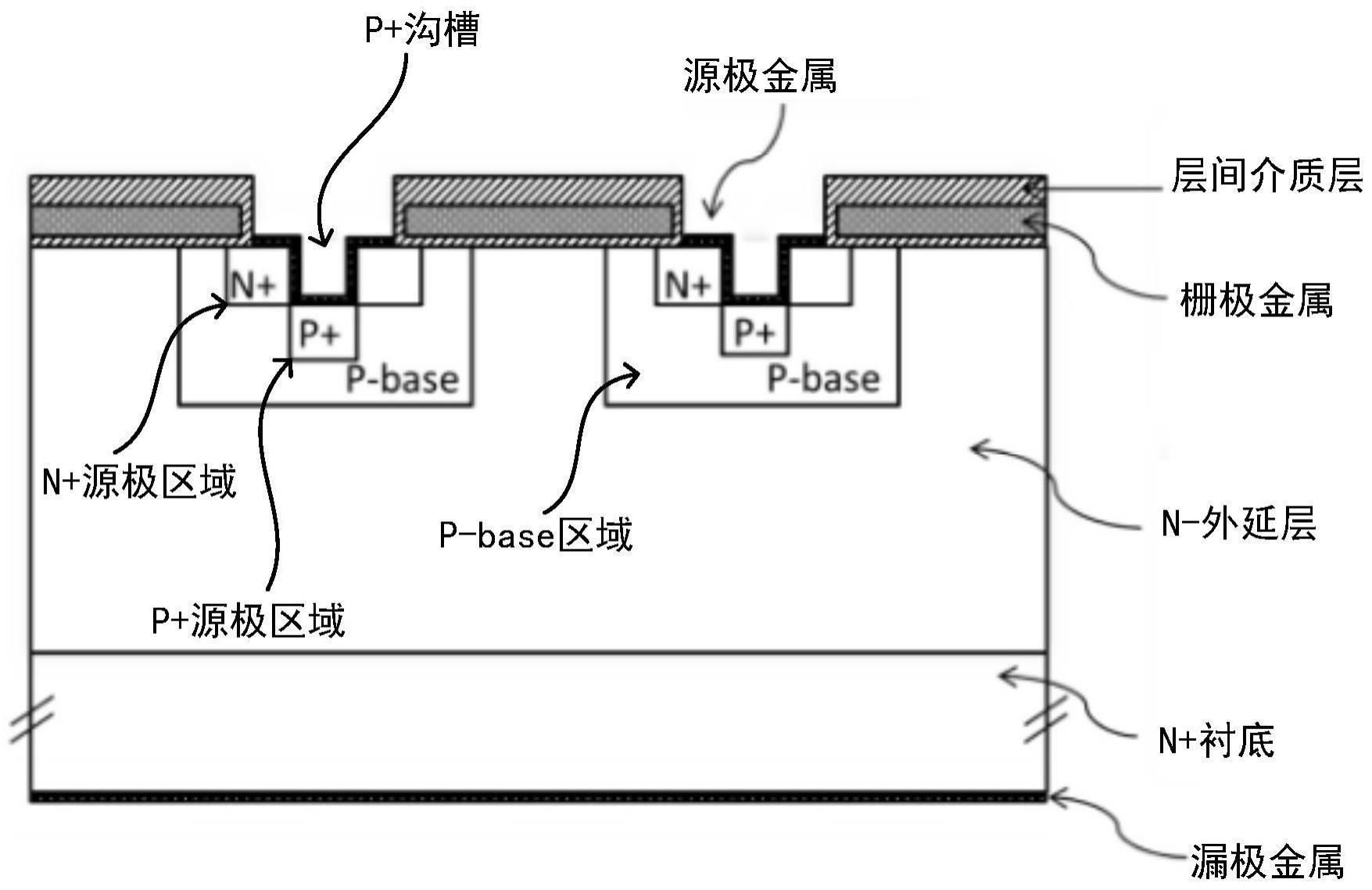

2、本公开实施例的第一方面,提供了一种带有p+沟槽结构的碳化硅mosfet器件,该带有p+沟槽结构的碳化硅mosfet器件包括并联的多个带有p+沟槽结构的碳化硅mosfet器件元胞,且这些碳化硅mosfet器件元胞是均匀排列的,所述带有p+沟槽结构的碳化硅mosfet器件元胞包括:

3、所述碳化硅n-外延层远离所述碳化硅n+衬底一侧内部形成有两个对称设置的p-base区域;

4、所述p-base区域远离所述碳化硅n+衬底一侧内部形成有通过自对准技术形成的n+源极区域,所述n+源极区域内部形成有p+沟槽;所述p+沟槽的底部下方形成有p+源极区域;

5、所述碳化硅n-外延层远离所述碳化硅n+衬底一侧形成有层间绝缘介质,所述层间绝缘介质内设有栅极金属,所述层间绝缘介质设有与所述p-base区域对应的源极开孔,所述源极开孔的宽度小于所述n+源极区域的宽度;

6、所述p+沟槽的侧壁和底部,以及所述源极开孔的底部设有均匀厚度的源极金属。

7、在一些实施例中,所述p+沟槽的深度小于或等于所述n+源极区域的深度。

8、本公开实施例的第二方面,提供了一种带有p+沟槽结构的碳化硅mosfet器件元胞的制作方法,包括:

9、获取碳化硅晶圆,所述碳化硅晶圆包括碳化硅n+衬底和设于所述碳化硅n+衬底上方的碳化硅n-外延层;

10、在所述碳化硅n-外延层远离所述碳化硅n+衬底一侧内部形成两个对称设置的p-base区域,在所述p-base区域内形成n+源极区域和p+沟槽,并在所述p+沟槽下方形成p+源极区域;

11、淀积栅氧化层,淀积多晶硅并图形化生成栅极电极,淀积层间绝缘介质,基于预设的第一宽度刻蚀所述栅氧化层、栅极电极和层间绝缘介质,得到源极开孔;

12、在所述p+沟槽的侧壁和底部,以及所述源极开孔的底部淀积源极金属,在碳化硅n+衬底的背部淀积漏极金属,得到所述带有p+沟槽结构的碳化硅mosfet器件元胞。

13、在一些实施例中,所述在所述碳化硅n-外延层远离所述碳化硅n+衬底一侧内部形成两个对称设置的p-base区域,在所述p-base区域内形成p+沟槽和基于自对准技术形成的n+源极区域,并在所述p+沟槽下方形成p+源极区域,包括:

14、在所述碳化硅n-外延层上方形成一层垫氧层;

15、在所述垫氧层上方淀积第一掩膜层,以所述垫氧层作为刻蚀截止层,基于预设的第二宽度刻蚀所述第一掩膜层得到p-base注入窗口,利用所述第一掩膜层作为离子注入掩膜注入p型离子,形成两个对称设置的p-base区域;

16、在所述p-base区域上方淀积第二掩膜层,基于预设的第三宽度刻蚀所述第二掩膜层得到第一掩膜侧墙,利用所述第一掩膜侧墙作为离子注入掩膜注入n型离子,形成两个对称设置的n+源极区域,以及与所述第一掩膜侧墙厚度相同的自对准沟道;

17、在所述n+源极区域上方淀积第三掩膜层,基于预设的第三厚度刻蚀所述第三掩膜层得到第二掩膜侧墙,利用所述第一掩膜层、所述第一掩膜侧墙和所述第二掩膜侧墙作为掩膜,对所述n+源极区域进行刻蚀,得到p+沟槽;

18、在所述p+沟槽的侧壁和底部生成热氧化层,利用所述第一掩膜层、所述第一掩膜侧墙和所述第二掩膜侧墙作为离子注入掩膜,注入p型离子得到p+源极区域,所述p+沟槽的侧壁的热氧化层用于阻挡离子注入散射;

19、去除所述垫氧层、第一掩膜层、所述第一掩膜侧墙、所述第二掩膜侧墙和所述热氧化层,并执行退火工艺。

20、在一些实施例中,所述在所述碳化硅n-外延层远离所述碳化硅n+衬底一侧内部形成两个对称设置的p-base区域,在所述p-base区域内形成p+沟槽和基于自对准技术形成的n+源极区域,并在所述p+沟槽下方形成p+源极区域,包括:

21、在所述碳化硅n-外延层上方形成一层垫氧层;

22、在所述垫氧层上方淀积第一掩膜层,以所述垫氧层作为刻蚀截止层,基于预设的第二宽度刻蚀所述第一掩膜层得到p-base注入窗口,利用所述掩膜层作为离子注入掩膜注入p型离子,形成两个对称设置的p-base区域;

23、在所述p-base区域上方淀积第二掩膜层,基于预设的第三宽度刻蚀所述第二掩膜层得到第一掩膜侧墙,利用所述第一掩膜侧墙作为离子注入掩膜注入n型离子,形成两个对称设置的n+源极区域,以及与所述第一掩膜侧墙厚度相同的自对准沟道;

24、在所述n+源极区域上方淀积第三掩膜层,基于预设的第三厚度刻蚀所述第三掩膜层得到第二掩膜侧墙,利用所述第一掩膜层、所述第一掩膜侧墙和所述第二掩膜侧墙作为离子注入掩膜,注入预先调节好的p型离子组合,形成p+1区域和处于所述p+1区域下部的p+2区域,所述p+1区域和p+2区域的间隔面高于所述n+源极区域的底面,所述p+1区域的离子浓度低于所述p+2区域的离子浓度;

25、利用所述第一掩膜层、所述第一掩膜侧墙和所述第二掩膜侧墙作为刻蚀掩膜,对所述p+1区域和所述p+2区域进行刻蚀,控制刻蚀时长以使刻蚀形成的p+沟槽的深度大于所述p+1区域的深度,得到p+源极区域;

26、去除所述第一掩膜层、所述第一掩膜侧墙、所述第二掩膜侧墙和所述热氧化层,并执行退火工艺;

27、对所述碳化硅晶圆进行热氧化处理,消耗预设厚度范围的n+源极区域和p+源极区域,以去除p+注入散射对n+源极区域侧壁浓度的影响。

28、在一些实施例中,所述第一掩膜层、所述第二掩膜层、所述第三掩膜层的制作材料为氮化硅或氮化铝。

29、在一些实施例中,所述垫氧层的厚度范围为50纳米至100纳米。

30、在一些实施例中,所述p+沟槽的深度范围为0.25微米至0.5微米。

31、在一些实施例中,所述热氧化层的厚度范围为50纳米至100纳米。

32、在一些实施例中,所述带有p+沟槽结构的碳化硅mosfet器件元胞的制作方法还包括:

33、对所述碳化硅晶圆的正面和背面的金属进行加厚。

34、有益效果

35、本公开实施例与现有技术相比存在的有益效果至少包括:通过形成的n+源极和p+源极,使得源极与p-base形成短接,抑制寄生npn效应,同时又提高p+源极的精度,避免元胞内的不均流现象,提高器件的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!