CMOS电路结构、阵列、非门结构、工艺方法及设备与流程

本技术实施例涉及半导体技术,尤指一种cmos电路结构、阵列、非门结构、工艺方法及设备。

背景技术:

1、非门是逻辑电路中的基本单元,当非门输入端为高电平时输出为低电平,反之,输入端为低电平时输出为高电平;当前逻辑电路中,非门的设计有两种,一种是coms(complementary metal oxide semiconductor,互补金属氧化物半导体)逻辑,一种ttl(transistor transistor logic,晶体管-晶体管逻辑)逻辑。其中,cmos逻辑的非门器件结构利用平面结构,使得pmos(p型金属氧化物半导体)和nmos(n型金属氧化物半导体)并联,来实现非门的逻辑功能。

技术实现思路

1、本技术实施例提供了一种cmos电路结构、阵列、非门结构、工艺方法及设备,能够降低占地面积,提高器件集成度。

2、本技术实施例提供了一种cmos电路结构,可以包括位于衬底上的第一晶体管和第二晶体管,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管;

3、所述第一晶体管包括依次叠层的第一源极、第一半导体层和第一漏极;

4、所述第二晶体管包括依次叠层的第二源极、第二半导体层和第二漏极;

5、所述第一晶体管和所述第二晶体管叠层而置;

6、所述第一晶体管和所述第二晶体管分别为垂直沟道晶体管。

7、在本技术的示例性实施例中,所述的cmos电路结构包括贯穿所述第一源极、第一半导体层,第一漏极,以及贯穿所述第二源极、第二半导体层,第二漏极的第一通孔,所述第一通孔内形成有导电线,所述导电线对应于所述第一半导体层的区域为所述第一晶体管的第一栅极,且对应于所述第二半导体层的区域为所述第二晶体管的第二栅极。

8、在本技术的示例性实施例中,所述衬底为硅衬底;

9、所述第一源极、第一半导体层,第一漏极分别为硅或锗硅外延层,所述第一源极和第一漏极分别为n型重掺杂外延层,所述第一半导体层为p型掺杂外延层;

10、所述第二源极、第二半导体层,第二漏极分别为硅或锗硅外延层,所述第二源极和第二漏极分别为p型重掺杂外延层,所述第二半导体层为n型掺杂外延层。

11、在本技术的示例性实施例中,所述第一半导体层位于所述衬底和所述第二半导体层之间;

12、所述第一漏极与所述硅衬底接触,所述硅衬底与第一参考电压连接;

13、所述第二栅极的顶端与cmos电路的输入端连接;

14、所述第一源极对应的n型重掺杂外延层与所述第二源极对应的p型重掺杂外延层连接且同时与cmos电路的输出端连接。

15、在本技术的示例性实施例中,所述的cmos电路结构还可以包括贯穿所述第二源极、第二漏极到所述第一源极的第二通孔,所述第二通孔内填充有与输出端连接的引线,所述引线与所述第二源极绝缘且与所述第一源极对应的n型重掺杂外延层接触,与所述第二漏极对应的p型重掺杂外延层接触。

16、本技术实施例还提供了一种cmos阵列,包括多个所述的cmos电路结构,同一个cmos电路中的所述第一通孔和第二通孔相邻且沿着行方向排列;不同cmos电路中的所述第一通孔沿着列方向排列,不同cmos电路中的所述第二通孔沿着列方向排列,且多列第一通孔和多列第二通孔交替分布。

17、本技术实施例还提供了一种非门器件的结构,所述非门器件基于所述的cmos电路结构,所述非门器件可以包括一个p型金属氧化物半导体pmos和一个n型金属氧化物半导体nmos;所述非门器件的结构包括:pmos、nmos以及设置于所述pmos和所述nmos内的输入端结构、输出端结构和公共连接端结构;

18、其中,所述pmos和所述nmos垂直堆叠。

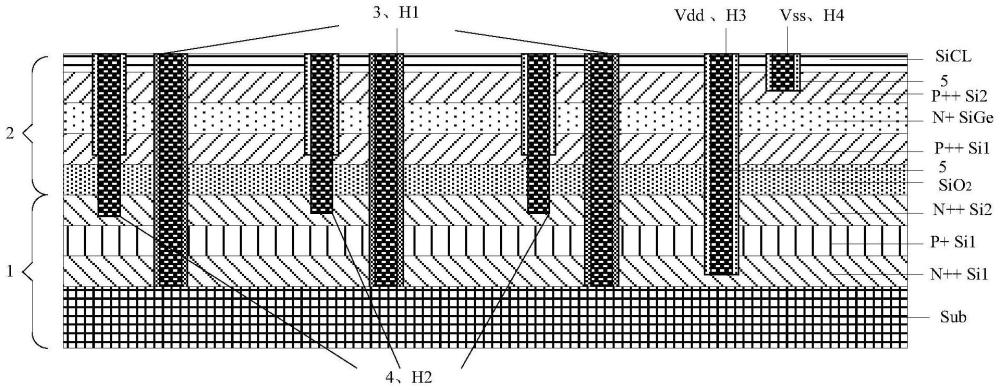

19、在本技术的示例性实施例中,所述nmos设置于底层,所述pmos设置于所述nmos上方;所述nmos,可以包括:

20、硅衬底;

21、设置于所述衬底上的第一层重掺杂的n型si(n++si1);

22、设置于所述第一层重掺杂的n型si(n++si1)上的第一层掺杂的p型si(p+si1);以及,

23、设置于所述第一层掺杂的p型si(p+si1)上的第二层重掺杂的n型si(n++si2)。

24、在本技术的示例性实施例中,所述pmos,可以包括:

25、设置于所述第二层重掺杂的n型si(n++si2)上的第一层重掺杂的p型si(p++si1);

26、设置于所述第一层重掺杂的p型si(p++si1)上的一层n掺杂的sige(n+sige);

27、设置于所述n掺杂的sige(n+sige)上的第二层重掺杂的p型si(p++si2);以及,

28、设置于所述第二层重掺杂的p型si(p++si2)上的覆盖层。

29、在本技术的示例性实施例中,所述pmos,还可以包括:

30、设置于所述第二层重掺杂的n型si和所述第一层重掺杂的p型si之间一层硅氧化物。

31、在本技术的示例性实施例中,所述输入端结构,可以包括:

32、第一通孔的内壁上设置的一层高k介质;其中,所述第一通孔贯穿所述覆盖层、所述第二层重掺杂的p型si、所述n掺杂的sige、所述第一层重掺杂的p型si、所述第二层重掺杂的n型si、所述第一层掺杂的p型si以及所述第一层重掺杂的n型si;以及,

33、设置该高k介质后的第一通孔内填充的导电线作为栅极。

34、在本技术的示例性实施例中,所述输出端结构,可以包括:

35、第二通孔的从所述覆盖层的上表面到所述第一层重掺杂的p型si(p++si1)之间的内壁上设置的一层硅氧化物;其中,所述第二通孔贯穿所述覆盖层、所述第二层重掺杂的p型si、所述n掺杂的sige、所述第一层重掺杂的p型si,所述第二通孔的底层位于所述第二层重掺杂的n型si内;以及,

36、设置所述硅氧化物以后的第二通孔内填充的接触金属;其中,所述第二通孔的从所述第一层重掺杂的p型si(p++si1)到所述第二层重掺杂的n型si(n++si2)之间的内径等于所填充的接触金属的内径。

37、在本技术的示例性实施例中,所述公共连接端可以包括:第一公共电源vdd端和第二公共电源vss端;所述公共连接端结构,可以包括:所述第一公共电源vdd端的结构和所述第二公共电源vss端的结构;

38、所述第一公共电源vdd端的结构,包括:

39、在第三通孔的内壁上设置的一层硅氧化物;以及,

40、在设置所述硅氧化物后的第三通孔内填充的接触金属;

41、其中,所述第三通孔位于每一行非门器件对应的pmos和nmos的一端;所述第三通孔贯穿所述覆盖层、所述第二层重掺杂的p型si、所述n掺杂的sige、所述第一层重掺杂的p型si、所述第二层重掺杂的n型si和所述第一层掺杂的p型si,所述第三通孔的底端位于所述第一层重掺杂的n型si内;

42、所述第二公共电源vss端的结构,包括:

43、在第四通孔的内壁上设置的一层硅氧化物;以及,

44、在设置所述硅氧化物后的第四通孔内填充的接触金属;

45、其中,所述第四通孔位于每一行非门器件对应的pmos和nmos的一端;所述第四通孔贯穿所述覆盖层,所述第四通孔的底端位于所述第二层重掺杂的p型si内。

46、本技术实施例还提供了一种非门器件的结构的工艺方法,基于所述的非门器件的结构;所述方法可以包括:

47、将所述结构中的pmos和nmos垂直堆叠;

48、在所述pmos和所述nmos内设置所述结构中的输入端结构、输出端结构和公共连接端结构,实现所述非门器件的结构设置。

49、在本技术的示例性实施例中,在所述pmos和所述nmos内设置所述输入端结构,可以包括:

50、采用刻蚀技术,从所述pmos上方的覆盖层的上表面竖直向下刻蚀,在所述pmos和所述nmos上刻蚀出多条沟道,通过所述多条沟道将所述pmos和所述nmos划分为多行;

51、采用刻蚀技术,从所述覆盖层的上表面竖直向下刻蚀,在每行pmos和nmos上按照预设间距刻蚀出多个第一通孔,每个第一通孔的底端为所述衬底的上表面;每个第一通孔对应一个非门器件;

52、当所述nmos和所述pmos之间设置有牺牲层时,去除所述牺牲层,并在去除所述牺牲层后的空间内以及所述多条沟道内填充硅氧化物,将每个第一通孔内的硅氧化物刻蚀掉;在每个第一通孔的内壁上设置一层高k介质;所述高k介质是指介电常数高于预设的介电常数阈值的介质;当所述nmos和所述pmos之间未设置有牺牲层时,直接在每个第一通孔的内壁上设置一层高k介质;

53、在设置有该高k介质后的第一通孔内填充作为栅极的导电线。

54、在本技术的示例性实施例中,在所述pmos和所述nmos内设置所述输出端结构,可以包括:

55、采用刻蚀技术,从所述pmos上方的覆盖层的上表面竖直向下刻蚀,在每行pmos和nmos上刻蚀出多个第二通孔,直至刻蚀到所述第一层重掺杂的p型si(p++si1)内;

56、在每个第二通孔的内壁上沉积一层硅氧化物;

57、采用刻蚀技术,以所述第二通孔的内壁上沉积所述硅氧化物以后的剩余空间的内径作为内径,继续将每个第二通孔沿竖直向下方向刻蚀,直至刻蚀到所述第二层重掺杂的n型si(n++si2)内;

58、在每个第二通孔内填充接触金属,完成所述输出端结构的设置。

59、在本技术的示例性实施例中,所述公共连接端可以包括:第一公共电源vdd端和第二公共电源vss端;所述公共连接端结构,可以包括:所述第一公共电源vdd端的结构和所述第二公共电源vss端的结构;在所述pmos和所述nmos内设置所述公共连接端结构,可以包括:

60、采用刻蚀技术,从所述pmos上方的覆盖层的上表面竖直向下刻蚀,在每一行所述pmos和所述nmos中一端的pmos和nmos内刻蚀出第三通孔和第四通孔;每个第三通孔的底端位于所述第一层重掺杂的n型si(n++si1)内;每个第四通孔的底端位于所述第二层重掺杂的p型si(p++si2)内;

61、在每个第三通孔和第四通孔的内壁上沉积一层硅氧化物;

62、在沉积所述硅氧化物后的第三通孔和第四通孔内填充接触金属,完成所述公共连接端结构的设置;其中,填充所述接触金属后的第三通孔为所述第一公共电源vdd端的结构,填充所述接触金属后的第四通孔为所述第二公共电源vss端的结构。

63、本技术实施例还提供了一种电子设备,包括所述的cmos电路结构,或包括所述的非门器件的结构。

64、与相关技术相比,本技术实施例的cmos电路结构包括位于衬底上的第一晶体管和第二晶体管,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管;所述第一晶体管包括依次叠层的第一源极、第一半导体层,第一漏极;所述第二晶体管包括依次叠层的第二源极、第二半导体层,第二漏极;所述第一晶体管和所述第二晶体管叠层而置;所述第一晶体管和所述第二晶体管分别为垂直沟道晶体管。通过该实施例方案,大幅度降低了占地面积,提高了器件集成度。

65、本技术的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术而了解。本技术的其他优点可通过在说明书以及附图中所描述的方案来实现和获得。

- 还没有人留言评论。精彩留言会获得点赞!