高电子迁移率晶体管及其制备方法与流程

1.本发明涉及半导体技术领域,特别涉及一种高电子迁移率晶体管及其制备方法。

背景技术:

2.高电子迁移率晶体管(high electron mobility transistor,hemt)是基于异质结中的二维电子气的高迁移率特性的场效应晶体管,其在低温、低电场下具备较高的电子迁移率,可实现高速低噪音工作。

3.目前,hemt器件一般包括耗尽型hemt器件和增强型hemt器件。其中,耗尽型hemt器件在关断时必须在栅电极上施加负电压偏置,这增加了电路的功耗和复杂度,并且降低了系统的安全性。而增强型hemt器件能够降低系统的功耗和复杂度,提升安全性,在高温和射频集成电路、高速开关以及微波单片集成电路中具有广阔的应用前景。

4.现有技术中,增强型hemt器件通常采用p型栅极结构,其具体是在栅电极和势垒层之间引入p型掺杂层。但是p型掺杂层存在受主杂质的钝化效应与自补偿效应,导致p型掺杂层内的离子浓度很低,难以进一步提高器件的阈值电压。

技术实现要素:

5.本发明的目的在于提供一种高电子迁移率晶体管的制备方法,以解决现有的高电子迁移率晶体管的阈值电压难以提升的问题。

6.为解决上述技术问题,本发明提供一种高电子迁移率晶体管的制备方法,包括:在一衬底上依次形成沟道层和势垒层;形成p型掺杂层,所述p型掺杂层形成在所述势垒层上并位于栅极区域内;执行退火工艺,以使所述p型掺杂层中的p型离子至少扩散至所述势垒层中;以及,形成栅电极、源电极和漏电极,所述栅电极形成在所述p型掺杂层上,所述源电极和所述漏电极分别位于所述栅电极的两侧。

7.可选的,所述p型掺杂层中掺杂有镁。

8.可选的,在执行退火工艺之前,所述p型掺杂层中的镁的浓度为5e18cm-3-1e20cm-3

。

9.可选的,执行退火工艺以使所述p型掺杂层中的镁扩散,并促使未电离的镁发生电离。

10.可选的,所述退火工艺包括:退火温度为700℃-1000℃。以及,所述退火工艺还可包括:退火时间为10min-50min。

11.可选的,所述p型掺杂层中的p型离子还扩散至所述沟道层中。

12.本发明还提供了一种高电子迁移率晶体管,包括:沟道层、势垒层和p型掺杂层,依次形成在一衬底上;其中,在所述p型掺杂层下方的所述势垒层中还掺杂有p型离子,并且所述p型掺杂层内的p型离子和所述势垒层中的p型离子相同;以及,栅电极、源电极和漏电极,所述栅电极形成在所述p型掺杂层上,所述源电极和所述漏电极分别位于所述栅电极的两侧。

13.可选的,所述p型掺杂层内的p型离子和所述势垒层中的p型离子均包括镁离子。

14.可选的,所述沟道层中也掺杂有p型离子,所述沟道层中的p型离子和所述p型掺杂层内的p型离子相同。

15.在本发明提供的高电子迁移率晶体管的制备方法中,通过形成p型掺杂层,以实现增强型hemt器件,并进一步利用退火工艺促使p型掺杂层中的p型离子在栅极区域向下扩散至势垒层中,有利于抬高势垒层的势垒,从而提高器件的阈值电压。在此基础上,还有利于增大势垒层中的铝镓氮层内铝的组份,并可进一步增大势垒层的厚度,进而能够降低器件的导通电阻,有效缓解了器件的阈值电压和导通电阻二者相互制约的问题。

附图说明

16.图1为本发明一实施例中的高电子迁移率晶体管的制备方法的流程示意图。

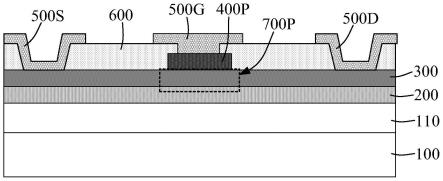

17.图2-图5为本发明一实施例中的高电子迁移率晶体管在其制备过程中的结构示意图。

18.其中,附图标记如下:

19.100-衬底;

20.110-过渡层;

21.200-沟道层;

22.300-势垒层;

23.400p-p型掺杂层;

24.500g-栅电极;

25.500s-源电极;

26.500d-漏电极;

27.600-钝化层;

28.700p-p型离子扩散区。

具体实施方式

29.以下结合附图以及具体实施例对本发明提出的高电子迁移率晶体管及其形成方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需要说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。应当认识到,附图中所示的诸如“上方”,“下方”,“顶部”,“底部”,“上方”和“下方”之类的相对术语可用于描述彼此之间的各种元件的关系。这些相对术语旨在涵盖除附图中描绘的取向之外的元件的不同取向。例如,如果装置相对于附图中的视图是倒置的,则例如描述为在另一元件“上方”的元件现在将在该元件下方。

30.具体参考图1所示的本发明一实施例中的高电子迁移率晶体管的制备方法的流程示意图,本实施例中的高电子迁移率晶体管的制备方法包括如下步骤。

31.步骤s100,在一衬底上依次形成沟道层和势垒层。

32.步骤s200,形成p型掺杂层,所述p型掺杂层形成在所述势垒层上并位于栅极区域内。

33.步骤s300,执行退火工艺,以使所述p型掺杂层中的p型离子至少扩散至所述势垒

层中。

34.步骤s400,形成源电极、漏电极和栅电极,所述栅电极形成在所述p型掺杂层上,所述源电极和所述漏电极分别位于所述栅电极的两侧。

35.本实施例中,在栅电极和势垒层之间设置有p型掺杂层,以提高器件的阈值电压,形成增强型hemt器件。并且,还通过退火工艺使p型掺杂层中的p型离子在栅极区域向下扩散至势垒层中,有利于抬高势垒层的势垒,进一步提高器件的阈值电压。

36.下面结合图2-图5为对本实施例中在制备高电子迁移率晶体管的各个步骤进行详细说明。

37.在步骤s100中,具体参考图2所示,在一衬底100上依次形成沟道层200和势垒层300。

38.其中,所述衬底100可进一步为氮化镓(gan)衬底、硅(si)衬底、碳化硅(sic)衬底或者蓝宝石衬底等。

39.本实施例中,在制备所述沟道层200之前,还在所述衬底100上外延生长过渡层110,所述过渡层110例如为氮化镓(gan)过渡层或氮化铝(aln)过渡层等。通过设置所述过渡层110,一方面可减小所述衬底100与后续外延生长的外延层之间的晶格失配,提高外延层的晶体质量;另一方面,还可作为高阻层以减小器件漏电等。

40.接着,可利用外延工艺(例如,mocvd工艺)在所述过渡层110上依次形成沟道层200和势垒层300,其中,所述沟道层200和所述势垒层300可均包括iii-v族化合物层。例如,所述沟道层200包括氮化镓层(gan)。以及,所述势垒层300包括铝镓氮层(al

x

ga

1-x

n)。

41.需要说明的是,在后续工艺中将使p型掺杂层中的p型离子扩散至势垒层300中,有利于提高器件的阈值电压。此时,还可以在保持器件的阈值电压不变的情况下,增大势垒层300中的铝镓氮层(al

x

ga

1-x

n)内铝的组份,和/或,增大势垒层300的厚度。例如,所述势垒层300中,铝镓氮层(al

x

ga

1-x

n)中铝的组份x大于等于0.15,以提高器件的载流子浓度,并降低导通电阻;进一步的,还可使铝镓氮层(al

x

ga

1-x

n)中铝的组份x小于等于0.3,以避免因为铝的组份过大而导致后续镁的扩散难度较大。此外,还可设置所述势垒层300的厚度大于等于8nm,具体示例中所述势垒层300的厚度可以为8nm-25nm,以使器件具备更高的载流子浓度和更低的导通电阻。

42.在步骤s200中,继续参考图2所示,形成p型掺杂层400p,所述p型掺杂层400p形成在所述势垒层300上并位于栅极区域内。

43.具体示例中,所述p型掺杂层400p的制备方法可包括如下步骤。

44.步骤一,利用外延工艺在势垒层300上形成p型掺杂材料层,所述p型掺杂材料层具体可以为p型氮化镓层(p-gan)。本实施例中,该p型掺杂材料层内掺杂有镁(mg),并且可以在p型掺杂材料层中掺杂高剂量的镁(mg),以预留更多的镁(mg)在后续工艺中扩散至下方的势垒层300中,例如所述p型掺杂材料层中掺杂的镁(mg)的浓度为5e18cm-3-1e20cm-3

。

45.需要说明的是,在p型掺杂材料层中高浓度的镁(mg)受限于较低的激活率,镁(mg)的电离率较低,存在不完全电离的现象,因此可以认为,此时该p型掺杂材料层内的镁(mg)包括了未电离的镁和已电离而形成的镁离子。

46.步骤二,去除所述p型掺杂材料层位于非栅极区域的部分,而保留位于栅极区域内的部分,进而形成所述p型掺杂层400p。

47.本实施例中,具体参考图3所示,在执行退火工艺之前,还包括:形成钝化层600,所述钝化层600覆盖暴露出势垒层300和p型掺杂层400p。具体示例中,所述钝化层600的材料例如包括氧化铝、氧化硅或氮化硅等。

48.需要说明的是,所述钝化层600具体可用于对所述势垒层300进行钝化保护,有利于降低势垒层300的表面缺陷态、改善hemt器件的电流崩塌现象。此外,在所述钝化层600的覆盖下,还可避免p型掺杂层400p在后续的退火工艺中暴露出,有利于缓解后续的退火工艺对p型掺杂层400p造成的不利影响,例如可有效改善p型氮化镓层(p-gan)在退火工艺中发生分解的问题。

49.在步骤s300中,具体参考图4所示,执行退火工艺,以使所述p型掺杂层400p中的p型离子至少扩散至所述势垒层300中,进而可以在势垒层300中形成有p型离子扩散区700p。如此,即可抬高势垒层300的势垒,有利于耗尽导电沟道内的二维电子气。

50.其中,所采取的退火工艺包括在700℃-1000℃的退火温度下执行,以及该退火工艺的退火时间可以为10min-50min。本实施例中,利用较高的退火温度,可以有效促进p型掺杂层400p中的p型离子的扩散(例如,可使p型氮化镓层中镁的高效扩散),并且可执行较长时间的退火过程,确保p型掺杂层400p中的p型离子能够扩散至势垒层300中,甚至扩散至沟道层200中。

51.具体示例中,所述p型掺杂层400p中掺杂有高浓度的镁(mg),通过退火工艺即可使镁(mg)至少扩散至势垒层300中,在镁(mg)的扩散过程中可包括未电离的镁和/或已电离的镁离子。同时,由于镁(mg)发生扩散而形成p型离子扩散区700p,使得镁(mg)的整体平均浓度降低,有利于促使未电离的镁进一步发生电离,从而使得栅极区域内发生电离的镁离子的含量增加,进而使栅极区域内的二维电子气更容易被完全耗尽,实现器件的阈值电压升高。

52.还应当认识到,正因为p型掺杂层400p设置在栅极区域内,进而在进行p型离子扩散时可使p型离子主要扩散在栅极区域内的势垒层300中,而仅少量的p型离子会扩散出栅极区域,因此所形成的p型离子扩散区700p主要控制在p型掺杂层400p的正下方而位于栅极区域内,以精确控制栅极区域内的二维电子气的耗尽。

53.本实施例中,所述p型掺杂层400p中的p型离子向下扩散至所述势垒层300,并进一步扩散至沟道层200内,具体可扩散至沟道层200靠近势垒层的顶部区域内,从而可以更进一步的提高器件的阈值电压。

54.在步骤s400中,具体参考图5所示,形成源电极500s、漏电极500d和栅电极500g,所述栅电极500g形成在所述p型掺杂层400p上,所述源电极500s和所述漏电极500d分别设置在所述栅电极500g的两侧。

55.其中,所述栅电极500g可用于控制hemt器件内的二维电子气的电导变化,实现器件的导通或关断。以及,所述源电极500s和所述漏电极500d均电连接所述沟道层200,以使得沟道层200内的电子电流能够被有效收集。

56.一示例中,所述源电极500s、所述漏电极500d和所述栅电极500g的形成方法例如包括:首先,对钝化层600执行刻蚀工艺,以形成栅极沟槽、源极沟槽和漏极沟槽,所述栅极沟槽暴露出p型掺杂层400p,所述源极沟槽和漏极沟槽均贯穿钝化层600并抵达至势垒层300;接着,淀积金属材料,使金属材料分别形成在栅极沟槽、源极沟槽和漏极沟槽中;之后,

可执行低温退火(例如,退火温度为400℃-600℃)或者高温退火(例如,退火温度为700℃-900℃),以形成所述栅电极500g、所述源电极500s和所述漏电极500d,其中的退火时间可控制在2min以内。

57.本实施例中,所述源电极500s和所述漏电极500d均接触至势垒层300的表面,并可在势垒层300中形成离子掺杂区,以通过该离子掺杂区和沟道层200内的二维电子气连接。然而其他实施例中,还可使所形成的源极沟槽和漏极沟槽均由上至下贯穿钝化层600和势垒层300并抵达至沟道层200中,进而使所形成的源电极500s和漏电极500d直接和沟道层200内的二维电子气电连接。

58.基于如上所述的制备方法,下面对制备形成的高电子迁移率晶体管的结构进行说明。具体可参考图5所示,所述高电子迁移率晶体管包括:形成在衬底100上的沟道层200和势垒层300;以及,形成在势垒层300上的栅电极500g、源电极500s和漏电极500d。

59.其中,所述衬底100可进一步为氮化镓(gan)衬底、硅(si)衬底、碳化硅(sic)衬底或者蓝宝石衬底等。本实施例中,在所述衬底100上还外延生长有过渡层110,所述过渡层110例如为氮化镓(gan)过渡层或氮化铝(aln)过渡层等。通过设置所述过渡层110,一方面可减小所述衬底100与后续外延生长的外延层之间的晶格失配,提高外延层的晶体质量;另一方面,还可作为高阻层以减小器件漏电等。

60.继续参考图5所示,所述沟道层200和所述势垒层300依次形成在所述过渡层110上。其中,所述势垒层300的带隙宽度大于所述沟道层200的带隙宽度,从而使得宽带隙的势垒层300中的电子和势垒层表面的电子溢出,并移向所述沟道层200靠近所述势垒层300的界面处而被限制在界面处所形成的势阱中,进而形成二维电子气2deg(2-dimensional electron gas)。由于势阱中的这些电子与势垒层中的电离杂质空间分离,大大降低了库伦散射,从而显著提高了导电沟道中的电子迁移率。

61.进一步的,所述势垒层300和所述沟道层200均包括iii-v族化合物层,例如,所述沟道层200包括氮化镓层(gan),所述势垒层300包括铝镓氮层(al

x

ga

1-x

n)。其中,在所述势垒层300中,铝镓氮层(al

x

ga

1-x

n)中铝的组份x可大于等于0.15,以提高器件的载流子浓度,并降低导通电阻。此外,还可设置所述势垒层300的厚度大于等于8nm,以使器件具备更高的载流子浓度和更低的导通电阻。

62.本实施例中,所述势垒层300中还掺杂有p型离子,所述p型离子例如包括镁离子,此外在所述势垒层300中还可存在有未电离的镁。进一步的方案中,在所述沟道层200中也掺杂有p型离子,并且沟道层200内的p型离子和势垒层300中的p型离子相同,例如均包括镁离子,并且在沟道层200和势垒层300中还可同时存在有未电离的镁。

63.继续参考图5所示,在所述势垒层300上还形成有p型掺杂层400p,该p型掺杂层400p具体位于栅极区域内,并且所述p型掺杂层400p内的p型离子和所述势垒层300中的p型离子相同。例如,所述p型掺杂层400p内的p型离子和所述势垒层300中的p型离子均包括镁离子,以及在势垒层300和p型掺杂层400p内可同时存在有未电离的镁和已电离而形成的镁离子。

64.进一步的,在所述势垒层300上还覆盖有钝化层600,用于对所述势垒层300进行钝化保护,有利于降低势垒层300的表面缺陷态、改善hemt器件的电流崩塌现象。其中,所述钝化层600的材料例如包括氧化铝、氧化硅或氮化硅等。

65.继续参考图5所示,所述高电子迁移率晶体管还包括栅电极500g、源电极500s和漏电极500d,所述栅电极500g形成在所述p型掺杂层400p上,所述源电极500s和所述漏电极500d分别位于所述栅电极500s的两侧。本实施例中,所述源电极500s和所述漏电极500d均接触至势垒层300的表面,并可在势垒层300中形成离子掺杂区,以通过该离子掺杂区和沟道层200内的二维电子气连接。

66.综上所述,在栅电极500g和势垒层300之间设置有p型掺杂层400p,以提高器件的阈值电压,形成增强型hemt器件。在此基础上,还通过退火工艺使p型掺杂层400p中的p型离子在栅极区域向下扩散至势垒层300中,有利于抬高势垒层300的势垒,进一步提高器件的阈值电压。

67.进一步的,在维持器件的阈值电压的情况下,还有利于增大势垒层300中的铝镓氮层内铝的组份,还可进一步增大势垒层300的厚度,使器件的导通电阻降低,进而有效缓解了器件的阈值电压和导通电阻二者相互制约的问题。

68.此外,针对的掺杂镁的p型掺杂层400p而言,由于镁(mg)的扩散,使得镁(mg)的整体平均浓度降低,从而可促使未电离的镁进一步发生电离,使得栅极区域内发生电离的镁离子的含量增加,进而使栅极区域内的二维电子气更容易被完全耗尽,实现器件的阈值电压能够进一步升高。

69.需要说明的是,上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围。

70.还应当理解的是,除非特别说明或者指出,否则说明书中的术语“第一”、“第二”、“第三”等描述仅仅用于区分说明书中的各个组件、元素、步骤等,而不是用于表示各个组件、元素、步骤之间的逻辑关系或者顺序关系等。此外还应该认识到,此处的以及所附权利要求中使用的单数形式“一个”和“一种”包括复数基准,除非上下文明确表示相反意思。例如,对“一个步骤”或“一个装置”的引述意味着对一个或多个步骤或装置的引述,并且可能包括次级步骤以及次级装置。应该以最广义的含义来理解使用的所有连词。以及,词语“或”应该被理解为具有逻辑“或”的定义,而不是逻辑“异或”的定义,除非上下文明确表示相反意思。此外,本发明实施例中的方法和/或设备的实现可包括手动、自动或组合地执行所选任务。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1