横向功率半导体器件的制作方法

背景技术:

1、0横向功率半导体器件通常用作电子控制的功率开关。在封装中,

2、半导体的栅极、源极和漏极通常通过使用引线接合(wire-bonding)

3、或夹片接合(clip-bonding)来连接。特别是对于高功率半导体,如高电子迁移率晶体管、hemt器件,夹片接合比引线接合具有优势。

4、高开关速度和高功率的结合要求触点具有低电阻和电感,以优化电气5性能。夹片接合可以满足这些要求,因为电路的开关损耗和电感会降低。

5、由于高铅焊料具有高导热率、良好的可靠性和高接合强度,因此夹片结合的封装通常可以包括高铅焊料,以将夹片连接到焊盘。出于环境原因,无铅接合是一种合适的替代方法,并且可以包括高导热粘0合剂。接合夹片可以由铜构成,在单个操作中将铜焊接到栅极和源极;

6、这种铜夹片具有改善的电和热特性以及增加的可靠性。

7、相比于引线接合,尽管横向功率半导体器件的夹片接合可能具有几个优点,但也具有一些缺点。已经发现,在组装过程中,诸如hemt器件等功率半导体器件的夹片接合封装可能表现出热机械应力。这可5能会导致隔离金属层的绝缘体层出现裂缝。当绝缘体中出现这种裂缝时,这可能导致半导体器件失效,尤其是在高电应力区域。

8、因此,需要提高这种横向功率半导体器件的可靠性,更具体地说,需要降低横向功率半导体器件的绝缘体层中出现裂缝的风险,尤其是在高电应力区域中。

技术实现思路

1、根据本公开的第一方面,一种横向功率半导体器件,包括:

2、-源极焊盘区域,其形成在所述器件的金属层中;

3、-漏极焊盘区域,其与所述源极焊盘间隔开并形成在所述器件的所述金属层中;

4、-多个导电指状物,其形成在器件的另一金属层中,并且包括:

5、-多个平行的源极指状物,其联接到所述源极焊盘区域并从所述源极焊盘区域朝向所述漏极焊盘区域延伸且延伸到所述漏极焊盘区域下方,以及

6、-多个平行的漏极指状物,其与所述多个源极指状物隔离,并且联接到所述漏极焊盘区域并从所述漏极焊盘区域朝向所述源极焊盘区域延伸且延伸到所述源极焊盘区域下方,其中所述漏极指状物叉指式布置(interdigitated)在所述源极指状物之间;并且其中所述漏极焊盘区域包括多个漏极焊盘,所述多个漏极指状物中的每一个对应一个漏极焊盘,其中所述多个漏极焊盘通过间隔而彼此隔离,所述间隔与延伸到所述漏极焊盘区域下方的所述源极指状物的位置相对应。

7、发明人发现,某些横向功率半导体器件显示出由金属层之间的短路引起的故障迹象。对故障器件的调查显示,两个金属层之间的绝缘体层出现裂缝,导致短路。进一步的研究表明,这些裂缝可集中在一个金属层的边界与另一金属层的边界交叉的这一特定区域。在这两个金属层之间的顶部绝缘体中发现了这些裂缝的证据,这被认为是该器件故障的可能原因,或者至少表明该结构中的高机械应力会降低器件的可靠性。

8、这个问题主要发生在具有夹片接合管芯的横向半导体器件中。在高温、高电压下,由组装过程或封装本身引起的热机械应力会在两个金属层之间的绝缘体层中产生电应力。

9、发明人已经认识到,去除第二金属层和第三金属层的边界之间的重叠(superimposition)降低了绝缘体层中出现裂缝的风险,从而增加了器件的可靠性。

10、因此,本公开的横向功率半导体器件中这些金属层中的一个以这样的方式配置:该(第二)金属层在它与另一(第三)金属层的区域重叠的区域处被去除,使得这两个金属层不仅通过这些金属层之间的绝缘体层而彼此隔离,而且通过横向的间隔而彼此隔离,使得这两个金属层不位于彼此之上。由于这种设计,降低了该区域出现裂缝的风险。

11、根据本公开,横向功率半导体器件至少具有源极焊盘区域、漏极焊盘区域和多个导电指状物。这些平行的指状物包括联接到源极焊盘并从源极焊盘延伸的一组平行的源极指状物或通道,以及联接到漏极焊盘并从漏极焊盘延伸的一组平行的漏极指状物或通道。这些源极指状物和漏极指状物叉指式交叉。源极焊盘区域和漏极焊盘区域形成在第三金属层中,而平行的指状物形成在器件的第二金属层中。这些平行的指状物中的一些,尤其是平行的源极指状物,延伸到漏极焊盘区域下方。常规设计具有形成在漏极焊盘区域中的单个漏极焊盘,这因此使得源极指状物的可能出现裂缝的一部分重叠。本公开的设计将其漏极焊盘区域分割成多个漏极焊盘,每个漏极焊盘用于一个对应的漏极指状物。这样,漏极焊盘区域(即第三金属层)的金属在下面的金属层(即第二金属层)的源极指状物的位置处被去除。因此,形成在第三金属层中的这些漏极焊盘中的每一个通过这样的间隔而彼此隔离:该间隔与延伸到漏极焊盘区域下方的源极指状物的位置相对应。

12、在一个示例中,半导体器件还包括覆盖每个所述漏极焊盘的周缘的绝缘体层。

13、在一个示例中,半导体器件还包括尺寸与所述漏极焊盘相对应的接触焊盘,并且其中每个所述接触焊盘尤其覆盖所述漏极焊盘的被所述漏极焊盘的周缘上的绝缘体层所包围的区域。

14、在一个示例中,横向功率半导体器件是高电子迁移率晶体管hemt器件。

15、在一个示例中,横向功率半导体器件还包括:

16、-iii-v族层,所述iii-v族层包括半导体电路,所述iii-v族层尤其是gan层。

17、本公开的优选实施例之一是高功率半导体器件,其包括具有高电子迁移率晶体管hemt或场效应晶体管fet的半导体封装。fet或hemt优选为iii-v族半导体,更优选为gan型fet或hemt半导体。

18、在一个示例中,所述多个导电指状物由第二导电层形成,所述另一导电层布置在所述iii-v族层的顶部,并且被所述第二导电层和所述iii-v族层之间的绝缘体层隔离。

19、在一个示例中,所述源极焊盘区域和所述漏极焊盘区域由第三导电层形成,所述第三导电层布置在所述第二导电层的顶部,并且被所述第三导电层和所述第二导电层之间的绝缘体层隔离。

20、在一个示例中,每个漏极焊盘还包括布置在该漏极焊盘的顶部的漏极接触焊盘,并且其中所述漏极焊盘和所述漏极接触焊盘通过所述漏极焊盘和所述漏极接触焊盘之间的绝缘体层而隔离,其中所述漏极接触焊盘优选地由钯覆盖的金属层构成。

21、在一个示例中,源极焊盘区域和所述漏极焊盘通过多个对应的通孔联接到所述多个导电指状物。

22、在一个实例中,所述多个平行的漏极指状物中的每一个通过公共漏极汇流条互连,其中所述公共漏极汇流条优选地形成在所述金属层中。

23、根据本公开的第一方面的设计展现了增加的可靠性和性能。汇流条提高了在片测试(on-wafer test)期间测量ron的精度,该公共漏极汇流条形成在多个指状物的金属层中。由于漏极焊盘彼此隔离,所以与单个漏极焊盘覆盖整个漏极焊盘区域的常规设计相比,每个单独的漏极焊盘将具有更高的ron。通过将每个漏极指状物与公共漏极汇流条互连,该公共漏极汇流条优选地形成在指状物的同一金属层中,由此提高了测量ron的精度。

24、在一个示例中,所述源极焊盘区域和所述漏极焊盘区域中的一个或多个被布置为用于所述半导体器件的夹片接合封装。

25、在第二方面,提供了一种共源共栅的(cascoded)半导体封装,该共源共栅的半导体封装包括布置在根据第一方面或根据其任何示例的gan hemt顶部的硅mosfet。

26、对于其中si mosfet与gan hemt一起工作的共源共栅器件,优选将mosfet放置在hemt的顶部。这样,中间节点的寄生电感最小,并且在开关操作期间共源共栅的性能被优化。

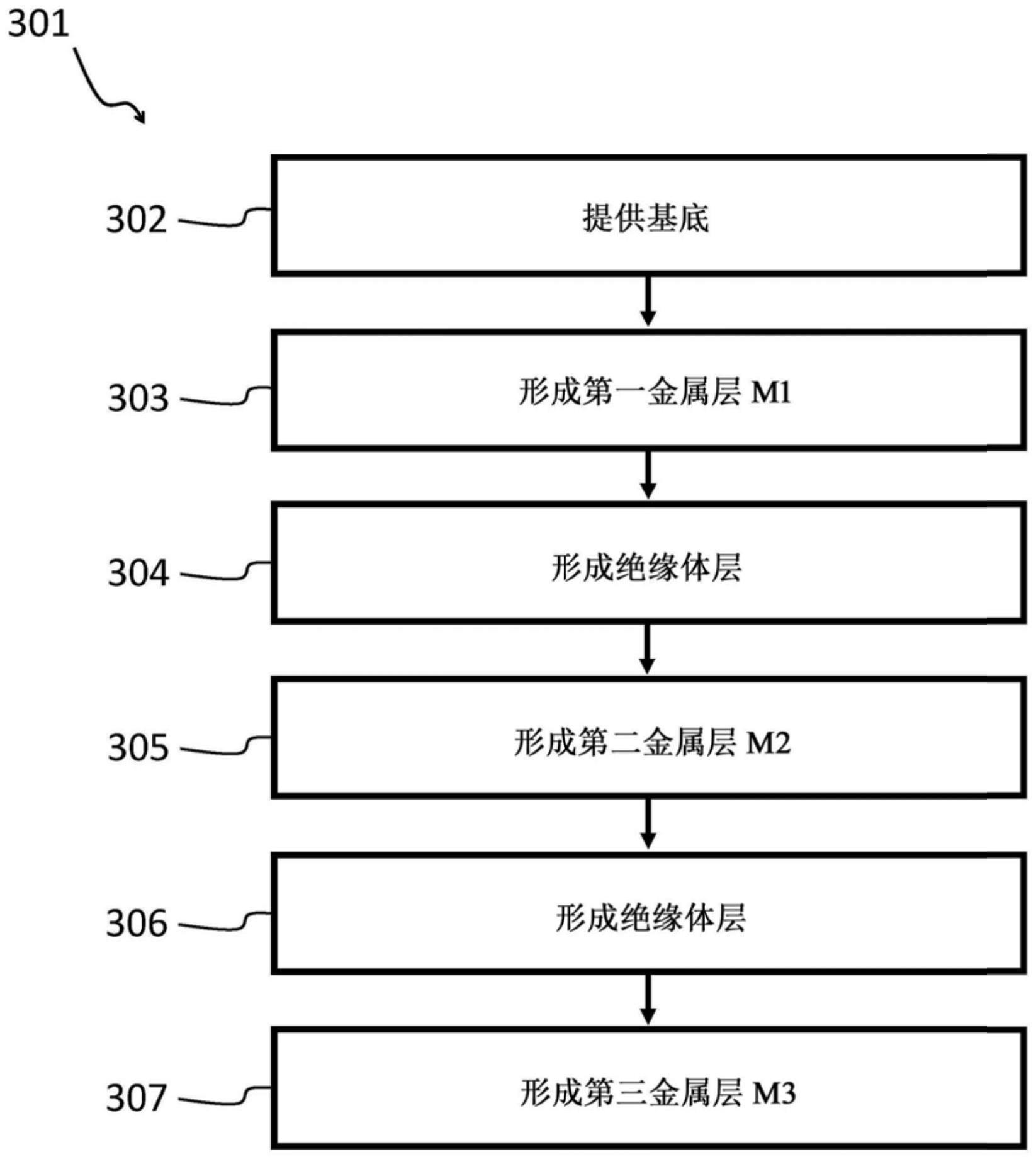

27、在第三方面,提供了一种制造横向功率半导体器件的方法,所述方法包括以下步骤:

28、-提供半导体基底,并在半导体基底上形成半导体器件;

29、-形成第一金属层(m1);

30、-在所述第一金属层上形成绝缘体层;

31、-在所述绝缘体层上形成第二金属层(m2),所述第二金属层包括多个导电指状物,所述导电指状物包括多个平行的源极指状物和与所述源极指状物隔离的平行的漏极指状物,其中所述漏极指状物叉指式布置在所述源极指状物之间;

32、-在所述第二金属层上形成绝缘体层;

33、-穿过所述绝缘体层,在所述第二金属层(m2)和第三金属层(m3)

34、之间形成多个通孔;

35、-在所述绝缘体层上形成所述第三金属层(m3),所述第三金属层包括源极焊盘区域和漏极焊盘区域;

36、-并且其中所述漏极焊盘区域包括多个漏极焊盘,所述多个漏极指状物中的每一个对应一个漏极焊盘,其中所述多个漏极焊盘通过与延伸到所述漏极焊盘区域下方的所述源极指状物的位置相对应的间隔而彼此隔离。

- 还没有人留言评论。精彩留言会获得点赞!