半导体器件和双向ESD保护器件的制作方法

本公开的各方面涉及一种半导体器件。更具体而言,本公开涉及一种特别用于esd保护目的半导体器件。

背景技术:

1、例如由于电子器件(或电路)与不同带电物体之间的紧密接触,或者由于所述器件(或电路)与所述物体之间的电介质的击穿,导致突然的电流,使得所述器件和电路可能遭受静电放电(esd)事件。由于esd事件的突然放电而引起的过电流能够对灵敏的电子器件造成显著和/或永久的损坏。

2、esd保护器件可用于防止对电子器件或电路的这种损坏。例如,专用esd保护器件可以并联地电连接到电子器件,以使esd电流分流。图1中示出了示例性配置,其中esd保护器件20连接在例如电子电路30(诸如集成电路(ic))的信号线31(例如数据线)和轨线(railline)32(或另一信号线)之间。替代地,esd保护器件20可以与电子电路30集成到单个ic中。在此,应注意的是,esd保护器件20可连接在电子电路20的任意两个端子之间。

3、通常,esd保护器件具有相对高的电流处理能力,并且通过允许esd事件引起的esd电流的相当大的一部分流过esd保护器件来阻止或限制所述电流流过灵敏的电子器件。同时,esd保护器件应当将灵敏的电子器件或电路内的电压限制到足够低的电平,以防止损坏要保护的所连接的电子器件或电路。

4、对于许多应用,诸如高数据速率通信,esd保护器件优选地是双向的,并且在要保护的电路上具有低电容负载、高稳健性以及相对低的触发和保持电压。反并联二极管或反并联二极管堆叠件是根据这些参数实现高性能的适当选择。

5、通常,需要相对大的二极管宽度,以在esd事件期间容纳esd电流。这通常通过并联布置多个二极管单元(unit cell)来实现。多个单元例如集成在同一半导体管芯上,并且经由半导体管芯的金属层或金属层堆叠件并联连接。通常通过提供如上所述的第一多个单元和第二多个单元来将已知的esd保护器件制成双向的,第一多个单元和第二多个单元被分开布置在同一半导体管芯上或被分开布置在不同的半导体管芯上,并且以反并联配置连接第一多个单元和第二多个单元。

6、实现如上所述的esd保护器件的主要挑战涉及最小化由所述esd保护器件在要保护的电路上的电容性负载。特别是,在正常操作期间(即,没有esd事件的情况下),esd保护器件应尽可能少地加载待保护的电路,以免电路性能降级。例如,在高速通信应用中,由于esd保护器件的存在而引起的电容性负载对于要保护的电路的最大通信速度是有害的。

技术实现思路

1、下面阐述了本文公开的某些实施例的方面的概述。应当理解,这些方面仅被呈现以向读者提供这些特定实施例的简要概述,并且这些方面不旨在限制本公开的范围。实际上,本公开可以涵盖可能未阐述的各种方面和/或方面的组合。

2、根据本公开的一方面,提供了一种半导体器件。该半导体器件具有第一端子和第二端子,并且包括半导体管芯;集成在半导体管芯上并且电连接在第一端子和第二端子之间的多个二极管单元,每个单元包括在半导体管芯中的具有第一电荷类型的第一区域和在半导体管芯中的具有第二电荷类型的第二区域。半导体器件还包括隔离结构,其布置在半导体管芯中,隔离结构被配置为将半导体管芯中的多个单元彼此电隔离;以及多个接触件,多个接触件包括电连接至第一端子的第一接触件和电连接至第二端子的第二接触件。第一接触件和第二接触件中的每个接触件电连接到多个单元中的相应单元的第一区域和多个单元中的另一单元的第二区域。

3、在根据本公开的半导体器件中,第一接触件和第二接触件由于连接到第一区域和第二区域两者而可以在两个方向上承载电流,电流的方向取决于第一端子和第二端子两端的电压的极性以及第一区域和第二区域的所选电荷类型。这样,当半导体器件与要保护的电路电连接时,可以显著减少用于接触件的互连材料(例如金属化)的总量,导致在要保护的电路上较低的电容负载。

4、多个单元可以布置在多个组中,每个组具有经由一个或多个中间接触件串联连接的两个或更多个单元。每个中间接触件可以电连接到所述组中的多个单元中的相应单元的第一区域并且电连接到所述组中的多个单元中的另一单元的第二区域。通过串联连接多个单元中的多组单元,可以实现堆叠二极管配置,同时仍使第一接触件和第二接触件能够承载在第一端子和第二端子之间在两个方向上的电流。

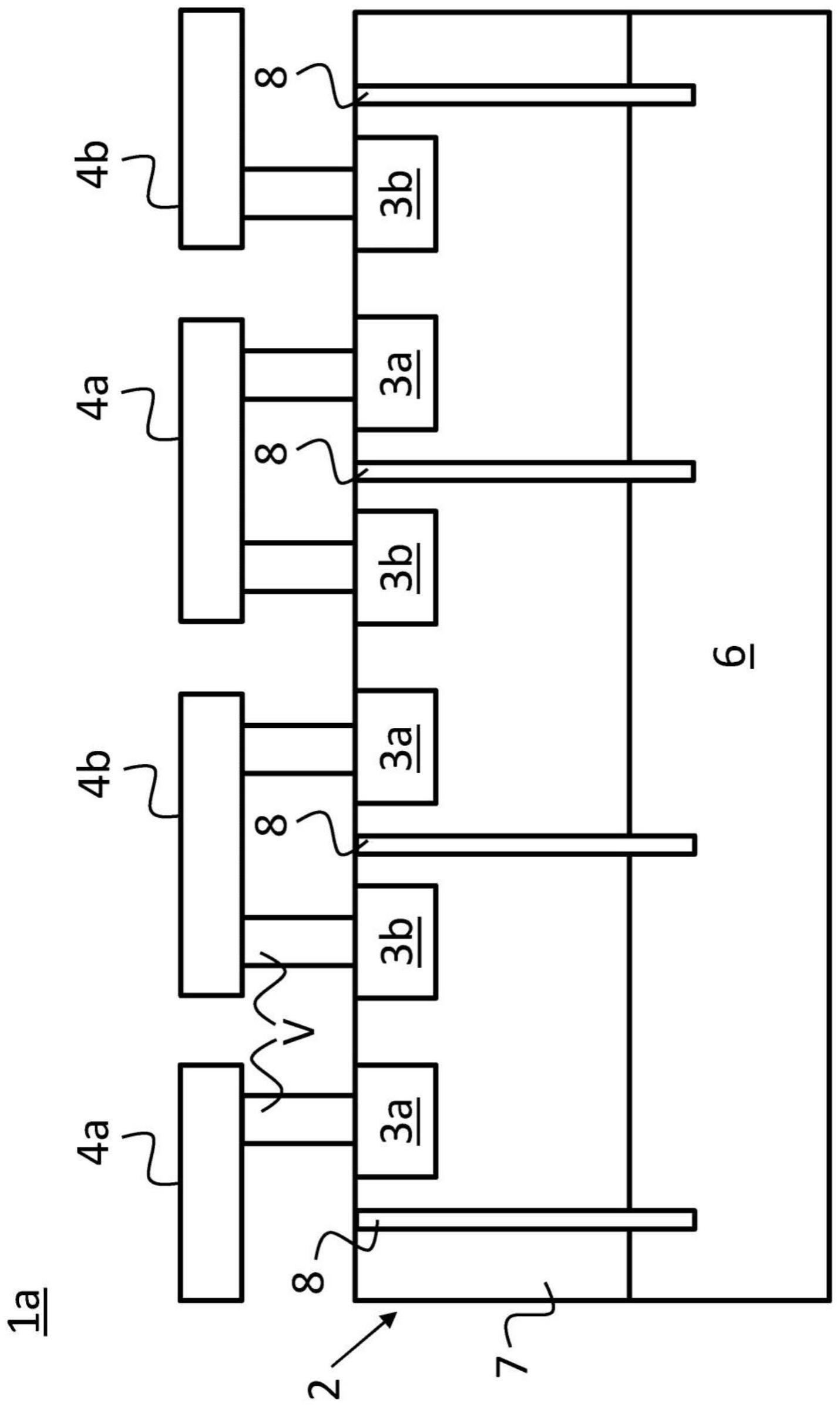

5、中间接触件的第一部分可以以与第一接触件交错的方式布置,并且中间接触件的第二部分可以以与第二接触件交错的方式布置。此外,中间接触件的第一部分中的中间接触件可以均电连接到中间接触件的第二部分中的至少一个中间接触件。替代地,第一接触件和第二接触件可以交替地布置,其中,中间接触件可以布置在所述第一接触件和所述第二接触件之间。以此方式,可以实现面积有效且电容低的堆叠二极管配置。

6、电连接到同一第一接触件、同一第二接触件和/或(如果适用的话)同一中间接触件的单元可以被相邻地布置,在这种情况下,可以最小化用于接触件的互连材料的总量。

7、多个单元的第一部分可以在第一端子和第二端子之间彼此平行地布置,或者如果适用的话,多个组可以在第一端子和第二端子之间彼此平行地布置,并且多个单元的第二部分可以在第一端子和第二端子之间与第一部分反平行地布置,或者如果适用的话,多个组可以在第一端子和第二端子之间与第一部分反平行地布置。

8、第一接触件可以经由第一互连部分彼此电连接。第一互连部分可以构成或可以电连接到第一端子。此外或替代地,第二接触件可以经由第二互连部分彼此电连接。第二互连部分可以构成或可以电连接到第二端子。

9、第一接触件、第二接触件和/或(如果适用的话)中间接触件可以具有指状物形状。例如,单元可以以多指结构布置。

10、半导体管芯可以包括半导体衬底和外延层,其中多个单元形成在外延层中。

11、隔离结构可以包括多个纵向隔离结构和多个横向隔离结构。纵向隔离结构可以均被布置在多个单元中的相邻单元之间,并且多个横向隔离结构可以均相对于半导体管芯的顶表面被布置在多个单元中的相应单元下方。纵向隔离结构可以从所述顶表面至少延伸到横向隔离结构。

12、纵向隔离结构可以均在实质上垂直于所述顶表面的第一方向上从顶表面延伸,并且横向隔离结构可以均在实质上平行于所述顶表面的第二方向上延伸。

13、横向隔离结构可以由相应埋置绝缘层(诸如埋置氧化物层)形成。在一些实施例中,埋置绝缘层可以一起形成连续埋置绝缘层的相应部分。

14、多个横向隔离结构可以由在与对应的单元相邻布置的纵向隔离结构之间延伸的相应pn结形成。

15、在一些实施例中,外延层可以具有与半导体衬底不同的电荷类型,并且pn结可以由在外延层和半导体衬底之间的结形成。在替代实施例中,外延层中的可以布置有多个单元的阱区可以具有与外延层的其余部分和/或半导体衬底不同的电荷类型,并且pn结可以由在外延层与半导体衬底之间的相应结形成和/或由在阱区与外延层之间的相应结形成。

16、pn结可以分别由在半导体管芯中的具有第一电荷类型或第二电荷类型的相应第一埋置区域和在半导体管芯中的具有第二电荷类型或第一电荷类型的相应第二埋置区域形成。第二埋置区域中的每个可以通过对应的第一埋置区域与外延层间隔开。

17、纵向隔离结构可以均包括沟槽。沟槽可以具有布置在其中的绝缘材料,诸如氧化物材料。

18、多个单元中的每个单元的第一区域和第二区域中的一个可以从半导体管芯的顶表面延伸到埋置绝缘层。外延层或外延层中的可以布置有多个单元的阱区可以具有第二电荷类型。在这种情况下,纵向隔离结构可以均由在相应单元的第一区域和第二区域中的所述一个与外延层或阱区之间的相应pn结形成。

19、替代地,多个单元中的每个单元的第一区域和第二区域二者从半导体管芯的顶表面延伸到埋置绝缘层。纵向隔离结构然后可以由相应单元的第一区域或第二区域中的一个与外延层或(如果适用的话)外延层中的布置有多个单元的阱区之间的相应pn结形成,或者由在相应单元的第一区域与直接与所述第一区域相邻布置的单元的第二区域之间的相应pn结形成。

20、多个接触件以及(如果适用的话)第一互连部分和第二互连部分可以布置在金属层中,或者布置在金属层堆叠件的一个或多个金属层中,金属层或金属层堆叠件的一个或多个金属层布置在半导体管芯的顶部上。

21、第一电荷类型可以对应于p型掺杂,并且第二电荷类型可以对应于n型掺杂,或者反之亦然。

22、根据本公开的另一方面,提供一种esd保护器件,其被配置为电连接至电子电路,并保护该电子电路免于esd事件。esd保护器件包括一个或多个上述半导体器件。esd保护器件可以是封装器件。

23、根据本公开的又一方面,提供一种器件,其包括集成在半导体管芯上的电子电路和一个或多个上述半导体器件。一个或多个半导体器件集成在半导体管芯上,并且电连接到电子电路以保护电子电路免受esd事件。该器件可以是封装器件。

- 还没有人留言评论。精彩留言会获得点赞!