一种晶圆表面具有再钝化层的凸块高度测量方法与流程

1.本发明涉及半导体封装技术领域,更具体涉及一种晶圆表面具有再钝化层的凸块高度测量方法。

背景技术:

2.晶圆(wafer)是一个圆形硅片,其上建立了许多独立的电路,单个独立电路被称为芯片(die),芯片上电镀的凸块称为bump。在晶圆完成凸块工艺后,使用3d测量设备对晶圆上所有的凸块进行测量。

3.利用3d测量设备进行测量时,3d测量设备的光源会穿透芯片表面的re-passivation(再钝化层),导致测量不准确,如图1所示,3d测量设备测得凸块上最高点位置得到最高信号高度a,穿透芯片表面的re-passivation测得底部信号高度b,只能得到底部信号高度b与最高信号高度a之差,由于该底部信号位置b低于re-passivation表面,最终导致凸块高度就偏高,这样,无法准确测量凸块高度,就无法评估工艺能力以及判断产品质量。因此,能准确测量凸块高度变得十分重要。

4.现有的测量方法是,通过上述方式测量数据后,统一减去一个固定值,使其接近真实值,此方法默认re-passivation的厚度一样为该固定值,但实际re-passivation的厚度在晶圆内分布会有差异,所以此方法存在局限性。

技术实现要素:

5.为了解决上述问题,本发明提供了一种晶圆表面具有再钝化层的凸块高度测量方法,3d测量设备的光源无法穿透再钝化层,能够准确抓取被测基准面,得到准确的凸块高度值,为后续工艺提供真实的数据。

6.根据本发明的一个方面,提供了一种晶圆表面具有再钝化层的凸块高度测量方法,其包括:

7.s1:完成凸块制造:

8.s1a、在来料晶圆表面涂布光刻胶作为再钝化层,经过曝光、显影在焊盘上方留出开口;

9.s1b、在再钝化层的开口内进行溅射工艺,形成溅射层;

10.s1c、在再钝化层上方涂布光刻胶,经过曝光、显影将再钝化层开口处露出溅射层;

11.s1d、通过电镀、去光刻胶、腐蚀、回流工艺,制作出凸块;

12.s2:溅射金属钛屏蔽层:

13.将s1制得的晶圆进行溅射一层钛,形成钛屏蔽层,钛屏蔽层形成于凸块和再钝化层的表面;

14.s3:使用3d测量设备自动测量晶圆上所有凸块的高度:

15.测量凸块上钛屏蔽层的顶部最高信号得到顶部信号高度,测量对应该凸块旁再钝化层上钛屏蔽层的信号高度得到底部信号高度,底部信号高度减去顶部信号高度直接得到

该凸点高度;

16.s4:剥离溅射的钛屏蔽层:

17.使用钛腐蚀液采用化学腐蚀的方法将钛屏蔽层去除。

18.在一些实施方式中,所述s2中的溅射的钛屏蔽层的均匀度为

19.在一些实施方式中,所述s2中的溅射的钛屏蔽层的厚度为0.05μm。

20.在一些实施方式中,所述s2中凸块的顶面形成有钛屏蔽层,凸块的侧面无钛屏蔽层。

21.在一些实施方式中,所述s4中进行化学腐蚀的温度为35

±

2℃,化学腐蚀的时间为100

±

20s。

22.在一些实施方式中,所述s4中进行化学腐蚀时,通过漏电流测试、以确认凸块与再钝化层是否存在漏电流,若漏电流≤2na即为完成化学腐蚀,若漏电流测试结果没有达到≤2na、则再进行化学腐蚀直至达标。

23.在一些实施方式中,所述s3中被测再钝化层上钛屏蔽层的位置范围为对应凸块直径尺寸的120%内。

24.与现有技术相比,本发明的有益效果是:本发明提供了一种晶圆表面具有再钝化层的凸块高度测量方法,工艺难度不高、易操作,通过在完成凸块制造的晶圆上,溅射一层0.05μm的材质为高纯度钛的钛屏蔽层,钛屏蔽层覆盖在再钝化层表面、以及凸块的顶部,在测量时,3d测量设备的光源无法穿透钛屏蔽层,也就不会把再钝化层的底面作为底部信号的基准面,3d测量设备能够准确抓取钛屏蔽层作为基准面,测量出最高信号高度和底部信号高度,两者之差即可准确得到凸块的高度值,通过该方法得到的高度为凸块真实的高度,以便正确评估工艺能力以及判断产品质量,该凸块高度测量方法适用于pi+pillar/solder,(pi+)rdl+pi+pillar/solder,pi+ubm+solder ball,(pi+)rdl+pi+ubm+solder ball等多种结构产品。

附图说明

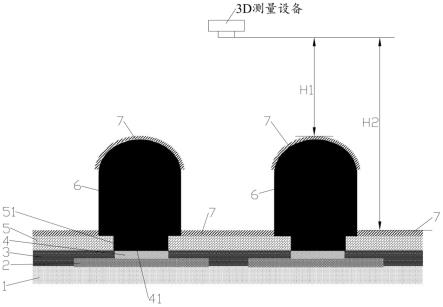

25.图1是现有技术测量凸块高度的方式示意图;

26.图2是本发明提供的凸块高度测量方法的测量示意图;

27.图3是钛屏蔽层上底部信号高度的测量范围示意图。

具体实施方式

28.下面结合具体实施方式对本发明作进一步的说明。

29.如图2所示,本发明所述一实施方式的一种晶圆表面具有再钝化层的凸块高度测量方法,凸块高度是指凸块相对于再钝化层的上表面向外凸出的实际高度,该凸块高度测量方法包括如下步骤:

30.第一步:完成凸块6制造,具体包括如下步骤:

31.a、来料晶圆(wafer)包括硅片层1、贴装的芯片2、表面的钝化层3、芯片上的焊盘4。在来料晶圆表面涂布光刻胶作为再钝化层5(re-passivation),经过曝光、显影的工艺,在焊盘上方留出开口51。

32.b、在再钝化层5的开口51内进行溅射工艺,形成溅射层41,该溅射层41主要是用于

提高凸块6与焊盘4之间的结合力。

33.c、在再钝化层5上方涂布光刻胶(图未示出),经过曝光、显影将再钝化层5开口处露出溅射层41。

34.d、通过电镀、去光刻胶、腐蚀、回流工艺,制作出凸块6。凸块6一般为cu+sn或cu+snag或cu+ni+snag这三种材质。

35.第二步:溅射金属钛屏蔽层7,具体操作包括:

36.将第一步制得的具有凸块6的晶圆进行溅射一层钛,形成钛屏蔽层7,溅射的钛屏蔽层7的厚度为0.05μm,溅射的钛屏蔽层7的均匀度为钛屏蔽层7覆盖凸块6和再钝化层5的表面。钛屏蔽层7的材质为高纯度的钛。

37.需要注意的是,在进行溅射形成钛屏蔽层7前,不需要进行常规工艺的rf(等离子)刻蚀,常规工艺的rf刻蚀的作用是去除焊盘表面的氧化层,而此处不进行rf刻蚀的目的是避免对已经完成的凸块6产生影响,防止损伤凸块6。

38.在进行本步骤操作时,钛屏蔽层7仅需要覆盖于凸块6的顶面,凸块6的侧面不需要覆盖钛屏蔽层7,因为测量的时候,不会取凸块6的侧面作为基准面。这样,可避免溅射钛屏蔽层7时工艺的浪费,也为后续剥离钛屏蔽层7节约时间和成本。

39.第三步:使用3d测量设备自动测量晶圆上所有凸块6的高度,具体操作方式为:

40.3d测量设备置于被测物的正上方,测量凸块6上钛屏蔽层7的顶部最高信号得到顶部信号高度h1,测量对应该凸块6旁再钝化层5上钛屏蔽层7的信号高度得到底部信号高度h2,将底部信号高度h2减去顶部信号高度h1直接得到该凸点高度。选取底部信号高度h2的基准点时,以对应的凸块6为中心、并以该凸块直径尺寸的120%向外扩(图3所示),检测该范围以内的再钝化层5上钛屏蔽层7的位置。

41.第四步:剥离溅射的钛屏蔽层7,具体操作如下:

42.使用钛腐蚀液,采用化学腐蚀的方法,将钛屏蔽层7去除。具体的,钛腐蚀液的组分为浓度为10~40%的双氧水、浓度为10~40%的氢氧化钾、其余为添加剂,,双氧水与氢氧化钾的比例为2:1,、添加剂的成分包括al保护剂,cu保护剂,snag保护剂,ni保护剂。进行化学腐蚀的温度为35

±

2℃,化学腐蚀的时间为100

±

20s。在进行化学腐蚀时,通过漏电流测试来确认凸块与再钝化层是否存在漏电流,若漏电流≤2na即为完成化学腐蚀;若漏电流测试结果没有达到≤2na,则再进行化学腐蚀直至测试达标。

43.本发明提供的晶圆表面具有再钝化层的凸块高度测量方法,工艺难度不高、易操作,在现有技术的基础上能够实现。通过在完成凸块6制造的晶圆上,溅射一层0.05μm的钛屏蔽层7,钛屏蔽层7覆盖在再钝化层5表面、以及凸块6的顶部,在测量时,3d测量设备的光源无法穿透钛屏蔽层7,也就不会把再钝化层5的底面作为底部信号的基准面,3d测量设备能够准确抓取钛屏蔽层7作为基准面,测量出顶部信号高度h1和底部信号高度h2,两者之差即可准确得到凸块6的高度值。通过该方法得到的高度为凸块6真实的高度,以便正确评估工艺能力以及判断产品质量。该凸块高度测量方法适用于pi+pillar/solder,(pi+)rdl+pi+pillar/solder,pi+ubm+solder ball,(pi+)rdl+pi+ubm+solder ball等多种结构产品,适用范围广。

44.以上所述的仅是本发明的一些实施方式,应当指出,对于本领域的普通技术人员来说,在不脱离本发明的创造构思的前提下,还可以做出其它变形和改进,这些都属于本发

明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1