像素单元、光探测器及其形成方法与流程

本发明涉及光探测器领域,特别涉及一种像素单元、光探测器及其形成方法。

背景技术:

1、车用三维距离成像系统由于其应用场景的特点,在性能上的核心需求为探测距离长,环境背景亮度高,行驶速度快;因此相比移动终端用直接飞行时间(direct time offly,dtof)光学传感器通常有高增益,高敏感度,高时间分辨率的性能指标需求。

2、三维距离成像系统的光探测器一种常见的表现形式为硅光电倍增管(sipm)。硅光电倍增管多个单光子雪崩二极管(spad)并联组成。通常每个spad单元独立串联一个淬灭电阻,多个串联有猝灭电阻的spad单元的阴极和阳极分别并联形成阵列作为一个像素以输出信号,多个阵列即可实现三维成像。

3、三维距离成像系统的光探测器的高时间分辨率需求,要求整个光探测器和读出电路所构成的系统具有较低的寄生电阻和寄生电容,以尽可能缩短spad的恢复时间(recovery time)。

4、三维距离成像系统的高增益需求,常常要求spad的过电压较高,以获得更高的光子探测效率,因此spad的工作电压较高。这对器件的电学隔离和直流电阻(direct currentresistance,dcr)降低等性能提出了更高的挑战。

5、但是现有方法所形成的sipm,往往存在光敏区面积受限、工艺成本高等问题。

技术实现思路

1、本发明解决的问题在保证高过电压、短恢复时间的同时,如何扩大光敏区面积。

2、为解决上述问题,本发明提供一种像素单元,包括:

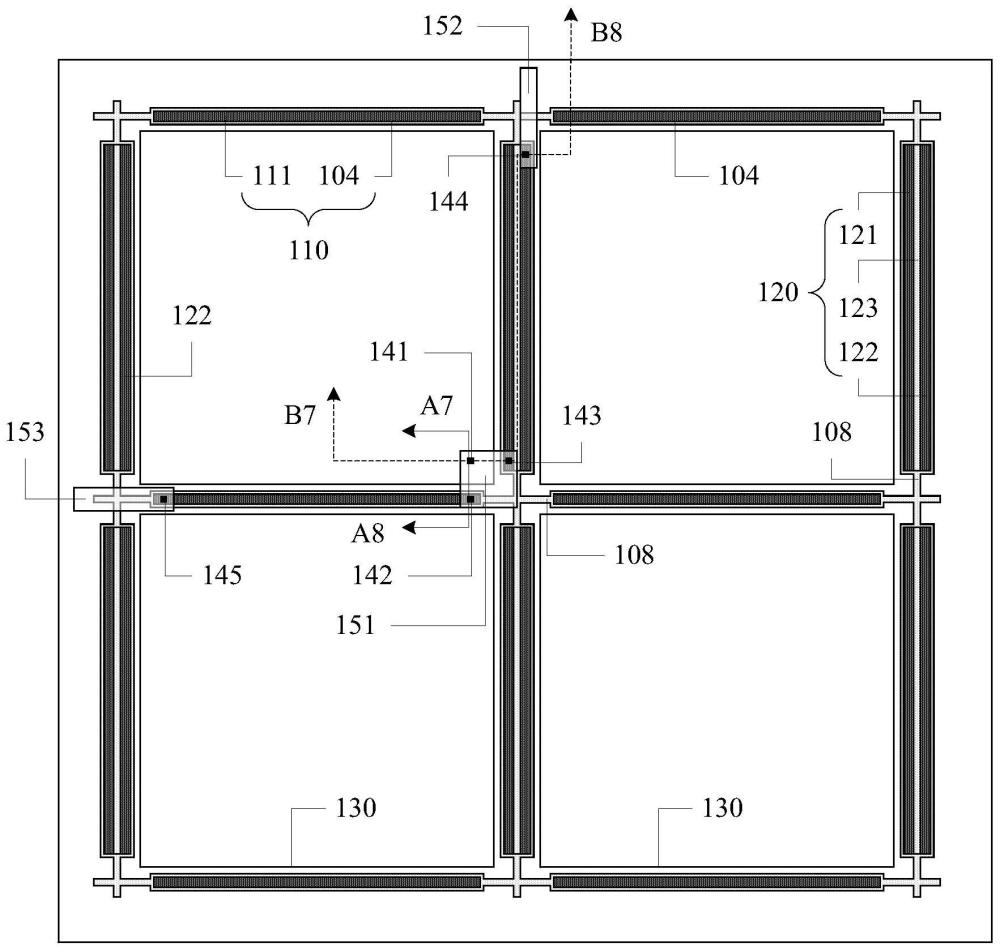

3、基底;第一深沟槽隔离结构,所述第一深沟槽隔离结构位于所述基底内,所述第一深沟槽隔离结构沿第一方向延伸;第二深沟槽隔离结构,所述第二深沟槽隔离结构位于所述基底内,所述第二深沟槽隔离结构与所述第一深沟槽隔离结构电绝缘,所述第二深沟槽隔离结构沿第二方向延伸,所述第一方向与所述第二方向相交;所述第二深沟槽隔离结构包括:第一导电层和第二导电层以及位于所述第一导电层和第二导电层之间的介质层,所述第一导电层、所述介质层和所述第二导电层的堆叠方向平行所述基底的表面且垂直所述第二方向;感光元件,所述感光元件位于所述第一深沟槽隔离结构和所述第二深沟槽隔离结构包围的基底内,所述感光元件与所述第一深沟槽隔离结构串联。

4、可选的,还包括:绝缘件,所述绝缘件位于所述第一深沟槽隔离结构和第二深沟槽隔离结构相交位置的基底内。

5、可选的,沿平行所述基底的表面且垂直所述第一方向上,所述绝缘件的尺寸小于所述第一深沟槽隔离结构的尺寸;沿平行所述基底的表面且垂直所述第二方向上,所述绝缘件的尺寸小于所述第二深沟槽隔离结构的尺寸。

6、可选的,所述第一深沟槽隔离结构包括:第三导电层和位于所述第三导电层和所述基底之间的线性层;所述第二深沟槽隔离结构还包括:位于所述第一导电层、所述第二导电层分别与所述基底之间的线性层。

7、可选的,所述线性层和所述绝缘层为一体结构。

8、可选的,所述第一导电层、所述第二导电层和所述第三导电层中至少1个为掺杂的多晶硅层。

9、可选的,所述第一导电层、所述第二导电层和所述第三导电层中至少1个,背向基底一侧的掺杂浓度大于朝向基底一侧的掺杂浓度。

10、可选的,沿平行所述基底的表面且垂直所述第二方向的堆叠方向,所述介质层的尺寸在50nm至300nm范围内。

11、可选的,还包括:互连结构,所述互连结构与所述感光元件、所述第一深沟槽隔离结构、所述第一导电层和所述第二导电层分别电连接。

12、可选的,所述互连结构包括:第一插塞,所述第一插塞与所述感光元件电连接的;第二插塞,所述第二插塞与所述第一深沟槽隔离结构电连接;第三插塞,所述第三插塞与所述第二导电层电连接;第四插塞,所述第四插塞与所述第一导电层电连接;第一互连层,所述第一互连层与所述第一插塞、所述第二插塞和所述第三插塞均电连接;第二互连层,所述第二互连层与所述第四插塞电连接。

13、可选的,所述互连结构还包括:第五插塞,所述第五插塞与所述第一深沟槽隔离结构电连接;第三互连层,所述第三互连层与所述第五插塞电连接。

14、可选的,沿所述第一方向,所述第二插塞和所述第五插塞分别位于所述第一深沟槽隔离结构的两端,沿所述第二方向,所述第三插塞和所述第四插塞分别位于所述第二深沟槽隔离结构的两端。

15、而且,本发明还提高一种光探测器,包括:像素单元,所述像素单元为本发明的像素单元。

16、可选的,所述光探测器为硅光电倍增管,所述光电探测器包括:多个像素单元,多个像素单元的感光元件并联。

17、和一种光探测器的形成方法,包括:

18、形成基底;在所述基底内形成电绝缘的第一深沟槽隔离结构和第二深沟槽隔离结构,所述第一深沟槽隔离结构沿第一方向延伸,所述第二深沟槽隔离结构沿第二方向延伸,所述第一方向与所述第二方向相交;其中,所述第二深沟槽隔离结构包括:第一导电层和第二导电层以及位于所述第一导电层和第二导电层之间的介质层,所述第一导电层、所述介质层和所述第二导电层的堆叠方向平行所述基底的表面且垂直所述第二方向;在所述第一深沟槽隔离结构和所述第二深沟槽隔离结构包围的基底内形成感光元件。

19、可选的,还包括:在第一深沟槽隔离结构和第二深沟槽隔离结构相交位置的基底内形成绝缘件。

20、可选的,在所述基底内形成第一深沟槽隔离结构和第二深沟槽隔离结构的步骤包括:在所述基底内形成沟槽网络,所述沟槽网络包括沿第一方向延伸的第一沟槽和沿第二方向延伸的第二沟槽;在所述第一沟槽和所述第二沟槽相交的位置形成绝缘件以阻断所述第一沟槽和所述第二沟槽;形成位于第一沟槽内的第三导电层和分别位于第二沟槽的相对的侧壁上的所述第一导电层、所述第二导电层;在所述第一导电层和所述第二导电层之间形成介质层。

21、可选的,在所述基底内形成沿第一方向延伸的第一沟槽和沿第二方向延伸的第二沟槽的步骤中,所述第一沟槽包括:功能区域和隔离区域,沿所述第一方向,所述隔离区域位于所述功能区域的两端;所述第二沟槽包括:功能区域和隔离区域,沿所述第二方向,所述隔离区域位于所述功能区域的两端;形成绝缘件以阻断所述第一沟槽和所述第二沟槽的步骤中,在所述隔离区域形成所述绝缘件。

22、可选的,隔离区域的沟槽的宽度小于功能区域的沟槽宽度;形成绝缘件以阻断所述第一沟槽和所述第二沟槽的步骤包括:形成线性层,所述线性层覆盖所述第一沟槽的底部和侧壁以及第二沟槽的底部和侧壁,其中所述线性层填充满所述第一沟槽的隔离区域和第二沟槽的隔离区域以形成所述绝缘件;形成所述第一导电层、所述第二导电层和所述第三导电层的步骤中,所述第三导电层位于所述第一沟槽的底部和侧壁的线性层上,所述第一导电层和所述第二导电层分别位于所述第二沟槽的底部和侧壁的线性层上。

23、可选的,形成所述第一导电层、所述第二导电层和所述第三导电层的步骤包括:形成导电材料层,所述导电材料层填充所述第一沟槽且覆盖所述第二沟槽的侧壁和底部;去除所述第二沟槽底部上的部分导电材料层以露出所述第二沟槽的底部;在所述第一导电层和所述第二导电层之间形成介质层的步骤中,在底部露出的所述第二沟槽内填充满所述介质层。

24、与现有技术相比,本发明的技术方案具有以下优点:

25、本发明技术方案中,与所述感光元件电连接的所述第二深沟槽隔离结构包括:第一导电层和第二导电层以及介质层;而且所述感光元件与所述深沟槽隔离结构串联。第一深沟槽隔离结构适宜于作为被动猝灭用的猝灭电阻,所述第二深沟槽隔离结构适宜于作为快速输出用的电容结构,通过对深沟槽隔离结构以及纵向空间的利用实现电阻、电容的同片集成,无需额外占用芯片面积,能够有效突破光敏区面积限制,能够有效增大感光元件的有效占用面积的填充系数,有利于提升光子转换效率。

26、本发明可选方案中,通过导电材料层形成所述第一导电层、所述第二导电层和所述第三导电层。通过一步材料沉积工艺形成所述第一导电层、第二导电层和第三导电层能够有效的简化工艺步骤。

27、本发明可选方案中,通过形成沟槽网络以形成第一沟槽和第二沟槽,进而利用使线性层填充满所述第一沟槽的隔离区域和第二沟槽的隔离区域以形成所述绝缘件,实现阻断所述第一沟槽和所述第二沟槽以实现第一深沟槽隔离结构和所述第二深沟槽隔离的分段。所述沟槽网络的形状定义了第一深沟槽隔离结构和所述第二深沟槽隔离的分布形状,无需单独的刻蚀掩模,也无需单独的注入掩模,能够有效减少掩模使用数量,有利于工艺成本控制,有利于工艺流程简化。

- 还没有人留言评论。精彩留言会获得点赞!