PCIE电连接器的制作方法

pcie电连接器

技术领域

1.本技术涉及电子器件技术领域,更详而言之,有关一种可抑制串音干扰的 pcie电连接器。

背景技术:

2.pcie电连接器被广泛运用到各种电子设备上进行信号传输之接口,且因应电子设备的特殊需求及发展,pcie电连接器被要求具备向更高频段传输高速信号能力,使电子设备有效信号传输速度更加提升。然而,pcie电连接器在高频段传输高速信号时,容易产生耦合的串音干扰,而使高速信号的传输产生干扰衰减,进而限制电子设备有效信号传输速度提升。

3.由上可知,如何解决一种pcie电连接器在高频段传输高速信号时容易产生耦合的串音干扰的问题,以提升电子设备有效信号传输速度,实为所属技术领域人士所亟待解决的问题。

技术实现要素:

4.鉴于上述现有技术的缺点,本技术提供一种pcie电连接器,所述pcie电连接器包括:第一高速传输端子对,所述第一高速传输端子对具有第一高速传输信号端子和第一高速传输接地端子;第二高速传输端子对,所述第二高速传输端子对具有第二高速传输信号端子和第二高速传输接地端子;以及桥接导电件,所述桥接导电件跨过所述第一高速传输信号端子和所述第二高速传输信号端子,而桥接所述第一高速传输接地端子与所述第二高速传输接地端子,使所述第一高速传输接地端子与所述第二高速传输接地端子共同并联串接,而抑制所述第一高速传输端子对与所述第二高速传输端子对之间的串音干扰。

5.优选地,在本技术的pcie电连接器中,所述桥接导电件具有桥接导电件本体、第一弹性抵接脚和第二弹性抵接脚,所述第一弹性抵接脚和所述第二弹性抵接脚分别弹性抵接所述第一高速传输接地端子和所述第二高速传输接地端子,而所述桥接导电件本体电性连接所述第一弹性抵接脚和所述第二弹性抵接脚,以桥接所述第一高速传输接地端子与所述第二高速传输接地端子。

6.优选地,在本技术的pcie电连接器中,所述桥接导电件为金属导体或导电塑料体。

7.相较于现有技术,本技术所提供的pcie电连接器可借由桥接导电件桥接各个高速传输端子对的接地端子,以使各个高速传输端子对的接地端子共同并联串接,而让各个高速传输端子对在高频段传输高速信号时产生信号干扰衰减的程度大幅抑制,进而提高运用本技术pcie电连接器的电子设备有效信号传输速度。

附图说明

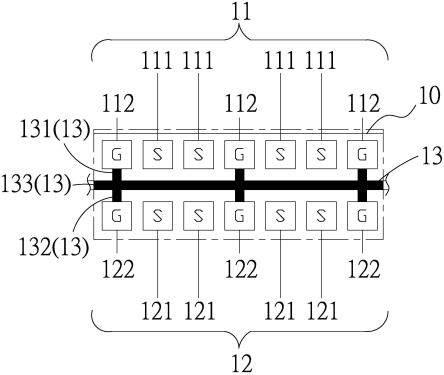

8.图1为本技术之pcie电连接器的实施例的立体示意图。

9.图2为本技术之pcie电连接器的实施例的分解示意图。

10.图3为本技术之pcie电连接器的实施例的侧视示意图。

11.图4为图3所示之pcie电连接器沿线段aa截切的截面示意图。

12.图5为图3所示之pcie电连接器沿线段bb截切的截面示意图。

13.图6为本技术之pcie电连接器的实施例的传输端子对的结构形式示意图。

14.符号说明:

[0015]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

pcie电连接器

[0016]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

胶芯

[0017]

11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一高速传输端子对

[0018]

111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一高速传输信号端子

[0019]

112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一高速传输接地端子

[0020]

12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二高速传输端子对

[0021]

121

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二高速传输信号端子

[0022]

122

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二高速传输接地端子

[0023]

13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

桥接导电件

[0024]

131

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

桥接导电件本体

[0025]

132

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一弹性抵接脚

[0026]

133

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二弹性抵接脚

具体实施方式

[0027]

以下内容将搭配附图,借由特定的具体实施例说明本技术的技术内容,熟悉此技术之人士可由本说明书所公开的内容轻易地了解本技术的其他优点和功效。本技术亦可借由其他不同的具体实施例加以施行或应用。本说明书中的各项细节亦可基于不同观点和应用,在不背离本技术之精神下,进行各种修饰和变更。尤其是,在附图中各个组件的比例关系及相对位置仅具示范性用途,并非代表本技术实施的实际状况。

[0028]

针对本技术技术公开的实施例说明,请一并参阅图1至图6。

[0029]

本技术提供一种pcie电连接器,所提供的pcie电连接器焊接于电子设备的电路基板以提供传输高速信号。如图2的实施例所示,pcie电连接器1包括胶芯10、第一高速传输端子对11、第二高速传输端子对12和桥接导电件13。

[0030]

所述第一高速传输端子对11嵌设于胶芯10的第一侧,且第一高速传输端子对11具有至少一第一高速传输信号端子111和至少一第一高速传输接地端子 112。所述胶芯10令第一高速传输信号端子111与第一高速传输接地端子112 分别错开,而避免第一高速传输信号端子111与第一高速传输接地端子112间发生电性短接。

[0031]

在上述实施例中,第一高速传输端子对11具有多根第一高速传输信号端子 111和多根第一高速传输接地端子112,如图6的实施例所示,每两根第一高速传输接地端子112之间设置有两根第一高速传输信号端子111,使第一高速传输端子对11构成gssgssg传输端子对的结构形式,其中,g为ground、s为signal,但不以此为限,在本技术的实施例中,每两根第一高速传输接地端子112之间设置有一根第一高速传输信号端子111,使第一高速传输端子对11构成gsgsg 传输端子对的结构形式。

[0032]

所述第二高速传输端子对12嵌设于胶芯10的第二侧,且第二高速传输端子对12具

有至少一第二高速传输信号端子121和至少一第二高速传输接地端子 122。所述胶芯10令第二高速传输信号端子121与第二高速传输接地端子122 分别错开,而避免第二高速传输信号端子121与第二高速传输接地端子122间发生电性短接。

[0033]

在上述实施例中,第二高速传输端子对12具有多根第二高速传输信号端子 121和多根第二高速传输接地端子122,如图6的实施例所示,每两根第二高速传输接地端子122之间设置有一根第二高速传输信号端子121,使第二高速传输端子对12构成gsgsg传输端子对的结构形式,但不以此为限,如图6的实施例所示,每两根第二高速传输接地端子122之间设置有两根第二高速传输信号端子121,使第二高速传输端子对12构成gssgssg传输端子对的结构形式,其中, g为ground、s为signal。

[0034]

所述桥接导电件13例如为金属导体或导电塑料体,且具有桥接导电件本体 131、第一弹性抵接脚132和第二弹性抵接脚133。所述桥接导电件本体131跨过第一高速传输信号端子111和第二高速传输信号端子121,第一弹性抵接脚 132和第二弹性抵接脚133分别弹性抵接第一高速传输接地端子112和第二高速传输接地端子122,而桥接导电件本体131电性连接第一弹性抵接脚132和第二弹性抵接脚133,以达成桥接第一高速传输接地端子112与第二高速传输接地端子122,使第一高速传输接地端子112与第二高速传输接地端子122共同并联串接,借此,抑制第一高速传输端子对11与第二高速传输端子对12之间产生耦合的串音干扰。

[0035]

综上所述,本技术所提供的pcie电连接器可借由桥接导电件桥接各个高速传输端子对的接地端子,以使各个高速传输端子对的接地端子共同并联串接,而抑制各个高速传输端子对之间产生耦合的串音干扰,让各个高速传输端子对在高频段传输高速信号时产生信号干扰衰减的程度大幅降低,进而提高运用本技术pcie电连接器的电子设备的有效信号传输速度。

[0036]

上述实施例仅例示性说明本技术的原理和功效,而非用于限制本技术。任何熟习此项技术之人士均可在不违背本技术之精神及范畴下,对上述实施例进行修饰和改变。因此,本技术的权利保护范围,应如本技术的权利要求书所列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1