一种DFN5060引线框架及封装元件的制作方法

一种dfn5060引线框架及封装元件

技术领域

1.本实用新型涉及半导体封装制造技术领域,特别是一种dfn5060引线框架及封装元件。

背景技术:

2.dfn5060是小型电子元器件的一种芯片封装类型。原来的dfn5060封装元件为单芯设计,产品功能单一,不利于电路集成化,如申请号为cn201920827541.x提供的一种新型dfn5060封装元件及封装框架。

技术实现要素:

3.本实用新型的目的在于:针对现有技术dfn5060封装元件采用单芯设计,不利于电路集成化的问题,提供一种dfn5060引线框架及封装元件。

4.为了实现上述目的,本实用新型采用的技术方案为:

5.一种dfn5060引线框架,包括框架本体,框架本体设有多个芯片安装部,每个芯片安装部包括至少两个芯片安置区,芯片安置区用于承装芯片。

6.本实用新型基于dfn5060芯片封装结构,增加了封装内用于承装芯片的芯片安置区,使新型dfn5060引线框架的每个芯片安装部处可以同时封装两颗以上芯片,这样当应用于pcb板在相同的占用面积下,相比单芯设计本实用新型制成的封装元件产品可以实现更多的功能,利于提高电路集成化。

7.优选地,相邻两个芯片安置区并排布置,且在厚度方向上交错设置,使封装时相邻两个芯片安置区的其中一个能够沉入封装内部、另一个能够外露,利于提高两个芯片之间的爬电间隙,提升相邻两个芯片安置区之间的绝缘性,从而可以支持更高电压的应用。

8.优选地,芯片安置区的数量为两个。

9.优选地,芯片安装部还包括引脚焊接区,芯片安置区和引脚焊接区均延伸出有管脚,管脚处设有阻液槽。

10.优选地,芯片安装部周围设有支撑连筋,支撑连筋处设有阻液槽。

11.阻液槽用于阻挡水汽进入,提升封装气密性。

12.优选地,阻液槽为v形槽。

13.优选地,每两个芯片安装部并排布置形成一个芯片安装单元,在框架本体上布置有12排、20列芯片安装单元。

14.优选地,芯片安装单元两列为一组镜像排列,一组为一个单元布置,相邻的单元之间设有单元分隔槽。

15.优选地,同一单元内的两组芯片安装单元之间还设有多个去浇道孔,多个去浇道孔成列布置,通过去浇道孔用模具冲下塑封残留浇道。

16.一种由上述dfn5060引线框架制成的dfn5060封装元件,包括封装体,封装体内设有装有芯片的芯片安装部,芯片安装部中相邻的两个芯片安置区的其中一个内沉于封装

体、另一个外露于封装体表面。

17.综上所述,由于采用了上述技术方案,本实用新型的有益效果是:

18.1、本实用新型基于dfn5060芯片封装结构,增加了封装内用于承装芯片的芯片安置区,使新型dfn5060引线框架的每个芯片安装部处可以同时封装两颗以上芯片,这样当应用于pcb板在相同的占用面积下,相比单芯设计本实用新型制成的dfn5060封装元件产品可以实现更多的功能,利于提高电路集成化。

19.2、本实用新型框架结构中相邻两个芯片安置区的其中一个能够沉入封装内部、另一个能够外露,利于提高两个芯片之间的爬电间隙,提升相邻两个芯片安置区之间的绝缘性,从而可以支持更高电压的应用。

附图说明

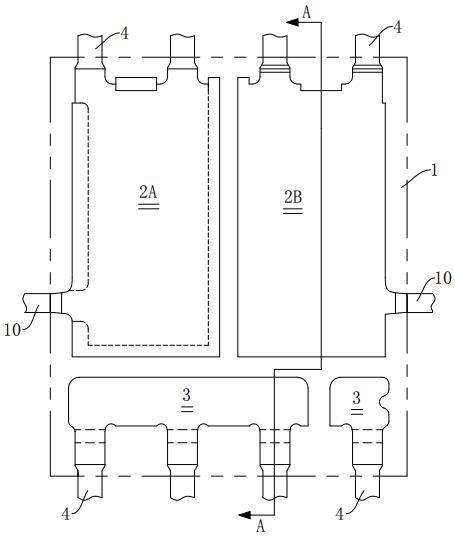

20.图1是dfn5060引线框架的整体结构示意图。

21.图2是芯片安装部的正面结构示意图。

22.图3是图2中a-a向截面图。

23.图4是图3中b部放大图。

24.图5是框架中单个芯片安装单元的结构示意图。

25.图6是框架的两个单元结构示意图。

26.图7是dfn5060封装元件产品的背面图。

27.图标:1-芯片安装部;2a-第一芯片安置区;2b-第二芯片安置区;3-引脚焊接区;4-管脚;5-阻液槽;6-框架本体;7-芯片安装单元;8-单元分隔槽;9-去浇道孔;10-支撑连筋;11-封装体。

具体实施方式

28.下面结合附图,对本实用新型作详细的说明。

29.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本实用新型,并不用于限定本实用新型。

30.实施例1

31.一种dfn5060引线框架,如图1-图6所示,包括框架本体6,框架本体6设有多个芯片安装部1,每个芯片安装部1包括至少两个芯片安置区,芯片安置区用于承装芯片。

32.本实施例基于dfn5060芯片封装结构,增加了封装内用于承装芯片的芯片安置区,使新型dfn5060引线框架的每个芯片安装部1处可以同时封装两颗以上芯片,这样当应用于pcb板在相同的占用面积下,相比单芯设计该引线框架制成的封装元件产品可以实现更多的功能,利于提高电路集成化。

33.进一步地,相邻两个芯片安置区并排布置,且在厚度方向上交错设置,使封装时相邻两个芯片安置区的其中一个能够沉入封装内部、另一个能够外露,利于提高两个芯片之间的爬电间隙,提升相邻两个芯片安置区之间的绝缘性,从而可以支持更高电压的应用。本实施例每个芯片安装部1中优选设置芯片安置区的数量为两个,分别为第一芯片安置区2a和第二芯片安置区2b,如图2。

34.如图2-图4,芯片安装部1还设有两个引脚焊接区3,两个引脚焊接区3分别延伸引出三个和一个管脚4支出并与框架本体6一体连接,两个芯片安置区均分别引出两个管脚4,芯片安置区引出的四个管脚4与引脚焊接区3引出的四个管脚4对称设置。芯片安装部1周边还设有支撑连筋10与框架本体6一体连接,支撑连筋10从两侧分别延伸连接至两个芯片安置区。管脚4处和支撑连筋10处均设有阻液槽5,位于焊盘与封装位置交接边缘附近,可有效提升界面粘接强度,同时阻挡外部环境水汽进入封装体11,提升封装气密性,从而降低分层的发生,保证产品质量。优选阻液槽5为v形槽,也可为w形等其它槽体形状。

35.如图2、图5所示,在长为299.6

±

0.1mm、宽为93

±

0.04mm的框架本体6中,每两个芯片安装部1并排布置形成一个芯片安装单元7,在框架本体6上布置有12排、20列芯片安装单元7,总共步骤480个芯片安装部1,框架密度高,有效提高了材料利用率,利于节约生产成本。

36.如图1、图6所示,芯片安装单元7两列为一组镜像排列,一组为一个单元布置,相邻的单元之间设有单元分隔槽8。同一单元内的两组芯片安装单元7之间还设有多个去浇道孔9,多个去浇道孔9成列布置,通过去浇道孔9用模具冲下塑封残留浇道。

37.实施例2

38.基于实施例1,本实施例提供一种由上述dfn5060引线框架制成的dfn5060封装元件,如图7,包括封装体11,封装体11内设有装有芯片的芯片安装部1,芯片安装部1中相邻的两个芯片安置区的其中一个内沉于封装体11内、另一个外露于封装体11表面。

39.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1