封装结构的制作方法

1.本实用新型是关于半导体制造技术领域,特别是关于一种封装结构。

背景技术:

2.晶圆级芯片封装(wafer level chip size packaging,wlcsp)技术是对整片晶圆进行封装测试后再切割得到单个成品芯片的技术。经晶圆级芯片封装技术封装后的芯片达到了高度微型化,芯片成本随着芯片的减小和晶圆尺寸的增大而显著降低。该技术顺应了市场对微电子产品日益轻、小、短、薄化和低价化的要求,从而成为当前封装领域的热点和发展趋势。

3.tsv(硅通孔技术)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直通孔,实现芯片之间互连的最新技术。与以往ic封装键合和使用凸点的叠加技术不同,tsv能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,大大改善芯片速度和低功耗的性能。

4.现有的晶圆级封装方法中对芯片进行封装时,芯片的厚度在150μm~180μm,通过刻蚀芯片形成暴露焊垫的过孔,然后在孔内沉积绝缘层,但是由于芯片厚度大,tsv形成的孔的深宽比超过3:1,刻蚀后,晶圆上形成的孔均一性差,整片晶圆翘曲严重,最终的封装良率很低,而且孔内表面及底部的绝缘层覆盖率低。

5.公开于该背景技术部分的信息仅仅旨在增加对本实用新型的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现要素:

6.本实用新型的目的在于提供一种封装结构,其能够可以解决现有技术中刻蚀孔均一性差以及孔内形成绝缘层覆盖率低的问题。

7.为实现上述目的,本实用新型的实施例提供了一种封装结构,包括:

8.芯片单元,包括相对的第一表面和第二表面,所述第一表面具有感应区和焊垫,所述焊垫与所述感应区电耦合,所述芯片单元的第二表面设置有贯穿所述芯片单元的过孔,所述过孔用于露出所述焊垫,所述芯片单元的厚度小于60μm;

9.保护盖板,与所述芯片单元的第一表面相对;

10.基板,与所述芯片单元的第二表面相对,所述基板上开设有与所述过孔连通的通孔;

11.绝缘层,至少覆盖于所述过孔的内壁;

12.焊接凸起,设置于所述基板背离所述芯片单元的表面,所述焊接凸起通过设置在所述过孔和通孔内的再布线层与所述焊垫电连接。

13.在本实用新型的一个或多个实施方式中,所述过孔为直通孔,和/或所述通孔为直通孔。

14.在本实用新型的一个或多个实施方式中,所述过孔的深度小于所述过孔的宽度。

在本实用新型的一个或多个实施方式中,所述过孔的宽度为40μm~60μm。

15.在本实用新型的一个或多个实施方式中,所述的基板与所述芯片单元的第二表面之间键合。

16.在本实用新型的一个或多个实施方式中,所述绝缘层延伸至所述芯片单元和基板之间。

17.在本实用新型的一个或多个实施方式中,所述的基板与所述芯片单元的第二表面之间键合。

18.在本实用新型的一个或多个实施方式中,所述基板的材料选自玻璃。

19.在本实用新型的一个或多个实施方式中,所述基板的厚度为100μm~120μm。

20.在本实用新型的一个或多个实施方式中,还包括支撑结构,所述支撑结构位于所述芯片单元的第一表面和保护盖板之间,所述感应区位于所述支撑结构与所述保护盖板围成的凹槽内。

21.与现有技术相比,本实用新型的封装方法先对芯片进行减薄,降低芯片的厚度,然后刻蚀形成过孔,如此获得的过孔均一性好,而且绝缘层在过孔内壁的覆盖率高。

附图说明

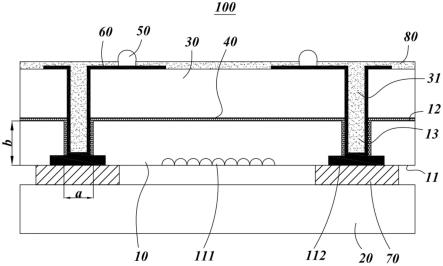

22.图1是根据本实用新型实施例1的封装结构的示意图;

23.图2a~图2h是根据本实用新型实施例2的封装结构制作流程的中间结构示意图;

24.图3是根据本实用新型实施例3的晶圆的结构的俯视图。

具体实施方式

25.下面结合附图,对本实用新型的具体实施方式进行详细描述,但应当理解本实用新型的保护范围并不受具体实施方式的限制。

26.除非另有其它明确表示,否则在整个说明书和权利要求书中,术语“包括”或其变换如“包含”或“包括有”等等将被理解为包括所陈述的元件或组成部分,而并未排除其它元件或其它组成部分。

27.实施例1

28.如图1所示,根据本实用新型优选实施方式的一种封装结构100,包括芯片单元10、保护盖板20、基板30、绝缘层40和焊接凸起50。芯片单元10包括相对的第一表面11和第二表面12,所述第一表面具有感应区111和焊垫112,所述焊垫112与所述感应区111电耦合,所述芯片单元10的第二表面12设置有贯穿所述芯片单元10的过孔13,所述过孔13用于露出所述焊垫112;保护盖板20与所述芯片单元10的第一表面11相对;基板30与所述芯片单元10的第二表面12相对,所述基板30上开设有与所述过孔13连通的通孔31;绝缘层40至少覆盖于所述过孔13的内壁;焊接凸起50设置于所述基板30背离所述芯片单元10的表面,所述焊接凸起50通过设置在所述过孔13和通孔31内的再布线层60与所述焊垫112电连接。

29.在一实施例中,芯片单元10的感应区111设置有阵列排布的多个像素点,芯片单元10可以为电容式感应芯片,如可以为指纹识别芯片。

30.在另一实施例中,芯片单元10还可以为感光型芯片,此时为了便于感应区111感光信息,保护盖板20采用透明材料,比如可以采用玻璃,玻璃可以为有机玻璃或无机玻璃。此

时,芯片单元10可以为影像传感芯片。

31.如果芯片单元10太厚,比如厚度大于60μm时,通过tsv刻蚀的过孔均一性差,导致整片芯片单元翘曲严重,最终的封装良率很低。为了解决该问题,本实施例中芯片单元10的厚度可以通过减薄方式控制在60μm以下,厚度比如可以为1μm、5μm、10μm、20μm、30μm、35μm、40μm、45μm、50μm、55μm。理论上芯片单元10的厚度越小越好,并直接暴露出焊垫112。在芯片单元10的厚度相对比较小的情况下,通过tsv刻蚀形成的通孔均一性好。

32.为了进一步提高绝缘层40在过孔13内的覆盖率,本实施例中过孔13的深宽比b/a小于1,在优选的实施例中,过孔13的宽度(内径)为40μm~60μm,更优选为40μm~55μm,比如可以为45μm、47μm、50μm。

33.过孔13用以暴露出焊垫112,以便于焊接凸起50与焊垫112电连接。在一实施例中,过孔13为直通孔,一方面,直通孔的轴线垂直于芯片单元所在表面,另一方面,过孔13沿其轴向方向具有相同的孔径。在其他实施例中,过孔13还可以为斜通孔,其轴线方向与芯片单元所在平面呈一定倾斜的夹角。过孔13的形状还可以为上宽下窄的喇叭状,其内径自上而下渐性变小。过孔13的形状还可以三角孔、方孔等,本实施例仅为示例性说明。

34.经过减薄处理后的芯片单元10的机械强度较弱,为了进一步增强封装结构的机械强度,本实施例在芯片单元10的第二表面12设置一具有一定硬度和厚度的基板30,在一实施例中,基板30可以采用绝缘材料,优选采用玻璃,玻璃可以为有机玻璃或无机玻璃。基板30的设置,一方面要保证封装的强度,另一方面要控制封装的厚度,因此,基板30的厚度为100μm~120μm,优选为100μm~110μm,比如可以为103μm、105μm、108μm。

35.基板30与芯片单元10之间通过键合方式结合,在一实施例中,可以采用硅硅键合。

36.基板30上的通孔31与过孔13连通用以供再布线层60通过,通孔31优选为直通孔,该通孔的轴向垂直于基板30所在平面。在其他实施例中,通孔31还可以为斜通孔。一实施例中,通孔31的内径与过孔13的内径相同,该实施例中,通孔31和绝缘层40顶部之间会形成台阶结构;在一实施例中,通孔31的内径与绝缘层40构成的内径相同,如此,再布线层60可以在平整的内壁表面延伸,再布线层60与通孔31和过孔13内壁表面的结合度更加牢固;另一实施例中,通孔31和过孔13可以形成双层台阶结构,通孔31的平均内径大于过孔13的内径。

37.绝缘层40还延伸至所述芯片单元10和基板30之间。绝缘层40覆盖在过孔13的内壁表面以及裸露的芯片单元的第二表面上,在基板30与芯片单元10键合时,绝缘层40可以夹持在基板30和芯片单元10之间,如此,可以避免绝缘层40的边缘翘边。在一实施例中,绝缘层的材料为二氧化硅。

38.封装结构100还包括支撑结构70,所述支撑结构70位于所述芯片单元10的第一表面11和保护盖板20之间,所述感应区111位于所述支撑结构70与所述保护盖板20围成的凹槽内。

39.封装结构100还包括防焊层80,防焊层80覆盖于再布线层60上和通孔31内。

40.实施例2

41.参图2a至图2h,根据本实用新型实施方式的一种封装方法,包括如下步骤。

42.步骤s101,参图2a,提供芯片单元10,芯片单元10包括相对的第一表面11和第二表面12,所述第一表面具有感应区111和焊垫112,所述焊垫112与所述感应区111电耦合。

43.一实施例中,芯片单元10的感应区111设置有阵列排布的多个像素点,芯片单元10

可以为电容式感应芯片,如可以为指纹识别芯片。在另一实施例中,芯片单元10还可以为感光型芯片,比如影像传感芯片。

44.步骤s102,参图2b,提供一保护盖板20。

45.当芯片单元10为感光型芯片时,为了便于感应区111感光信息,保护盖板20采用透明材料,比如可以采用玻璃,玻璃可以为有机玻璃或无机玻璃。

46.步骤s103,参图2c,在保护盖板20的表面制作支撑结构70。

47.步骤s104,参图2d,将保护盖板20结合于所述芯片单元10的第一表面11。其中,支撑结构70位于所述芯片单元10的第一表面11和保护盖板20之间,所述感应区111位于所述支撑结构70与所述保护盖板20围成的凹槽13内。

48.步骤s105,参图2e,对芯片单元10的第二表面12进行减薄,控制所述芯片单元10的厚度小于60μm。减薄可以通过机械研磨或是化学刻蚀等方式。

49.步骤s106,参图2f,在所述芯片单元10的第二表面12形成贯穿所述芯片单元的过孔13,所述过孔13露出所述焊垫112。

50.过孔13的深宽比b/a小于1,在优选的实施例中,过孔13的宽度(内径)为40μm~60μm,更优选为40μm~55μm,比如可以为45μm、47μm、50μm。过孔13用以暴露出焊垫112,以便于焊接凸起50与焊垫112电连接。在一实施例中,过孔13为直通孔,一方面,直通孔的轴线垂直于芯片单元所在表面,另一方面,过孔13沿其轴向方向具有相同的孔径。

51.步骤s107,参图2g,形成覆盖在芯片单元10第二表面12和过孔13侧壁的绝缘层40。

52.步骤s108,参图2h,提供一基板30,在基板30上形成与所述过孔13连通的通孔31。

53.将基板30通过键合方式结合于所述芯片单元10的第二表面12上。

54.基板30可以采用玻璃,玻璃可以为有机玻璃或无机玻璃。基板30的设置,一方面要保证封装的强度,另一方面要控制封装的厚度,因此,基板30的厚度为100μm~120μm,优选为100μm~110μm,比如可以为103μm、105μm、108μm。

55.步骤s109,参图1,在基板30背离所述芯片单元10的表面制作焊接凸起50,所述焊接凸起50通过设置在所述过孔13和通孔内的再布线层60与所述焊垫112电连接。最后制作覆盖于再布线层60上和通孔31内的防焊层80。

56.步骤s103中,也可以先在芯片单元10的第一表面11上制作支撑结构70,然后再将保护盖板20与芯片单元10进行结合。

57.步骤s108中,也可以先将基板30与芯片单元10进行键合,然后再在基板30上形成通孔31。

58.实施例3

59.参图3,以及图2a至图2h,根据本实用新型实施方式的一种封装方法,包括如下步骤。

60.步骤s201,提供一晶圆200,所述晶圆包括阵列排布的多个芯片单元100。

61.其中图2a为图3中在a-a’方向的剖视图。每个所述芯片单元分别包括包括相对的第一表面11和第二表面12,所述第一表面具有感应区111和焊垫112,所述焊垫112与所述感应区111电耦合。

62.一实施例中,芯片单元10的感应区111设置有阵列排布的多个像素点,芯片单元10可以为电容式感应芯片,如可以为指纹识别芯片。在另一实施例中,芯片单元10还可以为感

光型芯片,比如影像传感芯片。

63.步骤s202,参图2b,提供一保护盖板20。

64.当芯片单元10为感光型芯片时,为了便于感应区111感光信息,保护盖板20采用透明材料,比如可以采用玻璃,玻璃可以为有机玻璃或无机玻璃。

65.步骤s203,参图2c,在保护盖板20的表面制作支撑结构70。

66.步骤s204,参图2d,将保护盖板20结合于所述芯片单元10的第一表面11。其中,支撑结构70位于所述芯片单元10的第一表面11和保护盖板20之间,所述感应区111位于所述支撑结构70与所述保护盖板20围成的凹槽13内。

67.步骤s205,参图2e,对芯片单元10的第二表面12进行减薄,控制所述芯片单元10的厚度为小于60μm。减薄可以通过机械研磨或是化学刻蚀等方式。

68.步骤s206,参图2f,在所述芯片单元10的第二表面12形成贯穿所述芯片单元的过孔13,所述过孔13露出所述焊垫112。

69.过孔13的深宽比b/a小于1,在优选的实施例中,过孔13的宽度(内径)为40μm~60μm,更优选为40μm~55μm,比如可以为45μm、47μm、50μm。过孔13用以暴露出焊垫112,以便于焊接凸起50与焊垫112电连接。在一实施例中,过孔13为直通孔,一方面,直通孔的轴线垂直于芯片单元所在表面,另一方面,过孔13沿其轴向方向具有相同的孔径。

70.步骤s207,参图2g,形成覆盖在芯片单元10第二表面12和过孔13侧壁的绝缘层40。

71.步骤s208,参图2h,提供一基板30,在基板30上形成与所述过孔13连通的通孔31。

72.将基板30通过键合方式结合于所述芯片单元10的第二表面12上。

73.基板30可以采用玻璃,玻璃可以为有机玻璃或无机玻璃。基板30的设置,一方面要保证封装的强度,另一方面要控制封装的厚度,因此,基板30的厚度为100μm~120μm,优选为100μm~110μm,比如可以为103μm、105μm、108μm。

74.步骤s209,参图1,在基板30背离所述芯片单元10的表面制作焊接凸起50,所述焊接凸起50通过设置在所述过孔13和通孔内的再布线层60与所述焊垫112电连接。最后制作覆盖于再布线层60上和通孔31内的防焊层80。

75.步骤s210,参图3,沿着切割沟道201,通过切割工艺分割所述晶圆200,形成多个芯片单元的封装结构100。

76.步骤s203中,也可以先在芯片单元10的第一表面11上制作支撑结构70,然后再将保护盖板20与芯片单元10进行结合。

77.步骤s208中,也可以先将基板30与芯片单元10进行键合,然后再在基板30上形成通孔31。

78.前述对本实用新型的具体示例性实施方案的描述是为了说明和例证的目的。这些描述并非想将本实用新型限定为所公开的精确形式,并且很显然,根据上述教导,可以进行很多改变和变化。对示例性实施例进行选择和描述的目的在于解释本实用新型的特定原理及其实际应用,从而使得本领域的技术人员能够实现并利用本实用新型的各种不同的示例性实施方案以及各种不同的选择和改变。本实用新型的范围意在由权利要求书及其等同形式所限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1