一种提高芯片ESD性能的封装结构的制作方法

一种提高芯片esd性能的封装结构

技术领域

1.本实用新型涉及芯片封装技术领域,尤其涉及一种提高芯片esd性能的封装结构。

背景技术:

2.esd(electronic-static discharge,静电放电)是ic(integrate circuit,集成电路)生产制造过程中非常普遍的现象,esd保护电路也是集成电路设计的重要部分,它直接影响了ic的性能和使用寿命。

3.为了保护芯片内部电路,需要提高其esd性能,而提高esd性能的本质是减小esd电流泄放通路的电阻。在芯片设计和芯片级封装中,减小esd电流泄放通路的电阻,一般可使用以下两种做法:

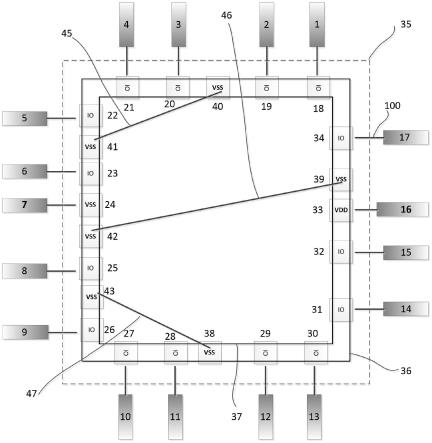

4.第一种做法,如图1所示,图中35为芯片内部,18~23,25~32,34为芯片普通io;33为电源vdd io;24为地io vss;1~17为封装引脚;36为esd电源环,电源环将所有io的vdd线连接在一起;37为esd地环,地环将所有io的vss线连接在一起;100为封装打线。通过采用esd电源环或者地环作为esd电流泄放通路,通过增加esd电源环36或地环37的宽度,以此来减小电源环36或地环37的电阻,达到提高esd性能的目的。

5.第二种做法,如图2所示,采用带有金属环或者金属基座进行封装,图中1~37和图1中一样,44是封装金属环,金属环与图中7封装引脚连接,38~43是在esd环中插入的vss io。通过将多插入的vss io的pad封装打线到金属环上,增加esd电流泄放通路,减小esd电流泄放通路电阻,达到提高esd性能的目的。

6.在图1和图2中,对普通io电路、地io vss电路、电源vdd io电路进行说明。普通io电路,如图3所示,图中p1为pmos,n1为nmos,vdd和vss分别为普通io的电源线和地线,pad为封装打线的位置,封装打线是指利用金线或者铜线将io的pad与封装引脚连接在一起;图4所示为地io vss电路图,p1,n1,vdd,vss和pad的解释和图3一样,区别是pad和vss连接在一起,图4中pad可以通过封装打线的形式与封装引脚,封装中的金属环(或者封装中的金属基座,如图2中44),或者封装飞线连接在一起;图5所示为电源vdd io电路图,p1,n1,vdd,vss和pad的解释和图4一样,唯一区别是pad与vdd连接在一起。

7.第一种方法的缺点是,通过增加esd电源环或地环的宽度,将带来芯片面积的增大,使芯片成本增加。第二种方法的缺点是,必须使用带有金属环或者金属基座的封装,有些应用中的封装是固定,并不支持这种类型的封装。带有金属环或者金属基座的封装的成本要高于无金属环或者金属基座的封装。

技术实现要素:

8.为解决背景技术中存在的技术问题,本实用新型提出一种提高芯片esd性能的封装结构,可以有效地降低esd泄放电路通路电阻,实现增强esd性能的目的。

9.本实用新型提出一种提高芯片esd性能的封装结构,在芯片上包括多个普通io、电源vdd io和地vss io,电源环将所有io的vdd线连接在一起,地环将所有io的vss线连接在

一起,其特征在于,在芯片上插入多个辅助vss io,多个辅助vss io与地环连接,通过封装飞线将插入的多个辅助vss io两两连接。

10.优选地,辅助vss io的数量为偶数。

11.优选地,辅助vss io可插入在任意相邻两个或多个io之间,以使esd电流最大限度地通过封装飞线进行传导。

12.优选地,esd电流通过封装飞线进行传导。

13.在本实用新型中,通过在芯片上插入偶数个辅助vss io,并通过封装飞线的形式将插入的辅助vss io两两连接,以增强芯片esd的性能;辅助vss io插入在任意相邻两个io之间,具体插入的辅助vss io的数量和位置,只要使电源io到地io、普通io到电源io、普通io到地io、每两个普通io之间的电路泄放通路电阻符合芯片的esd要求即可。

附图说明

14.图1为现有技术中第一种芯片封装结构的示意图。

15.图2为现有技术中另一种芯片封装结构的示意图。

16.图3为普通io电路图。

17.图4为地io vss电路图。

18.图5为电源vdd io电路图。

19.图6为本实用新型提出的第一种芯片封装结构的示意图。

20.图7为本实用新型提出的第二种芯片封装结构的示意图。

21.图8为本实用新型提出的第三种芯片封装结构的示意图。

22.图9为图1的电路泄放通路的等效电路。

23.图10为图6的电路泄放通路的等效电路。

具体实施方式

24.本实用新型实施例提出了一种提高芯片esd性能的封装结构,在芯片上包括多个普通io、电源vdd io和地vss io,电源环将所有io的vdd线连接在一起,地环将所有io的vss线连接在一起,在芯片上插入多个辅助vss io,多个辅助vss io与地环连接,通过封装飞线将插入的多个辅助vss io两两连接。辅助vss io的数量为偶数,辅助vss io插入在任意相邻两个或多个io之间,以使esd电流最大限度地通过封装飞线进行传导。

25.通过在芯片上插入偶数个辅助vss io,并通过封装飞线的形式将插入的vss io两两连接,每个辅助vss io只能打一次封装飞线或者封装打线,都可以达到增强芯片esd的性能;具体插入vss io的数量和位置,只要使电源io到地io,普通io到电源io,普通io到地io,每两个普通io之间的电路泄放通路电阻符合芯片的esd要求即可。

26.参照图6,本实用新型提出实施例提出的第一种芯片封装结构的示意图。

27.图6中1~43和图1中一样,38~42为插入的6个vss io,将40与41的pad用封装飞线45连接,将39与42的pad用封装飞线46连接,38与43的pad用封装飞线47连接,增加esd电流泄放通路,达到降低esd泄放电路通路电阻的目的,从而增强esd性能。

28.参照图7,本实用新型提出实施例提出的第二种芯片封装结构的示意图。

29.图7中1~43和图1中一样,48~55为插入的8个vss io,将48与55的pad用封装飞线

58连接,将49与50的pad用封装飞线57连接,将51与52的pad用封装飞线59连接,将53与54的pad用封装飞线56连接,增加esd电流泄放通路,达到降低esd泄放电路通路电阻的目的,从而增强esd性能.

30.在图7中,可以将49与50的pad,51与48的pad,52与55的pad,53与54的pad分别用封装飞线进行连接起来。

31.参照图8,本实用新型提出实施例提出的第三种芯片封装结构的示意图。

32.图8中1~43,48~59和图7中一样,60和61为插入的2个vss io,在图1基础上一共多插入了10个vss io,将48与55的pad用封装飞线58连接,将49与50的pad用封装飞线57连接,将51与52的pad用封装飞线59连接,将53与54的pad用封装飞线56连接,将60与61的pad用封装飞线62连接,增加esd电流泄放通路,达到降低esd泄放电路通路电阻的目的,从而增强esd性能。

33.为了说明本实用新型有显著减小esd电流泄放通路电阻的效果,我们举例说明,假设vdd对vss进行esd测试。

34.图1的esd电路泄放通路为,电流通过封装引脚16经过vdd io33到达esd电源环36,电流再从esd电源环36的节点33到达esd电源环36的节点24,到达vss io24,电流最后从封装引脚7流出。

35.图9为图1的vdd封装引脚16到vss封装引脚7的电路泄放通路的等效电路,其中v1为esd测试源,d1和d2分别为vdd io16和vss io7的esd保护电路等效二极管,r1为图1中节点33到节点24esd地环的等效电阻。

36.图6的esd电路泄放通路为,电流通过封装引脚16经过vdd io33到达esd电源环36,电流再从esd电源环36的节点33到达esd电源环36的节点39,电流再经过封装飞线46到达esd电源环36的节点42,电流再从esd电源环36的节点42到达esd电源环36的节点24,电流到达vss io24,电流最后从封装引脚7流出。

37.图10为图6的vdd封装引脚16到vss封装引脚7的电路泄放通路的等效电路,其中v1为esd测试源,d3和d4分别为vdd io16和vss io7的esd保护电路等效二极管,r2为图3中节点33到节点39esd地环的等效电阻,r4为图3中节点42到节点24esd地环的等效电阻,r3为图3中封装飞线46的等效电阻。

38.基于d1和d3都是vdd io16的esd保护电路等效二极管,所以d1和d3的压降一样,对于esd的影响是一样,同理,d2和d4都是vss io 7的esd保护电路等效二极管,对于esd的影响也是一样的。图9和图10的区别在于泄放通路电阻的不同,也就是r1和r2+r3+r4的不同,r1,r2,r4是esd电源环36的部分等效电阻,其阻值为欧姆级别。从图1和图6中可以明显看出,r1的阻值远大于r2+r4;r3的阻值是封装飞线46的等效电阻,其阻值为毫欧级别。所以r1的阻值远大于r2+r3+r4,图6的esd性能远强于图1的esd性能。

39.总体来说,本实用新型可以有多种实现方法,不限于图6、图7、图8所列举的实施例。在芯片上插入辅助vss io增强其esd性能的基本原理,通过在芯片上插入偶数个vss io,并通过封装飞线的形式将插入的vss io两两连接,都可以达到增强芯片esd的性能;具体插入vss io的数量和位置,只要使电源io到地io,普通io到电源io,普通io到地io,每两个普通io之间的电路泄放通路电阻符合芯片的esd要求即可。

40.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不

局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,根据本实用新型的技术方案及其实用新型构思加以等同替换或改变,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1