多层堆叠式芯片封装的制作方法

1.本实用新型涉及一种芯片封装,尤指一种多层堆叠式芯片封装。

背景技术:

2.随着科技产业及工艺技术的进步,芯片封装产品不仅追求面积缩小化,同时也追求芯片运算能力的提升化,制造端须不断开发运算能力更强的芯片,然而,芯片的个体运算能力的提升同时也增加了制造端研发与生产的新成本。

3.因此,一种芯片封装产品面积能缩小化且降低制造端成本的多层堆叠式芯片封装,为目前相关产业的迫切期待。

技术实现要素:

4.本实用新型的主要目的在于提供一种多层堆叠式芯片封装,该多层堆叠式芯片封装包含至少两个基板、至少两个电路层、至少两个芯片、至少两个绝缘层及一下部电路层;其中由一第一基板、一第一电路层、一第一芯片及一第一绝缘层构成一下层芯片封装;其中由一第二基板、一第二电路层、一第二芯片及一第二绝缘层构成一上层芯片封装;其中该上层芯片封装为堆叠地位于该下层芯片封装的上方,以此堆叠模式以形成该多层堆叠式芯片封装,以使每一该芯片之间能通过其中一该芯片能对其他每一该芯片进行指令操作,或通过每一该芯片之间的运算功能叠加而能加乘增加总体运算的效能,有效地解决制造端芯片为了封装产品追求面积缩小化须不断开发运算能力更强的芯片而增加成本的问题。

5.为达成上述目的,本实用新型提供一种多层堆叠式芯片封装,该多层堆叠式芯片封装包含至少两个基板、至少两个电路层、至少两个芯片、至少两个绝缘层及一下部电路层;其中每一该基板包括一第一基板及一第二基板位于该第一基板上方而形成一上一下的对应关系,其中该第一基板具有一第一面及相对的一第二面,该第一基板的该第一面上成型设有至少一第一盲孔,其中该第二基板具有一第一面及相对的一第二面,该第二基板的该第一面上成型设有至少一第二盲孔,其中在该第二基板的每一该第二盲孔与该第一基板之间更具有至少一第一穿孔,或在该第二基板的每一该第二盲孔与该第一基板的每一该第一盲孔之间更具有至少一该第一穿孔;其中每一该电路层包括一第一电路层及一第二电路层位于该第一电路层上方而形成一上一下的对应关系,其中该第一电路层设在该第一基板的该第一面上并能延伸设在每一该第一盲孔的内壁面上,其中该第二电路层设在该第二基板的该第一面上并能延伸设在每一该第二盲孔的内壁面上;其中每一该芯片包括一第一芯片及一第二芯片位于该第一芯片上方而形成一上一下的对应关系,其中该第一芯片电性连接地设在该第一电路层上,其中该第二芯片电性连接地设在该第二电路层上;其中每一该绝缘层包括一第一绝缘层及一第二绝缘层位于该第一绝缘层上方而形成一上一下的对应关系,其中该第一绝缘层为以压注技艺覆设在该第一基板的该第一面上,其中该第二绝缘层为以压注技艺覆设在该第二基板的该第一面上;该下部电路层设在该第一基板的该第二面上供用以向外电性连接;其中由该第一基板、该第一电路层、该第一芯片及该第一绝缘层

构成一下层芯片封装;其中由该第二基板、该第二电路层、该第二芯片及该第二绝缘层构成一上层芯片封装;其中该上层芯片封装为堆叠地位于该下层芯片封装的上方,以此堆叠模式以形成该多层堆叠式芯片封装;其中该第一芯片是通过该第一电路层以与该下部电路层电性连接;其中该第二芯片能选择通过该第二电路层并经由每一该第一穿孔以延伸至与该第一芯片电性连接,或选择通过该第二电路层并经由每一该第一穿孔以延伸至与该下部电路层电性连接,以利于芯片封装产品面积能缩小化且降低制造端成本。

6.在本实用新型一较佳实施例中,每一该第二盲孔及每一该第一穿孔的垂直轴心与每一该第一盲孔的垂直轴心相同,以使每一该第二盲孔及每一该第一穿孔与每一该第一盲孔形成一相连通的洞孔。

7.在本实用新型一较佳实施例中,每一该第二盲孔及每一该第一穿孔的垂直轴心与每一该第一盲孔的垂直轴心不相同,以使每一该第二盲孔及每一该第一穿孔与每一该第一盲孔无法相连通。

8.在本实用新型一较佳实施例中,在该下部电路层的下方进一步设有一下部外护层,该下部外护层上具有至少一下部开口,每一该下部开口上分别设有一锡球以对外电性连接。

9.在本实用新型一较佳实施例中,在该多层堆叠式芯片封装上进一步设有一上部基板、一上部电路层、一外部芯片及一上部绝缘层;其中该上部基板设于该第二绝缘层上,该上部基板具有一第一面,在该上部基板的该第一面成型设有至少一上部盲孔,其中在该上部基板的每一该上部盲孔与该第二基板之间更具有至少一上部穿孔,或在该上部基板的每一该上部盲孔与该第二基板的每一该第二盲孔之间更具有至少一该上部穿孔;其中该上部电路层设在该上部基板的该第一面上并能延伸设在每一该上部盲孔的内壁面上;其中该外部芯片电性连接地设在该上部电路层上;其中该上部绝缘层为以压注技艺覆设在该上部基板的该第一面上;其中该外部芯片能选择通过该上部电路层并经由每一该上部穿孔以延伸至与该第二芯片电性连接,或选择通过该上部电路层并经由每一该上部穿孔及每一该第一穿孔以延伸至与该第一芯片电性连接,或选择通过该上部电路层并经由每一该上部穿孔及每一该第一穿孔以延伸至与该下部电路层电性连接。

附图说明

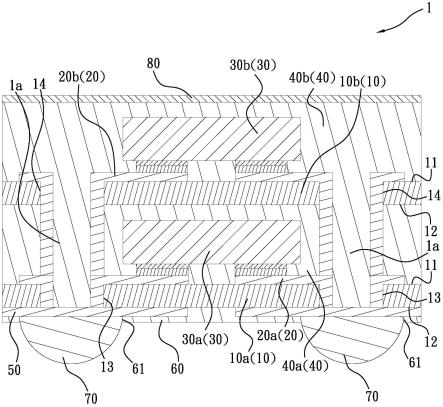

10.图1为本实用新型的多层堆叠式芯片封装具有两个芯片的侧视剖面示意图。

11.图2为本实用新型的第一盲孔与第二盲孔的洞孔不相通的侧视剖面示意图。

12.图3为本实用新型的多层堆叠式芯片封装具有三个芯片的侧视剖面示意图。

13.图4为本实用新型的多层堆叠式芯片封装外部具有一个外部芯片的侧视剖面示意图。

14.图5为本实用新型的第一基板的侧视剖面示意图。

15.图6为在图5中设置第一芯片的示意图。

16.图7为在图6中设置第一绝缘层的示意图。

17.图8为在图7中设置第二基板的示意图。

18.图9为在图8中设置第二电路层的示意图。

19.图10为在图9中设置第二芯片的示意图。

20.图11为在图10中设置第二绝缘层的示意图。

21.附图标记说明:1-多层堆叠式芯片封装;1a-第一穿孔;1b-上部穿孔;1c-第二穿孔;1d-第一层芯片封装;1e-第二层芯片封装;1f-第三层芯片封装;10-基板;10a-第一基板;10b-第二基板;10c-第三基板;11-第一面;12-第二面;13-第一盲孔;14-第二盲孔;15-第三盲孔;20-电路层;20a-第一电路层;20b-第二电路层;20c-第三电路层;30-芯片;30a-第一芯片;30b-第二芯片;30c-第三芯片;40-绝缘层;40a-第一绝缘层;40b-第二绝缘层;40c-第三绝缘层;50-下部电路层;60-下部外护层;61-下部开口;70-锡球;80-上部外护层;81-上部开口;90-上部基板;91-第一面;92-上部盲孔;100-上部电路层;110-上部绝缘层;120-外部芯片。

具体实施方式

22.配合图示,将本实用新型的结构及其技术特征详述如下,其中各图示只用以说明本实用新型的结构关系及相关功能,因此各图示中各元件的尺寸并非依实际比例画制且非用以限制本实用新型。

23.参考图1及图2,本实用新型提供一种多层堆叠式芯片封装1,该多层堆叠式芯片封装1包含至少两个基板10、至少两个电路层20、至少两个芯片30、至少两个绝缘层40及一下部电路层50;其中在该多层堆叠式芯片封装1最上方进一步设有一上部外护层80但不限制如图1及图2所示,以增加对该多层堆叠式芯片封装1的保护而提升产品的良率。

24.每一该基板10包括一第一基板10a及一第二基板10b位于该第一基板10a上方而形成一上一下的对应关系如图1及图2所示,其中该第一基板10a具有一第一面11及相对的一第二面12,该第一基板10a的该第一面11上成型设有至少一第一盲孔13,参考图1及图2,该多层堆叠式芯片封装1具有两个该第一盲孔13但不限制,且每一该第一盲孔13的深度等于该第一基板10a的厚度但不限制;其中该第二基板10b具有一第一面11及相对的一第二面12,该第二基板10b的该第一面11上成型设有至少一第二盲孔14,参考图1及图2,该多层堆叠式芯片封装1具有两个该第二盲孔14但不限制;其中在该第二基板10b的每一该第二盲孔14与该第一基板10a之间更具有至少一第一穿孔1a,或在该第二基板10b的每一该第二盲孔14与该第一基板10a的每一该第一盲孔13之间更具有至少一该第一穿孔1a,参考图1及图2,该多层堆叠式芯片封装1具有两个该第一穿孔1a但不限制,且每一该第二盲孔14的深度等于该第二基板10b的厚度但不限制。

25.每一该电路层20包括一第一电路层20a及一第二电路层20b位于第一电路层20a上方而形成一上一下的对应关系如图1及图2所示,其中该第一电路层20a设在该第一基板10a的该第一面11上并能延伸设在每一该第一盲孔13的内壁面上如图1及图2所示;其中该第二电路层20b设在该第二基板10b的该第一面11上并能延伸设在每一该第二盲孔14的内壁面上如图1及图2所示。

26.每一该芯片30包括一第一芯片30a及一第二芯片30b位于该第一芯片30a上方而形成一上一下的对应关系如图1及图2所示,其中该第一芯片30a电性连接地设在该第一电路层20a上;其中该第二芯片30b电性连接地设在该第二电路层20b上。

27.每一该绝缘层40包括一第一绝缘层40a及一第二绝缘层40b位于该第一绝缘层40a上方而形成一上一下的对应关系如图1及图2所示,其中该第一绝缘层40a为以压注技艺覆

设在该第一基板10a的该第一面11上且包覆地填满该第一芯片30a于该多层堆叠式芯片封装1中所留下的空隙;其中该第二绝缘层40b为以压注技艺覆设在该第二基板10b的该第一面11上且包覆地填满该第二芯片30b于该多层堆叠式芯片封装1中所留下的空隙。

28.该下部电路层50设在该第一基板10a的该第二面12上供用以向外电性连接如图1及图2所示,使该多层堆叠式芯片封装1能通过该下部电路层50与其他电子元件进行电性连接(未图示);其中该第一电路层20a进一步是经由每一该第一盲孔13的内壁面而向下延伸至与该下部电路层50电性连接但不限制如图1及图2所示;其中该第二电路层20b进一步是经由每一该第二盲孔14的内壁面而向下延伸设于每一该第一穿孔1a的内壁面上并延伸至与该第一电路层20a电性连接但不限制如图1及图2所示,或经由每一该第二盲孔14的内壁面及每一该第一穿孔1a的内壁面而向下延伸设于每一该第一盲孔13的内壁面上并延伸至与该下部电路层50电性连接但不限制如图1及图2所示。

29.其中,由该第一基板10a、该第一电路层20a、该第一芯片30a及该第一绝缘层40a构成的一第一层芯片封装1d(如图3所示)为一下层芯片封装但不限制;其中由该第二基板10b、该第二电路层20b、该第二芯片30b及该第二绝缘层40b构成的一第二层芯片封装1e(如图3所示)为一上层芯片封装但不限制;其中该上层芯片封装堆叠地位于该下层芯片封装的上方,以此堆叠模式以形成该多层堆叠式芯片封装1。

30.参考图1及图2,该第一芯片30a是通过该第一电路层20a以与该下部电路层50电性连接;其中该第二芯片30b能选择通过该第二电路层20b并经由每一该第一穿孔1a以延伸至与该第一芯片30a电性连接,或选择通过该第二电路层20b并经由每一该第一穿孔1a以延伸至与该下部电路层50电性连接。

31.通过上述该第一芯片30a及该第二芯片30b(即各芯片30)在该多层堆叠式芯片封装1中的电性连接的关系可知,参考图1及图2,每一该芯片30之间可互相电性连接,使其中一该芯片30(如第二芯片30b)能对其他该芯片30(如第一芯片30a)进行指令操作,或每一该芯片30之间的运算功能叠加而使运算功能加乘增加总体运算的效能,以利于产品的多元化应用而增加产品的市场竞争力。

32.参考图1,每一该第二盲孔14及每一该第一穿孔1a的垂直轴心与每一该第一盲孔13的垂直轴心相同但不限制,以使每一该第二盲孔14及每一该第一穿孔1a与每一该第一盲孔13形成一相连通的洞孔,制造端以此得在成型每一该第二盲孔14时,一同将每一该第一穿孔1a成型出来,以简化制造步骤而节省制造端的成本。

33.参考图2,每一该第二盲孔14及每一该第一穿孔1a的垂直轴心与每一该第一盲孔13的垂直轴心不相同但不限制,以使每一该第二盲孔14及每一该第一穿孔1a与每一该第一盲孔13无法相连通,制造端以此得更多元化安排设计每一该第二盲孔14及每一该第一穿孔1a与每一该第一盲孔13的位置所在处,以利于产品的多元化应用而增加产品的市场竞争力。

34.参考图1及图2,在该下部电路层50的下方进一步设有一下部外护层60但不限制,该下部外护层60上具有至少一下部开口61,每一该下部开口61上分别设有一锡球70以对外电性连接,使该多层堆叠式芯片封装1能通过每一该锡球70与其他电子元件电性连接,如以覆晶技术(flip chip)与其他电子元件进行封装但不限制(未图示)。

35.参考图1、图5至图11,当该多层堆叠式芯片封装1由两层芯片封装所堆叠形成时,

该多层堆叠式芯片封装1的制造方法包含下列步骤但不限制:

36.步骤s1:提供一第一基板10a,该第一基板10a具有一第一面11及相对的一第二面12,该第一基板10a的该第一面11上成型设有至少一第一盲孔13如图5所示;其中该第一基板10a的该第一面11上及每一该第一盲孔13的内壁面上具有一第一电路层20a如图5所示;其中该第一基板10a的该第二面12上具有该下部电路层50如图5所示,该下部电路层50与该第一电路层20a电性连接。

37.步骤s2:在该第一电路层20a上设置一第一芯片30a如图6所示,该第一芯片30a与该第一电路层20a电性连接。

38.步骤s3:在该第一基板10a的该第一面11上以压注技艺覆设置一第一绝缘层40a如图7所示。

39.步骤s4:在该第一绝缘层40a上设置一第二基板10b,该第二基板10b具有一第一面11及相对的一第二面12。

40.步骤s5:在该第二基板10b的该第一面11上成型设至少一第二盲孔14,并同时在该第二基板10b的每一该第二盲孔14与该第一基板10a的每一该第一盲孔13之间更成型设至少第一穿孔1a如图8所示。

41.步骤s6:在该第二基板10b的该第一面11上并能延伸设在每一该第二盲孔14的内壁面上设置该第二电路层20b,且该第二电路层20b经由每一该第一穿孔1a与该第一电路层20a电性连接,如图9所示。

42.步骤s7:在该第二电路层20b上设置一第二芯片30b如图10所示,该第二芯片与该第二电路层电性连接。

43.步骤s8:在该第二基板10b的该第一面11上以压注技艺覆设该第二绝缘层40b,且该第二绝缘层40b包覆地填满该第二芯片30b于该多层堆叠式芯片封装1中所留下的空隙如图11所示。

44.在图3中所示的实施例为本案的该多层堆叠式芯片封装1由三层封装结构所堆叠而成的实施例但不限制,其中每一该基板10之间更包含一第三基板10c位于该第二基板10b上方而形成一上一下的对应关系,该第三基板10c具有一第一面11及相对的一第二面12,该第三基板10c的该第一面11上成型设有至少一第三盲孔15,其中在该第三基板10c的每一该第三盲孔15与该第二基板10b之间更具有至少一第二穿孔1c,或在该第三基板10c的每一该第三盲孔15与该第二基板10b的每一该第二盲孔14之间更具有每一该第二穿孔1c,参考图3,该多层堆叠式芯片封装1具有两个该第二穿孔1c但不限制;其中每一该电路层20之间更包含一第三电路层20c位于该第二电路层20b上方而形成一上一下的对应关系,该第三电路层20c设在该第三基板10c的该第一面11上并能延伸设在每一该第三盲孔15的内壁面上;其中每一该芯片30之间更包含一第三芯片30c位于该第二芯片30b上方而形成一上一下的对应关系,该第三芯片30c电性连接地设在该第三电路层20c上;其中每一该绝缘层40之间更包含一第三绝缘层40c位于该第二绝缘层40b上方而形成一上一下的对应关系,该第三绝缘层40c为以压注技艺覆设在该第三基板10c的该第一面11上。

45.其中,该第三基板10c、该第三电路层20c、该第三芯片30c及该第三绝缘层40c构成一第三层芯片封装1f,该第三层芯片封装1f相对于该第二层芯片封装1e为该上层芯片封装,而该第二层芯片封装1e则相对为该下层芯片封装如图3所示;其中该第三芯片30c能选

择通过该第三电路层20c经由每一该第二穿孔1c延伸至与该第二芯片30b电性连接,或选择通过该第三电路层20c经由每一该第二穿孔1c及每一该第一穿孔1a延伸至与该第一芯片30a电性连接,或选择通过该第三电路层20c经由每一该第二穿孔1c及每一该第一穿孔1a延伸至与该下部电路层50电性连接,以利于增加产品的多元化功能或芯片效能运算的加乘。

46.在图4中所示的实施例为本案的该多层堆叠式芯片封装1由两层封装结构所堆叠而成,并在该多层堆叠式芯片封装1外部增加芯片的实施例但不限制,其中在该多层堆叠式芯片封装1上进一步设有一上部基板90、一上部电路层100、一外部芯片120及一上部绝缘层110;其中该上部基板90设于该第二绝缘层40b上,该上部基板90具有一第一面91,在该上部基板90的该第一面91成型设有至少一上部盲孔92,其中在该上部基板90的每一该上部盲孔92与该第二基板10b之间更具有至少一上部穿孔1b,或在该上部基板90的每一该上部盲孔92与该第二基板10b的每一该第二盲孔14之间更具有每一该上部穿孔1b,参考图4,该多层堆叠式芯片封装1具有两个该上部穿孔1b但不限制;其中该上部电路层100设在该上部基板90的该第一面91上并能延伸设在每一该上部盲孔92的内壁面上;其中该外部芯片120电性连接地设在该上部电路层100上,且该外部芯片120通过该上部外护层80的至少一上部开口81与该上部电路层100电性连接,参考图4,该上部外护层80具有两个该上部开口81但不限制;其中该上部绝缘层110为以压注技艺覆设在该上部基板90的该第一面91上;其中该外部芯片120能选择通过该上部电路层100并经由每一该上部穿孔1b以延伸至与该第二芯片30b电性连接,或选择通过该上部电路层100并经由每一该上部穿孔1b及每一该第一穿孔1a以延伸至与该第一芯片30a电性连接,或选择通过该上部电路层100并经由每一该上部穿孔1b及每一该第一穿孔1a以延伸至与该下部电路层50电性连接,以利于增加产品的多元化功能或芯片效能运算的加乘。

47.本实用新型的该多层堆叠式芯片封装1与现有的芯片封装相较,具有以下优点:

48.本实用新型的该多层堆叠式芯片封装1,参考图1及图2,由该第一基板10a、该第一电路层20a、该第一芯片30a及该第一绝缘层40a构成的一第一层芯片封装1d(如图3所示)为一下层芯片封装但不限制;其中由该第二基板10b、该第二电路层20b、该第二芯片30b及该第二绝缘层40b构成的一第二层芯片封装1e(如图3所示)为一上层芯片封装但不限制;其中该上层芯片封装为堆叠地位于该下层芯片封装的上方,以此堆叠模式以形成该多层堆叠式芯片封装1,以使每一该芯片30之间能通过其中一该芯片30(如第二芯片30b)能对其他该芯片30(如第一芯片30a)进行指令操作,或通过各每一芯片30之间的运算功能叠加而能加乘增加总体运算的效能,有效地解决制造端芯片为了封装产品追求面积缩小化须不断开发运算能力更强的芯片而增加成本的问题,以利于芯片封装产品面积能缩小化且降低制造端成本。

49.以上所述仅为本实用新型的优选实施例,对本实用新型而言其仅是说明性的,而非限制性的;本领域普通技术人员理解,在本实用新型权利要求所限定的精神和范围内可对其进行许多改变,修改,甚至等效变更,但都将落入本实用新型的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1