半导体测试装置的制作方法

1.本实用新型涉及半导体技术领域,具体提供一种半导体测试装置。

背景技术:

2.在半导体的制造过程中有一个很重要的工序:半导体量产测试。通过半导体量产测试对芯片进行测试,从而检测芯片是否合格。

3.为了追求测试效率一般会采用在测试板上设置多个用于测试芯片的测试座(即多site同测),通过机械手可以对多个芯片进行同时测试,从而提高测试效率,减少测试时间,降低测试成本。

4.然而,现有多site同测方案中,在测试过程中,机械手会对芯片产生一定压力,芯片会将该压力传递至测试板上,由于是多个芯片同时测试,测试板上受到的压力也成倍增加,经过长时间的测试,测试板长期受到过大的压力容易导致安装芯片的区域出现凹陷、平整度变差,从而影响最终的测试结果。

技术实现要素:

5.本实用新型旨在解决上述技术问题,即,解决现有多site同测方案中测试板受到的压力过大,导致测试区域出现凹陷、平整度变差的问题。

6.为此目的,本实用新型提供一种半导体测试装置,该半导体测试装置包括:安装结构;测试板,所述测试板设置在所述安装结构上,所述测试板上具有用于安装多个芯片组件的安装区域;支撑结构,所述支撑结构设置在所述安装结构上,所述支撑结构具有凸出的支撑面,所述支撑面在所述安装区域内抵顶在所述测试板上,以便向所述测试板提供支撑力,所述支撑力的方向与所述芯片组件在测试时受到的压力方向相反。

7.进一步地,所述支撑结构包括:支撑板,所述支撑板与所述安装结构连接;支撑块,所述支撑块设置在所述支撑板上,所述支撑面位于所述支撑块上,所述支撑块通过所述支撑面抵顶在所述测试板上。

8.进一步地,所述支撑块为多个,多个所述支撑块间隔分布在所述支撑板上,所有所述支撑块均抵顶在所述测试板上。

9.进一步地,所述安装区域包括多个间隔分布的子安装区域,每个所述芯片组件安装在一个所述子安装区域内,所述支撑块的位置与所述子安装区域的位置一一对应设置。

10.进一步地,所述支撑结构包括:支撑条,所述支撑条设置在所述支撑板上,所述支撑条与所述支撑块共同抵顶在所述测试板上。

11.进一步地,所述芯片组件通过螺栓固定在所述测试板上,所述测试板上设置有与所述螺栓配合的第一安装孔;所述支撑条上设置有与所述第一安装孔相对应的第二安装孔,所述螺栓同时贯穿所述第一安装孔和第二安装孔。

12.进一步地,所述支撑条为多个,多个所述支撑条间隔分布;所述支撑块为多个,相邻的所述支撑条之间设置有至少一个所述支撑块。

13.进一步地,所述芯片组件通过螺栓固定在所述测试板上,所述测试板上设置有与所述螺栓配合的第一安装孔;所述支撑结构上设置有与所述第一安装孔相对应的第二安装孔,所述螺栓同时贯穿所述第一安装孔和第二安装孔。

14.进一步地,所述测试板具有相对设置的第一侧和第二侧,所述芯片组件安装在所述测试板的第一侧,所述支撑结构位于所述测试板的第二侧,所述支撑结构提供的支撑力自所述测试板的第二侧朝向所述测试板的第一侧。

15.进一步地,所述支撑结构为一体成型结构。

16.在采用上述技术方案的情况下,本实用新型的半导体测试装置通过在支撑结构上设置凸出的支撑面,可以通过支撑面抵顶在测试板的安装区域内,从而向测试板提供支撑力,该支撑力的方向与所述芯片组件在测试时受到的压力方向相反,因此,在机械手对芯片进行测试的过程中,支撑结构提供的支撑力可以抵消机械手产生的压力,从而避免测试板上出现凹陷变形,提高测试板的平整度,进而保证测试的准确性。

附图说明

17.下面结合附图来描述本实用新型的优选实施方式,附图中:

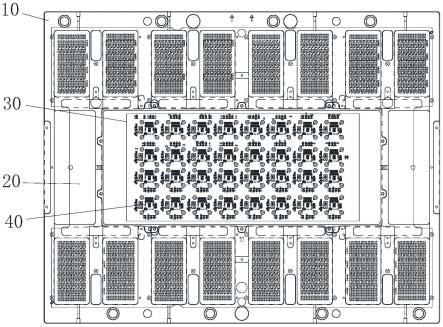

18.图1是本实用新型的实施例一的半导体测试装置的结构示意图;

19.图2是本实用新的实施例一的半导体测试装置的支撑结构的结构示意图;

20.图3是本实用新的实施例一的半导体测试装置的测试板的安装区域的示意图;

21.图4是图3中a的局部放大图;

22.图5是本实用新的实施例二的半导体测试装置的支撑结构的结构示意图;

23.图6是本实用新的实施例二的半导体测试装置的测试板的安装区域的示意图;

24.图7是图6中b的局部放大图;

25.图8是本实用新型的实施例一的半导体测试装置的爆炸图;

26.图例:

27.10、安装结构;20、测试板;21、第一安装孔;30、安装区域;31、子安装区域;40、支撑结构;41、支撑板;42、支撑块;421、支撑面;43、支撑条;431、第二安装孔;44、连接耳。

具体实施方式

28.下面结合实施例对本实用新型做进一步说明,但本实用新型的保护范围不局限于说明书的内容。

29.如图1所示,本实用新型的实施例一,提供一种半导体测试装置,该半导体测试装置包括安装结构10、测试板20和支撑结构40,测试板 20设置在安装结构10上,测试板20上具有用于安装多个芯片组件的安装区域30;支撑结构40设置在安装结构10上,支撑结构40具有凸出的支撑面421,支撑面421在安装区域30内抵顶在测试板20上,以便向测试板20提供支撑力,支撑力的方向与芯片组件在测试时受到的压力方向相反。也就是说,支撑结构40设置在安装结构10上,支撑面421抵顶在测试板20上,支撑面421的抵顶位置位于安装区域30内,支撑结构40用于向测试板20提供支撑力,支撑力的方向与芯片组件在测试时受到的压力方向相反。本实用新型的半导体测试装置通过在支撑结构40上设置凸出的支撑面421,可以通过支撑面421抵顶在测试板20的安装区域 30内,从而向测试板20提供支撑力,该支

撑力的方向与芯片组件在测试时受到的压力方向相反,因此,在机械手对芯片进行测试过程中,支撑结构40提供的支撑力可以抵消机械手产生的压力,从而避免测试板20 上出现凹陷变形,提高测试板20的平整度,进而保证测试的准确性。

30.需要说明的是,安装结构10是用来安装测试板20和支撑结构40的基础结构,在本实施例中,安装结构10为安装框,在图未示出的一些其他实施例中,安装结构10也可以是基座、支架等,只要可以起到安装测试板20和支撑结构40作用的结构均在本实用新型的保护范围之内。

31.在如图2所示的实施例一中,支撑结构40包括支撑板41和支撑块 42,支撑板41与安装结构10连接;支撑块42设置在支撑板41上,支撑块42抵顶在测试板20上。支撑板41的外周上形成有连接耳44,连接耳44上设置有螺孔,螺栓通过该螺孔将支撑板41固定在安装结构10上,支撑块42设置在支撑板41朝向测试板20的一侧,支撑块42具有相对设置的第一端面和第二端面,支撑块42的第一端面与支撑板41相连,支撑块42的第二端面为支撑面421,支撑块42通过支撑面421抵顶在支撑板41的第二侧上。支撑块42抵顶在测试板20上的位置为支撑结构40 的抵顶位置。通过设置支撑板41和支撑块42,可以通过支撑块42对支撑板41上的安装区域30提供支撑力,从而避免测试板20在芯片测试过程中受到压力而变形,避免芯片接触不良,提高芯片测试的准确率。

32.进一步地,如图2所示,支撑块42为多个,多个支撑块42间隔分布在支撑板41上,所有支撑块42均抵顶在测试板20上。通过将多个支撑块42间隔分布在支撑板41上,在将支撑结构40安装到安装结构10 上后,多个支撑块42可以同时支撑在测试板20上,使支撑力可以间隔分布在测试板20上,避免测试板20局部受力过大导致变形。

33.需要说明的是,在本实施例中,如图3和图4所示,安装区域30包括多个间隔分布的子安装区域31,每个芯片组件安装在一个子安装区域 31内,支撑块42的位置与子安装区域31的位置一一对应设置。通过将支撑块42的设置位置与子安装区域31的位置一一对应设置,使支撑块 42的抵顶位置正好是芯片组件的安装位置,由于在芯片测试过程中,机械手的压力是通过芯片传递至测试板20上的,也就是说,芯片组件的安装位置就是测试板20的受力位置,而通过将支撑块42的安装位置与芯片组件的位置一一对应,从而可以使支撑块42正好支撑在测试板20的受力位置上,从而将压力抵消,避免测试板20变形、凹陷。

34.机械手最多支撑同测32site,也就是说,可以最多支持32个芯片同时测试,因此,如图3所示的实施例一中,测试板20上最多可以设置32 个子安装区域31,每个子安装区域31内对应安装一个芯片组件,实现 32个芯片同时测试。而采用这种测试方案,测试板20在测试过程中受到的压力也会非常的大,更容易变形,因此,为了避免测试板20在测试过程中发生变形,需要在支撑板41上对应设置32个支撑块42,而且每个支撑块42均与芯片组件的安装位置相对应,这样可以将机械手在测试时施加的压力一一抵消,从而有效避免测试板20的变形,使机械手的使用率最大,进而大大提高检测效率。

35.如图5所示的实施例二,同样公开了一种半导体测试装置,其结构与实施例一基本相同,区别在于,支撑结构40还包括支撑条43,支撑条 43设置在支撑板41上,支撑条43与支撑块42共同抵顶在测试板20上。支撑条43相较于支撑块42来说,支撑面421更大,较大的支撑面421 贴合在测试板20上,可以对测试板20施加更加均匀的支撑力,从而避免测试板20局部变形。

36.在本实施例中,芯片组件通过螺栓固定在测试板20上,测试板20 上设置有与螺栓配合的第一安装孔21;如图5所示,支撑条43上设置有与第一安装孔21相对应的第二安装孔431,螺栓同时贯穿第一安装孔21 和第二安装孔431。具体来说,芯片组件包括芯片和芯片座,芯片插设在芯片座上,芯片座上设置有第三安装孔,装配时,将芯片座的第三安装孔与第一安装孔21、第二安装孔431对齐,将螺栓同时穿过第三安装孔、第一安装孔21和第二安装孔431,再通过螺母固定,从而将芯片座、测试板20和支撑结构40固定在一起。由于第二安装孔431设置在支撑条43上,因此,测试板20的表面紧紧贴合在支撑条43的支撑面421上,可以有效避免测试板20的弯曲、变形或凹陷;另外,由于测试板20位于芯片座与支撑条43之间,螺母是与支撑条43直接接触,并不会与测试板20直接接触,因此,螺母施加的预紧力不会直接作用在测试板20 上,而是通过支撑条43施加到测试板20上,相当于支撑条43起到了垫片的作用,可以有效防止螺母预紧力过大对测试板20造成损坏,属于典型的一物多用。

37.如图6和图7所示的实施例二中,在采用32site同测方案时,子安装区域31呈矩阵式分布,总共8列,每列4个子安装区域31。为了实现可靠的支撑,可以设置多个间隔分布的支撑条43,相应的,支撑块42也设置有多个,相邻的支撑条43之间设置有至少一个支撑块42。具体到本实施例中,支撑条43为9个,支撑块42为32个,相邻的两个支撑条43 之间形成间隔空间,每个间隔空间内又间隔设置有4个支撑块42,4个支撑块42与测试板20上的子安装区域31一一对应。在芯片组件装配时,每个芯片组件均安装在一个子安装区域31内,并与支撑块42一一对应,芯片组件分别连接在支撑块42两侧的支撑条43上,实现固定。采用这种支撑结构40,可以在将芯片组件固定的同时,通过支撑块42进行精准地支撑,从而抵消芯片测试过程中的压力,避免测试芯片变形,在保证芯片测试准确度的前提下,提高芯片的测试效率。

38.在图未示出的实施例三中,还公开了一种半导体测试装置,其结构与实施例一基本相同,区别在于,支撑结构40为一体成型结构,其中,支撑块42、支撑条43均一体成型在支撑板41上,使三者形成一个整体结构,使支撑结构40整体强度更高,可靠性更好。进一步地,支撑条43 可以设计成加强筋结构,采用这种方式,支撑条43不仅具有支撑、连接和垫片的作用,还可以作为加强筋,起到提高支撑结构40的强度的作用,属于典型的一物多用。

39.在图未示出的实施例四中,还公开了一种半导体测试装置,其结构与实施例一基本相同,区别在于,芯片组件通过螺栓固定在测试板20上,测试板20上设置有与螺栓配合的第一安装孔21;支撑块42上设置有与第一安装孔21相对应的第二安装孔431,螺栓同时贯穿第一安装孔21和第二安装孔431。具体来说,芯片组件包括芯片和芯片座,芯片插设在芯片座上,芯片座上设置有第三安装孔,装配时,将芯片座的第三安装孔与第一安装孔21、第二安装孔431对齐,将螺栓同时穿过第三安装孔、第一安装孔21和第二安装孔431,再通过螺母固定,从而将芯片座、测试板20和支撑块42紧紧固定在一起,测试板20的表面紧紧贴合在支撑块42的支撑面421上,芯片座的位置全部由支撑块42支撑,可以有效避免测试板20的弯曲、变形或凹陷;另外,由于测试板20位于芯片座与支撑块42之间,螺母是与支撑块42直接接触,并不会与测试板20直接接触,因此,螺母施加的预紧力不会直接作用在测试板20上,而是通过支撑块42施加到测试板20上,相当于支撑块42起到了垫片的作用,可以有效防止螺母预紧力过大对测试板20造成损坏,属于典型的一物多用。

40.需要说明的是,如图8所示的实施例一中,测试板20具有相对设置的第一侧和第二

侧,芯片组件安装在测试板20的第一侧,支撑结构40 位于测试板20的第二侧,支撑结构40提供的支撑力自测试板20的第二侧朝向测试板20的第一侧;可以理解的是,安装结构10位于测试板20 与支撑结构40之间,测试板20和支撑结构40分别通过螺栓固定在安装结构10上,在测试过程中,测试板20受到压力后,可以通过支撑结构 40提供的支撑力将压力抵消,从而避免测试板20凹陷、变形。

41.至此,已经结合附图所示的优选实施方式描述了本实用新型的技术方案,但是,本领域技术人员容易理解的是,本实用新型的保护范围显然不局限于这些具体实施方式。在不偏离本实用新型的原理的前提下,本领域技术人员可以对相关技术特征作出等同的更改或替换,这些更改或替换之后的技术方案都将落入本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1