芯片和终端的制作方法

1.本技术涉及半导体技术领域,尤其涉及一种芯片和终端。

背景技术:

2.晶振与裸芯(die)构成的电路,可以实现时钟的高稳定输出,其每秒时钟偏差小于百万分之20(20ppm)以内,且因其可以采用纽扣电池等供电,无需依赖设备主体上电或下电,广泛应用于工业通信设备、室内终端设备、室外终端设备等。

3.然而,如果封装晶振的工艺控制不当,可能出现封装空洞、封装分层、封装内形变等严重问题,因此,对封装晶振的制程管控技术提出了挑战。

技术实现要素:

4.本技术提供一种芯片和终端,通过解决封装空洞、封装分层、封装内形变问题,可以提高芯片的导电性能以及可靠性。

5.第一方面,本技术提供一种芯片,该芯片包括承载基板、多个第一焊盘、多个焊锡层、晶振、以及底部填充胶。多个第一焊盘、多个焊锡层、以及晶振依次层叠设置于承载基板上,多个第一焊盘之间间隔设置,多个焊锡层之间间隔设置;底部填充胶填充于晶振与承载基板之间。

6.本技术中,由于承载基板与晶振之间的间距较小,约为30μm。而底部填充胶的粒径也非常小,底部填充胶的粒径小于塑封体的粒径,因此,相较于在承载基板与晶振之间填充塑封体,底部填充胶可以更加充分地流入承载基板与第一焊盘的连接处、以及焊锡层与晶振的连接处,进而在晶振与承载基板之间充分填充,避免出现封装分层和封装空洞的问题。在此基础上,由于底部填充胶具有较好的热变形性能和玻璃化转变性能,而塑封体的热变形性能和玻璃化转变性能与焊锡层的材料特性、晶振的材料特性具有较大差异,因此,相较于塑封体,底部填充胶能够更好地承受机械应力,有效缓冲晶振和承载基板受到的机械应力,并防止晶振发生形变。例如,底部填充胶的材料的粒径小于或等于30μm,这样一来,即可在承载基板与晶振之间充分填充底部填充胶。本技术通过解决封装空洞、封装分层、封装内形变问题,可以提高芯片的导电性能以及可靠性。

7.在一些可能实现的方式中,环氧树脂不但可以以液态流入承载基板与晶振之间,其粒径还小于30μm,因此,底部填充胶的材料包括环氧树脂。在此基础上,根据设计需求,底部填充胶还可以包括催化剂、固化剂等材料。

8.在一些可能实现的方式中,晶振朝向承载基板一侧还设置有两个第二焊盘,两个第二焊盘均呈条状,且间隔设置。多个第一焊盘和多个焊锡层在承载基板上的正投影,与两个第二焊盘在承载基板上的正投影重叠。这样一来,利用第一焊盘与第二焊盘之间的焊锡层将晶振固定在承载基板上。

9.在一些可能实现的方式中,多个第一焊盘和多个焊锡层的数量均为n个;其中,n为大于或等于4的正整数。

10.相关技术中,为了确保利用第一焊盘与第二焊盘之间的焊锡层将晶振固定在承载基板上,第一焊盘的数量也为两个,两个第一焊盘均呈条状并间隔设置,以使得第一焊盘和第二焊盘对合后具有重叠区域。

11.然而,在两个呈条状的第一焊盘上形成的焊锡层可能因面积过大,导致焊锡层中锡的分布不均匀,从而在焊锡层中出现空洞现象。基于此,第一焊盘和焊锡层的数量可以均为n个,n为大于或等于4的正整数。并且,由于本技术实施例未改变第二焊盘的设置位置和尺寸,因此,本技术的每个第一焊盘和焊锡层在承载基板上的正投影的尺寸,均可以小于相关技术中第一焊盘和焊锡层在承载基板上的正投影的尺寸。例如,相关技术中第一焊盘和焊锡层在承载基板上的正投影的尺寸,等于第二焊盘在承载基板上的正投影的尺寸,则本技术的第一焊盘和焊锡层在承载基板上的正投影的尺寸,可以小于第二焊盘在承载基板上的正投影的尺寸。

12.在一些可能实现的方式中,晶振在承载基板上的正投影的形状为矩形,晶振包括相对设置的第一边沿和第二边沿、以及相对设置的第三边沿和第四边沿。两个第二焊盘从第一边沿延伸至第二边沿,且其中一个第二焊盘的边沿与第三边沿齐平,另一个第二焊盘的边沿与第四边沿齐平;多个第一焊盘在承载基板上的正投影,至少与晶振的四个角在承载基板上的正投影重叠。这样一来,既可以改善焊锡层中的锡分布不均匀的问题,还可以确保晶振通过第一焊盘、焊锡层、以及第二焊盘固定在承载基板上。

13.在该情况下,第一焊盘的数量可以为四个,该矩形的长可以为2mm,矩形的宽可以为1.2mm。多个第一焊盘中每一第一焊盘的长和宽的范围为0.3mm~0.5mm,多个第一焊盘中相邻第一焊盘之间的间距范围为0.2mm~1.4mm。当然,晶振在承载基板上的正投影的尺寸还可以是其他,第一焊盘在承载基板上的正投影的尺寸以及相邻第一焊盘之间的间隔,可以随着晶振在承载基板上的正投影的尺寸变化,本技术实施例对此不作限定。

14.在一些可能实现的方式中,芯片还包括裸芯片和塑封体,裸芯片包括集成电路,晶振与集成电路电连接,以为其他集成电路提供信号,并利用同一塑封体进行一体化封装。

15.第二方面,本技术提供一种终端,包括电路板和第一方面所述的芯片,该芯片设置于电路板上。

16.第二方面的实现方式与第一方面任意一种实现方式相对应。第二方面的实现方式所对应的技术效果可参见上述以及第一方面的任意一种实现方式所对应的技术效果,此处不再赘述。

附图说明

17.图1a为相关技术提供的一种晶振的封装结构图;

18.图1b为相关技术提供的另一种晶振的封装结构图;

19.图1c为相关技术提供的又一种晶振的封装结构图;

20.图2a为本技术实施例提供的芯片的俯视图;

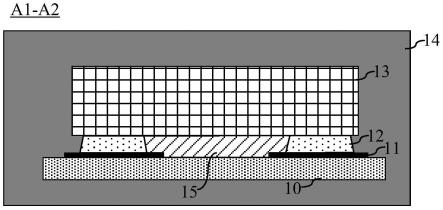

21.图2b为图2a中a1-a2向的剖视图;

22.图3a为本技术实施例提供的芯片的封装过程图;

23.图3b为本技术实施例提供的芯片的封装过程图;

24.图3c为本技术实施例提供的芯片的封装过程图;

25.图3d为本技术实施例提供的芯片的封装过程图;

26.图4为本技术实施例提供的晶振与第二焊盘的位置关系图;

27.图5a为本技术实施例提供的第一焊盘与第二焊盘的位置关系图;

28.图5b为本技术实施例提供的第一焊盘与第二焊盘的位置关系图。

29.附图标记:

30.10-承载基板;11-第一焊盘;12-焊锡层;13-晶振;14-塑封体;15-底部填充胶;16-第二焊盘;20-裸芯片。

具体实施方式

31.为使本技术的目的、技术方案和优点更加清楚,下面将结合本技术中的附图,对本技术中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

32.本技术的说明书实施例和权利要求书及附图中的术语“第一”、“第二”等仅用于区分描述的目的,而不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。“和/或”,用于描述关联对象的关联关系,表示可以存在三种关系,例如,“a和/或b”可以表示:只存在a,只存在b以及同时存在a和b三种情况,其中a,b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。“安装”、“连接”、“相连”等应做广义理解,例如可以是固定连接,也可以是可拆卸连接,或者一体地连接;可以是直接连接,也可以是通过中间媒介间接,也可以是两个元件内部的连通。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元。方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。“上”、“下”、“左”、“右”等仅用于相对于附图中的部件的方位而言的,这些方向性术语是相对的概念,它们用于相对于的描述和澄清,其可以根据附图中的部件所放置的方位的变化而相应地发生变化。

33.本技术实施例提供一种终端,该终端可以是手机、电脑、平板电脑、个人数字助理(personal digital assistant,简称pda)、智能穿戴式设备、智能家居设备等包含时钟电路的电子设备,本技术实施例对此不作限定。为了方便说明,下文以终端为手机进行举例说明。

34.在手机中,利用时钟电路可以实现时、分、秒的管理,定时,计时等功能。随着手机的日益普及,手机的功能也越来越多,多数消费者可以应用到手机的闹钟功能。手机的闹钟功能可以通过实时时钟(real_time clock,rtc)芯片与手机中的其他器件协同实现。

35.例如,用户设置特定时间作为闹钟提醒后,手机的操作系统可以向rtc芯片的寄存器写入上述闹钟的时间信息,当达到特定时间时,rtc芯片触发中断时间,实现闹钟。rtc芯片作为一个独立的模块,可以由纽扣电池独立供电,因此,即使手机关机,也可以到达特定时间后,闹钟也可以正常提醒。当然,还可以采用其他芯片实现闹钟功能,本技术实施例对此不作限定。

36.晶振可以提供较稳定的脉冲,因此,其广泛应用于芯片的时钟电路里。为了防止水汽、氧气接触到晶振,通常需要对晶振进行封装。

37.然而,相关技术中,如果封装晶振的工艺控制不当,可能出现封装空洞、封装分层、封装内形变等问题。

38.具体的,如图1a-图1c所示,承载基板10上依次层叠设置有第一焊盘11、焊锡层12、以及晶振13,并利用塑封体14对第一焊盘11、焊锡层12、以及晶振13进行整体封装。

39.如图1a所示,在第一焊盘11上焊接形成焊锡层12时,因锡的延展性不好,导致焊锡层12的焊接不好,在焊锡层12内可能出现空洞,即,封装空洞问题。

40.请继续参考图1a,形成晶振13后,利用塑封体14对第一焊盘11、焊锡层12、以及晶振13进行整体封装时,由于承载基板13与晶振13之间的间隔距离约为30μm,也可以说,沿承载基板10指向晶振的方向,第一焊盘11和焊锡层12的总厚度约为30μm,而现有的用于封装的塑封体13的粒径约为50μm,因此塑封体14无法充分填充晶振13与承载基板之间的区域,尤其是第一焊盘11、焊锡层12与承载基板11和晶振13的连接处,塑封体14更加难以填充,从而出现第一焊盘和焊锡层12与塑封体14分层的问题,即,封装分层。

41.此处需要说明的是,塑封体14的粒径即为塑封体14的颗粒直径。

42.如图1b和图1c所示,因机械应力,一方面,可能出现时钟偏差的问题;另一方面,机械应力使晶振13沿晶振13指向承载基板10的方向倾斜,或者,机械应力使得晶振13发生形变,承载基板10沿承载基板10指向晶振13的方向倾斜,导致晶振13到承载基板10距离更近一侧的焊锡层12的厚度较小,从而出现导电不良,可靠性变差的问题。

43.基于此,本技术实施例提供一种芯片,如图2a和图2b所示,该芯片包括承载基板10、多个第一焊盘11、多个焊锡层12、晶振13、以及底部填充胶(underfill)15。多个第一焊盘、多个焊锡层、以及晶振依次层叠设置于承载基板上,多个第一焊盘之间间隔设置,多个焊锡层之间间隔设置。底部填充胶填充于晶振与承载基板之间。

44.在此基础上,芯片还可以包括塑封体14,塑封体14可以对承载基板10、第一焊盘11、焊锡层12、晶振13、以及底部填充胶15进行封装。

45.在一些可能实现的方式中,本领域的技术人员应该知道,焊锡层12与第一焊盘11一一对应,每一焊锡层12在承载基板10上的正投影,均与一个第一焊盘11在承载基板10上的正投影重叠,焊锡层12在承载基板10上的正投影的尺寸,可以小于或等于与其对应的第一焊盘11在承载基板10上的正投影的尺寸。因此,在多个第一焊盘11之间间隔设置的情况下,多个焊锡层12之间也间隔设置。此处需要说明的是,在承载基板10上的正投影是指垂直投射至承载基板10上的投影。

46.如图2a所示,由于设置在承载基板10上的多个第一焊盘11之间间隔设置,多个焊锡层12之间间隔设置,因此,在晶振13所在的区域,未设置第一焊盘11和焊锡层12处,晶振13与承载基板10之间具有间距。本技术可以将底部填充胶15填充于晶振13与承载基板10之间的间距处。

47.具体的,在承载基板10上形成晶振13,并利用塑封体14对晶振13进行封装的工艺包括如下步骤:如图3a所示,在承载基板10上形成第一焊盘11,第一焊盘11的设置位置与晶振13朝向承载基板10侧的第二焊盘16(图4)的设置位置有关,第一焊盘11和第二焊盘1 6对合后具有重叠区域,以确保利用第一焊盘11与第二焊盘16之间的焊锡层12,将晶振13固定在承载基板10上。接着,如图3b所示,在第一焊盘11背离承载基板10侧形成焊锡层12,此时焊锡层12的锡可以处于熔融状态。接着,如图3c所示,在熔融状态的焊锡层12背离承载基板

10侧形成晶振13,并对熔融状态的焊锡层12进行固化,以得到固态的焊锡层12。之后,如图3d所示,从相邻第一焊盘11之间的间隔处,向晶振13与承载基板10之间填充液态的底部填充胶15,待液态的底部填充胶15充分填充晶振13与承载基板10之间的间隔处后,对液态的底部填充胶15进行固化,以得到固态的底部填充胶15。接着,如图2a所示,利用塑封体14对晶振13进行封装。

48.此处需要说明的是,为了避免出现封装分层的问题,应充分在晶振13与承载基板10之间的间隔处填充底部填充胶15,此情况下,待晶振13与承载基板10之间填满底部填充胶15后,部分底部填充胶15流至任一第一焊盘11背离与其相邻的第一焊盘11一侧。经固化后,保留下来的底部填充胶15不但可以位于承载基板10与晶振13之间的间隔处,还可以位于任一第一焊盘11背离与其相邻的第一焊盘11一侧。

49.本技术中,由于承载基板10与晶振13之间的间距较小,约为30μm。而底部填充胶15的粒径也非常小,底部填充胶15的粒径小于塑封体14的粒径,因此,相较于在承载基板10与晶振13之间填充塑封体14,底部填充胶15可以更加充分地流入承载基板10与第一焊盘11的连接处、以及焊锡层12与晶振13的连接处,进而在晶振13与承载基板10之间充分填充,避免出现封装分层和封装空洞的问题。在此基础上,由于底部填充胶15具有较好的热变形性能和玻璃化转变性能,而塑封体14的热变形性能和玻璃化转变性能与焊锡层12的材料特性、晶振13的材料特性具有较大差异,因此,相较于塑封体14,底部填充胶15能够更好地承受机械应力,有效缓冲晶振13和承载基板10受到的机械应力,并防止晶振13发生形变。本技术实施例通过解决封装空洞、封装分层、封装内形变问题,可以提高芯片的导电性能以及可靠性。

50.在一些可能实现的方式中,本技术实施例不对底部填充胶15的具体材料进行限定,只要底部填充胶15可以以液态流入承载基板10与晶振13之间,且底部填充胶15的粒径小于或等于30μm即可。这样一来,即可在承载基板10与晶振13之间充分填充底部填充胶15。

51.可选的,环氧树脂不但可以以液态流入承载基板10与晶振13之间,其粒径还小于30μm,因此,底部填充胶15的材料包括环氧树脂。在此基础上,根据设计需求,底部填充胶15还可以包括催化剂、固化剂等材料。

52.在一些实施例中,前文提到,第一焊盘11的设置位置与第二焊盘16的设置位置有关。如图4所示,第二焊盘16的数量通常为二个,两个第二焊盘16均呈条状并间隔设置。相关技术中,为了利用第一焊盘11与第二焊盘16之间的焊锡层12将晶振13固定在承载基板10上,第一焊盘11的数量也为两个,两个第一焊盘11均呈条状并间隔设置,以使得第一焊盘11和第二焊盘1 6对合后具有重叠区域。

53.然而,在两个呈条状的第一焊盘11上形成的焊锡层12可能因面积过大,导致焊锡层12中锡的分布不均匀,从而在焊锡层12中出现空洞现象。基于此,第一焊盘11和焊锡层12的数量可以均为n个,n为大于或等于4的正整数。并且,由于本技术实施例未改变第二焊盘12的设置位置和尺寸,因此,本技术实施例的每个第一焊盘11和焊锡层12在承载基板10上的正投影的尺寸,均可以小于相关技术中第一焊盘11和焊锡层12在承载基板10上的正投影的尺寸。例如,相关技术中第一焊盘11和焊锡层12在承载基板10上的正投影的尺寸,等于第二焊盘16在承载基板10上的正投影的尺寸,则本技术实施例的第一焊盘11和焊锡层12在承载基板10上的正投影的尺寸,可以小于第二焊盘16在承载基板10上的正投影的尺寸。

54.这样一来,可以在不改变第二焊盘12的设置位置和尺寸的情况下,改善因焊锡层12在承载基板10上的正投影的尺寸过大,导致焊锡层12中的锡分布不均匀的问题,从而进一步解决封装空洞问题。

55.在一些可能实现的方式中,本技术实施例不对第一焊盘11和焊锡层12的具体设置位置、数量、以及形状进行限定,只要第一焊盘11和焊锡层12在承载基板10上的正投影,与第二焊盘16在承载基板10上的正投影具有重叠区域即可。

56.示例的,如图5a和图5b所示,第一焊盘11和焊锡层12在承载基板10上的正投影的形状可以为圆形、矩形等。当然,第一焊盘11和焊锡层12的形状也可以是其他,本技术实施例对此不作限定。

57.示例的,如图5a所示,第一焊盘11和焊锡层12的数量可以为四个;或者,如图5b所示,第一焊盘11和焊锡层12的数量可以为六个。

58.示例的,如图4所示,晶振13包括相对设置的第一边沿和第二边沿、以及相对设置的第三边沿和第四边沿,两个第二焊盘16从第一边沿延伸至第二边沿,且其中一个第二焊盘的边沿与第三边沿齐平,另一个第二焊盘16的边沿与第四边沿齐平。如图5a所示,第一焊盘11在承载基板10上的正投影的形状为矩形,多个第一焊盘11在承载基板10上的正投影,至少与晶振13的四个角在承载基板10上的正投影重叠。也可以说,第一个第一焊盘11的边沿与第一个第二焊盘16的一个短边齐平,第二个第一焊盘11的边沿与第一个第二焊盘16的另一个短边齐平,且第一个第一焊盘11和第二个第一焊盘11的边沿还与第一个第二焊盘的长边齐平;第三个第一焊盘11的边沿与第二个第二焊盘16的一个短边齐平,第四个第一焊盘11的边沿与第二个第二焊盘16的另一个短边齐平,且第三个第一焊盘11和第四个第一焊盘11的边沿还与第二个第二焊盘的长边齐平。这样一来,既可以改善焊锡层12中的锡分布不均匀的问题,还可以确保晶振13通过第一焊盘11、焊锡层12、以及第二焊盘16固定在承载基板10上。

59.或者,如图5b所示,第一焊盘11在承载基板10上的正投影的形状为圆形,每三个第一焊盘11在承载基板10上的正投影与一个第二焊盘16在承载基板10上的正投影重合。

60.需要说明的是,图5a和图5b为示意性的示出第一焊盘11、焊锡层12、以及第二焊盘16的位置关系图,本领域的技术人员应该理解的是,在将晶振13固定在承载基板10上后,第二焊盘16应始终焊接在晶振13上。

61.在一些可能实现的方式中,本技术实施例不对第一焊盘11和焊锡层12在承载基板10上的正投影的具体尺寸进行限定,第一焊盘11和焊锡层12在承载基板10上的正投影的尺寸,与第二焊盘16在承载基板10上的正投影的尺寸有关。而第二焊盘16在承载基板10上的正投影的尺寸,与晶振13在承载基板10上的正投影的尺寸有关。因此,本技术实施例可以根据晶振13的实际尺寸,调节第一焊盘11和焊锡层12在承载基板10上的正投影的尺寸。

62.示例的,晶振13在承载基板10上的正投影为矩形,该矩形的尺寸为2mm*1.2mm。以图5a所示的第一焊盘11形状及设置位置为例,每个第一焊盘11在承载基板10上的正投影的长和宽的范围可以为0.3mm~0.5mm,相邻第一焊盘11之间的间距范围可以为0.2mm~1.4mm。例如,第一焊盘11在承载基板10上的正投影的长和宽为0.3mm*0.3mm,相邻第一焊盘11之间的间距可以分别为0.6mm和1.4mm。当然,晶振13在承载基板10上的正投影的尺寸还可以是其他,第一焊盘11在承载基板10上的正投影的尺寸以及相邻第一焊盘11之间的间

隔,可以随着晶振13在承载基板10上的正投影的尺寸变化,本技术实施例对此不作限定。

63.在一些实施例中,如图2a所示,考虑晶振13通常与其他集成电路电连接,以为其他集成电路提供信号,其他集成电路可以集成在裸芯片(die)20上,因此,可以将晶振13与集成有集成电路的裸芯片20集成在同一芯片上,并利用同一塑封体14进行一体化封装。并且,包含晶振13和裸芯片20的芯片可以设置在终端的电路板上。

64.此处需要说明的是,图2a为示意性的示出了晶振13与裸芯片20的相对位置,本领域的技术人员应该知道,裸芯片20不但可以与晶振13错开设置在承载基板10上,裸芯片20还可以设置在晶振13朝向承载基板10一侧,或者裸芯片20还可以设置在晶振13背离承载基板10一侧,只要晶振13与裸芯片20通过同一塑封体14一体化封装即可。

65.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1