一种提高电流能力的碳化硅MOSFET的制作方法

一种提高电流能力的碳化硅mosfet

技术领域

1.本实用新型涉及一种提高电流能力的碳化硅mosfet。

背景技术:

2.sic器件碳化硅(sic)材料因其优越的物理特性,广泛受到人们的关注和研究。其高温大功率电子器件具备输入阻抗高、开关速度快、工作频率高、耐高温高压等优点,在开关稳压电源、高频加热、汽车电子以及功率放大器等方面取得了广泛应用。

3.在面临更高耐压的情况下,超结作为将纵向耐压转化为横向耐压的一种技术手段,可以将普通纵向sic器件的耐压特性进一步提高,适用于特高压输电等高压领域。导通电阻的降低是功率mosfet永恒不变的追求,每一种降低导通电阻的方法都应该被重视;如何在维持器件耐压特性的基础上降低器件的导通电阻成了器件设计的重要发展方向。

技术实现要素:

4.本实用新型要解决的技术问题,在于提供一种提高电流能力的碳化硅mosfet,利用了器件纵向的空间构建两路电流通路,来提高器件的电流密度,降低导通电阻。

5.本实用新型是这样实现的:一种提高电流能力的碳化硅mosfet,包括:

6.碳化硅衬底,

7.漂移层,所述漂移层设于所述碳化硅衬底的上侧面;所述漂移层上设有倒凸字形的沟槽;所述沟槽内设有一n+低阻导电区以及p型夹断区,所述p型夹断区为倒凹字形,所述n+低阻导电区设于所述漂移层以及p型夹断区内,所述n+低阻导电区底部连接至所述碳化硅衬底;

8.p+夹断区,所述p+夹断区设于所述漂移层上,且与所述p型夹断区连接;

9.n+源区,所述n+源区分别连接所述p+夹断区以及所述p型夹断区;

10.源极金属层,所述源极金属层分别连接所述p型夹断区、p+夹断区以及所述n+源区;

11.栅极绝缘层,所述栅极绝缘层连接至所述p型夹断区;

12.栅极金属层,所述栅极金属层连接至所述栅极绝缘层;

13.以及,漏极金属层,所述漏极金属层连接至碳化硅衬底的下侧面。

14.进一步地,所述p+夹断区设有第一源区卡槽,所述p型夹断区设有第二源区卡槽,所述n+源区设于所述第一源区卡槽以及第二源区卡槽内。

15.进一步地,所述漂移层为n-型。

16.本实用新型的优点在于:

17.一、在器件纵向结构中有低阻的导电通道;

18.二、器件的低阻导电通道和横向的p型夹断区形成横向pn结,将纵向的耐压特性转变为横向;

19.三、器件仍然维持了纵向的p+和n-构成的pn结耐压特性;并且器件耐压特性极高,

克服了纵向耐压结构耐压极限,同时在纵向导电通路中有纵向的高掺低阻路径,可以有效降低导通电阻。

附图说明

20.下面参照附图结合实施例对本实用新型作进一步的说明。

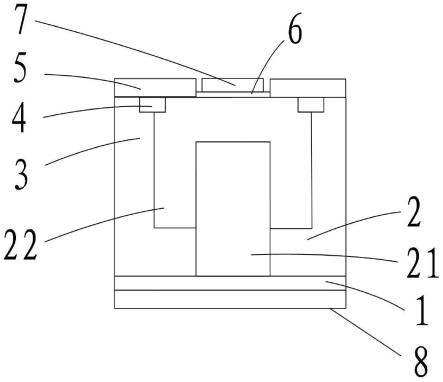

21.图1是本实用新型一种提高电流能力的碳化硅mosfet的原理示意图。

22.图2是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图一。

23.图3是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图二。

24.图4是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图三。

25.图5是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图四。

26.图6是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图五。

27.图7是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图六。

28.图8是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图七。

29.图9是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图八。

30.图10是本实用新型一种提高电流能力的碳化硅mosfet的制造方法流程图九。

具体实施方式

31.如图1所示,本实用新型一种提高电流能力的碳化硅mosfet,包括:

32.碳化硅衬底1,

33.漂移层2,所述漂移层2设于所述碳化硅衬底的上侧面;所述漂移层上设有倒凸字形的沟槽;所述沟槽内设有一n+低阻导电区21以及p型夹断区22,所述p型夹断区22为倒凹字形,所述n+低阻导电区21设于所述漂移层2以及p型夹断区22内,所述n+低阻导电区21底部连接至所述碳化硅衬底1,所述漂移层2为n-型;

34.p+夹断区3,所述p+夹断区3设于所述漂移层2上,且与所述p型夹断区22连接;

35.n+源区4,所述n+源区4分别连接所述p+夹断区3以及所述p型夹断区22;

36.源极金属层5,所述源极金属层5分别连接所述p型夹断区22、p+夹断区3以及所述n+源区4;

37.栅极绝缘层6,所述栅极绝缘层6连接至所述p型夹断区22;

38.栅极金属层7,所述栅极金属层7连接至所述栅极绝缘层6;

39.以及,漏极金属层8,所述漏极金属层8连接至碳化硅衬底1的下侧面。

40.所述p+夹断区3设有第一源区卡槽,所述p型夹断区22设有第二源区卡槽,所述n+源区4设于所述第一源区卡槽以及第二源区卡槽内。

41.在器件的栅极金属层7下方构建了n+低阻导电区21,该n+低阻导电区21从栅极绝缘层6下方一直接触到碳化硅衬底1;在源极金属层5下方,n+源区4左侧有p+夹断区3用来与n-型漂移层2形成纵向pn结,在源极金属层5下方,n+源区4右侧有p型夹断区22用来与n+低阻导电区21形成横向pn结,其n+源区4是n型重掺杂,实现n+源区4和源极金属层5的欧姆接触,其构成了纵向的n+低阻导电区21,可以形成低阻导电沟道,从而降低导通电阻。通过将纵向的pn结耐压特性转化为横向的pn结,使得在n+低阻导电区的耐压特性不会衰减,可以突破纵向厚度对于器件耐压特性的影响,同时构建低阻通道,实现耐压和低导通电阻兼得。

42.如图1至10所示,上述的碳化硅mosfet的制造方法,(mosfet为metal-oxide-semiconductor field-effect-transistor,金属-氧化物-半导体场效应晶体管)包括:

43.步骤1、在具有漂移层2的碳化硅衬底1上形成阻挡层9,并对阻挡层9蚀刻形成通孔,通过通孔对漂移层2进行离子注入,形成n+低阻导电区21,所述漂移层2为n-型;

44.步骤2、重新形成阻挡层9,并对阻挡层蚀刻形成通孔,通过通孔对漂移层2进行离子注入,形成p型夹断区22;

45.步骤3、重新形成阻挡层9,并对阻挡层9蚀刻形成通孔,通过通孔对n+低阻导电区21进行离子注入,形成中间的p型夹断区22;

46.步骤4、重新形成阻挡层9,并对阻挡层9蚀刻形成通孔,通过通孔对漂移层2进行离子注入,形成p+夹断区3;

47.步骤5、重新形成阻挡层9,并对阻挡层9蚀刻形成通孔,通过通孔对进行离子注入,形成n+源区4;

48.步骤6、重新形成阻挡层9,并对阻挡层9蚀刻形成通孔,通过通孔氧化形成栅极绝缘层6;

49.步骤7、重新形成阻挡层9,并对阻挡层9蚀刻形成通孔,通过通孔淀积金属形成源极金属层5;

50.步骤8、重新形成阻挡层9,并对阻挡层9蚀刻形成栅极金属淀积区,淀积形成栅极金属层7;

51.步骤9、去除所有阻挡层9,并在碳化硅衬底上淀积漏极金属层8。

52.虽然以上描述了本实用新型的具体实施方式,但是熟悉本技术领域的技术人员应当理解,我们所描述的具体的实施例只是说明性的,而不是用于对本实用新型的范围的限定,熟悉本领域的技术人员在依照本实用新型的精神所作的等效的修饰以及变化,都应当涵盖在本实用新型的权利要求所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1