芯片封装结构的制作方法

1.本实用新型是一种芯片封装结构,尤指一种具电磁干扰屏蔽层的芯片封装结构。

背景技术:

2.半导体产业所生产的芯片产品普遍应用于人们的日常生活之中,如计算机、手机、汽车或医疗等,为人们带来便利的生活,然而,生活环境中所存在电磁波会对现有的芯片产品产生电磁干扰(emi,electromagneticinterference)而影响到产品内部的芯片或内部线路,使得产品产生故障或表现下降,进而造成产品的市场竞争力下降,尤其5g技术或未来6g技术都会陆续应用于各个电子产品上,各个电子产品免不了要使用芯片产品,若应用在汽车或医疗领域上更会有人身安全的问题考虑。

3.因此,一种有效地解决电磁波会对现有的芯片产品产生电磁干扰而影响到产品内部的芯片或内部线路问题的具电磁干扰屏蔽层的芯片封装结构及其制造方法,为目前相关产业的迫切期待。

技术实现要素:

4.本实用新型的主要目的在于提供一种具电磁干扰屏蔽层的芯片封装结构,其中该芯片封装结构包含一基板、至少一第一电路层、至少一第二电路层、至少一芯片、一第一绝缘层及至少一电磁干扰屏蔽层;其中该至少一电磁干扰屏蔽层是由金属材料所构成,该至少一电磁干扰屏蔽层是全面覆盖地设在该第一绝缘层的一第一表面上供用以防止该至少一第一电路层、该至少一第二电路层及该至少一芯片受到电磁干扰,有效地解决环境中的电磁波会对现有的芯片产品产生电磁干扰(emi,electromagnetic interference)而影响到产品内部的芯片或内部线路的问题。

5.为达成上述目的,本实用新型提供一种具电磁干扰屏蔽层的芯片封装结构,该芯片封装结构包含一基板、至少一第一电路层、至少一第二电路层、至少一芯片、一第一绝缘层及至少一电磁干扰屏蔽层;其中该基板具有一第一表面及相对的一第二表面,该基板的该第一表面上成型设有至少一盲孔;其中该至少一第一电路层是设在该基板的该第一表面上并能延伸设在该基板的该至少一盲孔的内壁面上,该至少一第一电路层具有一第一表面;其中该至少一第二电路层是设在该基板的该第二表面上,其中该至少一第一电路层能通过该基板的该至少一盲孔延伸并电性连接地至该至少一第二电路层;其中该至少一芯片是电性连接地设在该至少一第一电路层的该第一表面上;其中该第一绝缘层是设在该基板上且包覆住该至少一芯片,该第一绝缘层具有一第一表面;其中该至少一电磁干扰屏蔽层是由金属材料所构成,该至少一电磁干扰屏蔽层是全面覆盖地设在该第一绝缘层的该第一表面上供用以防止该至少一第一电路层、该至少一第二电路层及该至少一芯片受到电磁干扰;其中该至少一芯片是先与该至少一第一电路层的该第一表面电性连接,再通过该至少一第一电路层由该至少一盲孔的内壁面延伸至该至少一第二电路层上,以使该至少一芯片能由该至少一第二电路层向外电性连接,有助于增加于产品的市场竞争力。

6.在本实用新型一较佳实施例中,该至少一电磁干扰屏蔽层是由铜金属所构成。

7.在本实用新型一较佳实施例中,该至少一第二电路层进一步具有一第一表面;其中该至少一电磁干扰屏蔽层进一步具有一第一表面;其中该芯片封装结构更具有至少一第一外护层及至少一第二外护层;其中该至少一第一外护层是设在该至少一电磁干扰屏蔽层的该第一表面上;其中该至少一第二外护层是设于该至少一第二电路层的该第一表面上,该至少一第二外护层上具有至少一开口,该至少一开口能供该至少一第二电路层的该第一表面对外露出。

8.在本实用新型一较佳实施例中,该至少一第二外护层的该至少一开口上进一步设有一锡球与该至少一第二电路层的该第一表面电性连接,以使该至少一芯片能通过该锡球对外电性连接。

9.本实用新型更提供一种具电磁波干扰阻绝层的芯片封装结构,该芯片封装结构包含一基板、至少一第一电路层、至少一第二电路层、至少一芯片、一第一绝缘层、至少一电磁干扰屏蔽层及一第二绝缘层;其中该基板具有一第一表面及相对的一第二表面,该基板的该第一表面上成型设有至少一盲孔;其中该至少一第一电路层是设在该基板的该第一表面上并能延伸设在该基板的该至少一盲孔的内壁面上,该至少一第一电路层具有一第一表面;其中该至少一第二电路层是设在该基板的该第二表面上,其中该至少一第一电路层能通过该基板的该至少一盲孔延伸并电性连接地至该至少一第二电路层;其中该至少一芯片是电性连接地设在该至少一第一电路层的该第一表面上;其中该第一绝缘层是设在该基板上且包覆住该至少一芯片,该第一绝缘层具有一第一表面;其中该至少一电磁干扰屏蔽层是由金属材料所构成,该至少一电磁干扰屏蔽层是全面覆盖地设在该第一绝缘层的该第一表面上供用以防止该至少一第一电路层、该至少一第二电路层及该至少一芯片受到电磁干扰,其中该至少一电磁干扰屏蔽层具有一第一表面;其中该第二绝缘层是设在该至少一电磁干扰屏蔽层的该第一表面上;其中该至少一芯片是先与该至少一第一电路层的该第一表面电性连接,再通过该至少一第一电路层由该至少一盲孔的内壁面延伸至该至少一第二电路层上,以使该至少一芯片能由该至少一第二电路层向外电性连接。

10.在本实用新型一较佳实施例中,该至少一电磁干扰屏蔽层是由铜金属所构成。

11.在本实用新型一较佳实施例中,该至少一第二电路层进一步具有一第一表面;其中该第二绝缘层进一步具有一第一表面;其中该芯片封装结构更具有至少一第一外护层及至少一第二外护层;其中该至少一第一外护层是设在该第二绝缘层的该第一表面上;其中该至少一第二外护层是设于该至少一第二电路层的该第一表面上,该至少一第二外护层上具有至少一开口,该至少一开口能供该至少一第二电路层的该第一表面对外露出。

12.在本实用新型一较佳实施例中,该至少一第二外护层的该至少一开口上进一步设有一锡球与该至少一第二电路层的该第一表面电性连接,以使该至少一芯片能通过该锡球对外电性连接。

附图说明

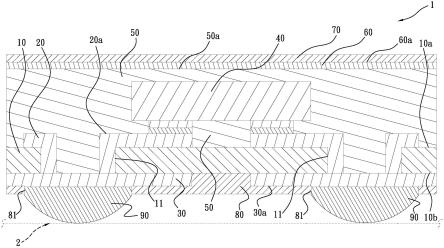

13.图1为本实用新型第一实施例的侧面剖视的平面示意图。

14.图2为本实用新型的基板上具有第一电路层及第二电路层的侧面剖视的平面示意图。

15.图3为图2中的第一电路层上设有芯片的侧面剖视的平面示意图。

16.图4为图3中的基板上设有第一绝缘层的侧面剖视的平面示意图。

17.图5为图4中的第一绝缘层上设有电磁干扰屏蔽层的侧面剖视的平面示意图。

18.图6为本实用新型第二实施例的侧面剖视的平面示意图。

19.图7为图3中的基板上设有第一绝缘层(图7中的第一绝缘层厚度较图 4中的第一绝缘层低)的侧面剖视的平面示意图。

20.图8为图7中的第一绝缘层上设有电磁干扰屏蔽层的侧面剖视的平面示意图。

21.图9为图8中的电磁干扰屏蔽层上设有第二绝缘层的侧面剖视的平面示意图。

22.附图标记说明:1-芯片封装结构;1a-芯片封装结构;10-基板;10a-第一表面;10b-第二表面;11-盲孔;20-第一电路层;20a-第一表面;30-第二电路层;30a-第一表面;40-芯片;50-第一绝缘层;50a-第一表面;60-电磁干扰屏蔽层;60a-第一表面;70-第一外护层;80-第二外护层;81-开口;90-锡球; 100-第二绝缘层;100a-第一表面;2-电路板。

具体实施方式

23.配合图示,将本实用新型的结构及其技术特征详述如下,其中各图示只用以说明本实用新型的结构关系及相关功能,因此各图示中各元件的尺寸并非依实际比例画制且非用以限制本实用新型。

24.参考图1及图6,本实用新型提供一种具电磁干扰屏蔽层的芯片封装结构1、1a,该芯片封装结构1、1a包含一基板10、至少一第一电路层20、至少一第二电路层30、至少一芯片40、一第一绝缘层50及至少一电磁干扰屏蔽层60;其中各电磁干扰屏蔽层60是由铜金属所构成但不限制。

25.该基板10具有一第一表面10a及相对的一第二表面10b,该基板10的该第一表面10a上成型设有至少一盲孔11,如图2所示;其中各盲孔11的数量进一步为两个但不限制,如图2所示。

26.各第一电路层20是设在该基板10的该第一表面10a上并能延伸设在该基板10的各盲孔11的内壁面上,各第一电路层20具有一第一表面20a,如图2所示;其中各第一电路层20的数量进一步为两个但不限制,如图2所示。

27.各第二电路层30是设在该基板10的该第二表面10b上,各第二电路层 30进一步具有一第一表面30a但不限制;其中各第一电路层20能通过该基板 10的各盲孔11延伸并电性连接地至各第二电路层30,如图2所示;其中各第二电路层30的数量进一步为两个但不限制,如图2所示。

28.各芯片40是电性连接地设在各第一电路层20的该第一表面20a上,如图3所示;其中各芯片40的数量进一步为一个但不限制,如图2所示。

29.该第一绝缘层50是设在该基板10上且包覆住各芯片40,该第一绝缘层 50具有一第一表面50a,如图4及图7所示。

30.其中,各芯片40是先与各第一电路层20的该第一表面20a电性连接,再通过各第一电路层20由各盲孔11的内壁面延伸至各第二电路层30上,以使各芯片40能由各第二电路层30向外电性连接,如图4及图7所示。

31.根据本实用新型的各电磁干扰屏蔽层60设置在该芯片封装结构1、1a上的位置的

不同,可进一步分为第一实施例(该芯片封装结构1)如图1所示及第二实施例(该芯片封装结构1a)如图6所示;其中该基板10、各第一电路层20、各第二电路层30、各芯片40、该第一绝缘层50在第一实施例(该芯片封装结构1)中或第二实施例(该芯片封装结构1a)中的结构构造或技术特征上大致上相同;其中第二实施例(该芯片封装结构1a)中的该第一绝缘层50厚度(如图7所示)较低于第一实施例(该芯片封装结构1)中的该第一绝缘层50厚度(如图4所示)但不限制,有利于减少产品的体积。

32.在图1中所示的实施例为本实用新型的第一实施例(该芯片封装结构1),在第一实施例中,各电磁干扰屏蔽层60是由金属材料所构成,各电磁干扰屏蔽层60是全面覆盖地设在该第一绝缘层50的该第一表面50a上供用以防止各第一电路层20、各第二电路层30及各芯片40受到电磁干扰如图1所示。

33.参考图1至图5,该芯片封装结构1更是由一种芯片封装结构的制造方法所制成,该制造方法包含下列步骤:

34.步骤s1:提供一该基板10,该基板10具有一第一表面10a及相对的一第二表面10b,该基板10的该第一表面10a上成型设有至少一盲孔11,如图 2所示;其中该基板10的该第一表面10a上设有至少一第一电路层20,且各第一电路层20能延伸设在该基板10的各盲孔11的内壁面上,其中各第一电路层20具有一第一表面20a,如图2所示;其中该基板10的该第二表面10b 上设有至少一第二电路层30,各第二电路层30具有一第一表面30a;其中各第一电路层20能通过该基板10的各盲孔11延伸并电性连接地至各第二电路层30,如图2所示。

35.步骤s2:在各第一电路层20的该第一表面20a上设置至少一芯片40与各第一电路层20电性连接,如图3所示,各芯片40是先与各第一电路层20 的该第一表面20a电性连接,再通过各第一电路层20由各盲孔11的内壁面延伸至各第二电路层30上,各芯片40以由各第二电路层30的该第一表面 30a向外电性连接,如图3所示。

36.步骤s3:在该基板10上设置一第一绝缘层50,如图4所示,且该第一绝缘层50包覆住各芯片40,该第一绝缘层50具有一第一表面50a,如图4 所示。

37.步骤s4:在该第一绝缘层50的该第一表面50a上全面覆盖地设置至少一电磁干扰屏蔽层60,如图5所示,各电磁干扰屏蔽层60供用以防止各第一电路层20、各第二电路层30及各芯片40受到电磁干扰,以完成该芯片封装结构1。

38.参考图1,各电磁干扰屏蔽层60进一步具有一第一表面60a但不限制;其中该芯片封装结构1更具有至少一第一外护层70及至少一第二外护层80 但不限制供用以保护该芯片封装结构1,以提升产品的良率;其中各第一外护层70是设在各电磁干扰屏蔽层60的该第一表面60a上;其中各第二外护层80是设于各第二电路层30的该第一表面30a上,各第二外护层80上具有至少一开口81,各开口81能供各第二电路层30的该第一表面30a对外露出。

39.参考图1,各第二外护层80的各开口81上进一步设有一锡球90与各第二电路层30的该第一表面30a电性连接但不限制,以使各芯片40能通过各锡球90对外电性连接,如与一电路板2(pcb)电性连接但不限制,以利于产品的多元化应用;其中各锡球90的数量进一步为两个但不限制,如图1所示。

40.在图6中所示的实施例为本实用新型的第二实施例(该芯片封装结构 1a),在第二实施例中,各电磁干扰屏蔽层60是由金属材料所构成,各电磁干扰屏蔽层60是全面覆盖地设在该第一绝缘层50的该第一表面50a上供用以防止各第一电路层20、各第二电路层30及

各芯片40受到电磁干扰,如图6所示。

41.其中该芯片封装结构1a更包含一第二绝缘层100,该第二绝缘层100是设在各电磁干扰屏蔽层60的该第一表面60a上,如图9所示,增加对各电磁干扰屏蔽层60的保护,以利于提升产品的良率。

42.参考图2、图3、图6至图9,该芯片封装结构1a更是由一种芯片封装结构的制造方法所制成,该制造方法包含下列步骤:

43.步骤s1:提供一该基板10,该基板10具有一第一表面10a及相对的一第二表面10b,该基板10的该第一表面10a上成型设有至少一盲孔11,如图 2所示;其中该基板10的该第一表面10a上设有至少一第一电路层20,且各第一电路层20能延伸设在该基板10的各盲孔11的内壁面上,其中各第一电路层20具有一第一表面20a,如图2所示;其中该基板10的该第二表面10b 上设有至少一第二电路层30,各第二电路层30具有一第一表面30a;其中各第一电路层20能通过该基板10的各盲孔11延伸并电性连接地至各第二电路层30,如图2所示。

44.步骤s2:在各第一电路层20的该第一表面20a上设置至少一芯片40与各第一电路层20电性连接,如图3所示,各芯片40是先与各第一电路层20 的该第一表面20a电性连接,再通过各第一电路层20由各盲孔11的内壁面延伸至各第二电路层30上,各芯片40以由各第二电路层30的该第一表面 30a向外电性连接,如图3所示。

45.步骤s3:在该基板10上设置一第一绝缘层50,如图7所示,且该第一绝缘层50包覆住各芯片40,该第一绝缘层50具有一第一表面50a,如图7 所示。

46.步骤s4:在该第一绝缘层50的该第一表面50a上全面覆盖地设置至少一电磁干扰屏蔽层60,如图8所示,各电磁干扰屏蔽层60供用以防止各第一电路层20、各第二电路层30及各芯片40受到电磁干扰。

47.步骤s5:在各电磁干扰屏蔽层60的该第一表面60a上设置一第二绝缘层100,如图9所示,以完成一芯片封装结构1a。

48.参考图6,该第二绝缘层100进一步具有一第一表面100a但不限制;其中该芯片封装结构1a更具有至少一第一外护层70及至少一第二外护层80但不限制供用以保护该芯片封装结构1,以提升产品的良率;其中各第一外护层70是设在该第二绝缘层100的该第一表面100a上;其中各第二外护层80 是设于各第二电路层30的该第一表面30a上,各第二外护层80上具有至少一开口81,各开口81能供各第二电路层30的该第一表面30a对外露出;其中各开口81的数量进一步为一个但不限制,如图6所示。

49.参考图6,各第二外护层80的各开口81上进一步设有一锡球90与各第二电路层30的该第一表面30a电性连接但不限制,以使各芯片40能通过各锡球90对外电性连接,如与一电路板2(pcb)电性连接但不限制,以利于产品的多元化应用;其中各锡球90的数量进一步为两个但不限制如图6所示。

50.本实用新型的芯片封装结构1、1a具有以下优点:

51.(1)本实用新型的各电磁干扰屏蔽层60是由金属材料所构成,各电磁干扰屏蔽层60是全面覆盖地设在该第一绝缘层50的该第一表面50a上供用以防止各第一电路层20、各第二电路层30及各芯片40受到电磁干扰(emi, electromagnetic interference),如图1所示,有效地解决环境中的电磁波会对现有的芯片产品产生电磁干扰而影响到产品内部的芯片或内部线路的问题,有助于增加于产品的市场竞争力,并使产品的应用符合5g技术或未

来6g技术的趋势需求。

52.(2)本实用新型的实用新型各电磁干扰屏蔽层60是由金属材料所构成,各电磁干扰屏蔽层60是全面覆盖地设在该第一绝缘层50的该第一表面50a 上,有助于帮助产品增加散热的功效,使得产品的使用寿命提升,且也降低发生故障的几率,同时提升了产品的良率,有助于增加产品的市场竞争力。

53.以上仅为本实用新型的优选实施例,其对本实用新型而言仅是说明性的,而非限制性的;本领域普通技术人员理解,在本实用新型权利要求所限定的精神和范围内可对其进行许多改变,修改,甚至等效变更,但都将落入本实用新型的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1