芯片封装结构的制作方法

1.本实用新型涉及半导体封装技术领域,尤其是涉及一种将芯片以封装体的形式与基板互连的芯片封装结构。

背景技术:

2.现有技术中,倒装芯片封装是将工作面上制有凸点电极的芯片朝下,与封装衬底直接键合,通过芯片上呈阵列排布的凸点来实现芯片与封装衬底的互连。封装衬底一般选用基板。基板包括至少一层介电层、堆叠在介电层上下表面的线路层以及焊盘层,相邻线路层之间电连接,线路层与焊盘层之间电连接。

3.为了满足集成化、高密度化的封装要求,一个封装结构往往需要设置更多的线路以及引脚数目,这就需要设置更多的基板层数(增加线路层),以便于布局设计电路。

4.基板的层数越多,排版布线难度增加,制作工艺也越复杂,降低了封装结构的集成度;这也不可避免的导致成本增加。

5.因此,亟需一种能够减少基板层数,提高电路集成度和性能的芯片封装结构。

技术实现要素:

6.本实用新型的目的在于克服现有技术中存在的缺陷,提供一种将芯片以封装体的形式与基板互连的芯片封装结构,减少基板层数,提高电路集成度和性能。

7.为解决上述技术问题,本实用新型提供了一种芯片封装结构,其包括基板和倒装于基板表面的芯片封装体,所述芯片封装体包括芯片、塑封层、支撑层和多层布线层,所述芯片具有相对的正面和背面,所述芯片背面依次设有塑封层和支撑层,所述塑封层包覆芯片背面和侧面,所述芯片正面和多层布线层电连接,所述多层布线层通过导电凸块贴装于基板表面。

8.在一些实施方式中,芯片正面通过临时键合层倒装于载体晶圆,之后在所述芯片背面依次设置塑封层和支撑层;去除所述临时键合层和载体晶圆后,在所述芯片正面压区电连接于多层布线层。

9.在一些实施方式中,支撑层由硅材料制成。

10.在一些实施方式中,基板包括至少一层介电层、堆叠在所述介电层上下表面的线路层以及焊盘层,相邻所述线路层之间电连接,所述线路层与焊盘层之间电连接;所述多层布线层通过导电凸块与焊盘层电连接。

11.在一些实施方式中,芯片封装结构还包括散热片和焊球,所述散热片包覆芯片封装体并设于基板上,所述焊球设于基板的背面。

12.在一些实施方式中,芯片封装体和散热片之间设有金属导热层。

13.在一些实施方式中,金属导热层为铟或铟合金。

14.在一些实施方式中,基板表面设有被动元件。

15.在一些实施方式中,导电凸块的间距为40~400μm,相对于传统的焊球间距更小。

16.本实用新型提供的芯片封装结构,与现有技术相比,具有以下有益效果:

17.本技术通过细线宽和窄间距的多层布线层形成芯片封装体,再将芯片封装体连接到基板上,代替基板内的部分线路层,减少了基板排版布线的困难程度,也减少布线和装配的差错,降低安装强度;也减少了基板层数;

18.同时,将芯片以封装体的形式与基板互连的芯片封装结构,也增加了基板设计的灵活性,使器件能以更紧凑的方式排列在基板上,提高电路集成度和性能。

附图说明

19.图1是本实用新型中芯片封装体制备过程的结构示意图;

20.图2是本实用新型中单颗芯片封装体的结构示意图;

21.图3是本实用新型中单颗芯片封装体连接到基板的结构示意图;

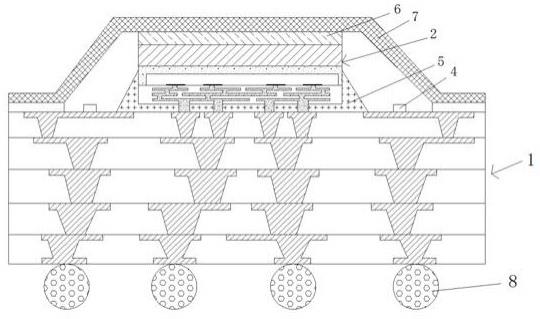

22.图4是本实用新型所述的芯片封装结构一种实施方式的结构示意图。

具体实施方式

23.下面结合附图和实施例,对本实用新型的具体实施方式作进一步描述。以下实施例仅用于更加清楚地说明本实用新型的技术方案,而不能以此来限制本实用新型的保护范围。

24.本实用新型提供了一种芯片封装结构,包括基板1和倒装于基板1表面的芯片封装体2。其将芯片3以封装体的形式与基板1实现互连,减少基板1层数,增加基板1设计的灵活性,使器件能以更紧凑的方式排列在基板1上,提高电路集成度和性能。

25.图1示意性的展示了芯片封装体2的制备过程。具体的,芯片封装体2包括芯片3、塑封层201、支撑层202和多层布线层203。芯片3具有相对的正面和背面,芯片3正面设有压区301。如图1中的1-1所示,芯片3正面通过临时键合层204倒装于载体晶圆205。之后如图1中的1-2,对芯片3进行塑封,具体是使芯片3背面和侧面被塑封层201包覆;在塑封层201外部粘合支撑层202。该支撑层202用于支撑整个芯片封装体2,完成整个封装结构,支撑层202由硅材料制成。如图1中的1-3所示,去除临时键合层204和载体晶圆205后,将芯片3正面压区301电连接于多层布线层203。最后,在多层布线层203表面电连接导电凸块207,以完成如图1中的1-4所示的芯片封装体2。

26.多层布线层203设置在绝缘介质层206上。两两布线层之间设有绝缘膜。具体是在绝缘介质层206上涂上光刻胶,利用光刻工艺开出图形开口,形成图形化的绝缘介质层206,在开口内电镀,形成布线层;重复以上步骤,形成多层布线层203。多层布线层203可以代替基板1内的部分线路层102,整体结构简单,可以直接由封装厂完成,降低制造成本。本实施中,利用bumping工艺能够制备2~8层布线层,线路能够达到1~20μm的较窄间距,从而形成高密度的有机转接层,以此作为多层布线层。通过细线宽和窄间距的多层布线层形成芯片封装体,再将芯片封装体连接到基板上,代替基板内的部分线路层,减少了基板排版布线的困难程度,也减少布线和装配的差错,降低安装强度;也减少了基板层数。

27.图1中1-4所示的芯片封装体2切割成如图2所示的单颗芯片封装体2之后,再和基板1电连接。

28.如图3所示,基板1包括至少一层介电层101、堆叠在介电层101上下表面的线路层

102以及焊盘层103,相邻线路层102之间通过导电过孔104电连接,线路层102与焊盘层103之间也通过导电过孔104电连接。单颗芯片封装体2中的多层布线层203通过导电凸块207与焊盘层103电连接,以实现单颗芯片封装体2和基板1的电连接,接线、安装简单便捷,减少了安装难度和强度。

29.单颗芯片封装体2安装到基板1后,可对基板1进一步设计。将芯片以封装体的形式与基板1互连的芯片封装结构,增加了基板设计的灵活性,使器件能以更紧凑的方式排列在基板上,提高电路集成度和性能。

30.如图4所示,在基板1表面其余位置连接被动元件4,利用环氧树脂或其他的填料对芯片封装体2进行底部填充5,该底部填充5可将芯片封装体2和基板1紧紧地黏结在一起,还可降低因芯片封装体2与基板1热膨胀系数(cte)不匹配在焊点上产生的应力。然后安装散热片7。具体的,先在芯片封装体2的支撑层202表面涂覆金属导热层6,在基板1的边缘涂覆粘结材料,然后将散热片7贴装在基板1表面。金属导热层6为铟或铟合金,能够将芯片封装体2散发的热量传导至散热片7,有助于增加散热效率,使芯片封装体2稳定工作。同时,金属导热层6也具有一定的粘性,起到固定散热片7的作用。最后将焊球8焊接于基板1背面,焊球8与基板1背面的焊盘相连接。

31.以上所述仅是本实用新型的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型技术原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1