一种QFN封装结构、射频收发模组结构及电子设备的制作方法

一种qfn封装结构、射频收发模组结构及电子设备

技术领域

1.本技术涉及封装领域,尤其涉及一种qfn封装结构、射频收发模组结构及电子设备。

背景技术:

2.目前很多芯片在大发射功率的条件下容易产生辐射超标的问题,一般来说,当芯片支持15dbm的发射功率时,可能超出fcc(federal communications commission,国联邦通信委员会)规定的对谐波辐射的限制20db以上。目前市面上产品为了解决该问题,一般通过额外增加滤波器件,或增加芯片屏蔽罩,但这些方案都会大幅度增加成本或者使得芯片体积增加,因此,如何更低成本地解决辐射超标成为亟待解决的技术问题。

技术实现要素:

3.针对辐射超标的问题,本技术实施例提供了一种qfn封装结构、射频收发模组结构及电子设备。

4.本技术的实施例的第一方面提供了一种qfn封装结构,包括基板、epad焊接区、芯片和qfn封装引脚,epad焊接区设置于基板的表面,芯片设置于epad焊接区的表面;

5.qfn封装引脚围绕epad焊接区并且设置于基板的表面;qfn封装引脚用于与qfn封装结构的外部的器件连接;qfn封装引脚与芯片连接;

6.芯片设置于epad焊接区的非中心位置的表面;

7.芯片的射频发射引脚通过至少三根第一绑定线连接至qfn封装引脚的射频发射引脚。

8.根据第一方面,在一种可能的实现方式中,芯片的射频接收引脚通过第二绑定线连接至qfn封装引脚的射频接收引脚;

9.第一绑定线的长度小于或者等于第二绑定线的长度。

10.根据第一方面,在一种可能的实现方式中,第二绑定线的数量为1。

11.根据第一方面,在一种可能的实现方式中,第一绑定线的打线弧高大于或者等于70um并且小于或者等于80um,第一绑定线的长度小于或者等于第二绑定线的长度。

12.根据第一方面,在一种可能的实现方式中,芯片的射频发射地引脚通过第三绑定线连接至qfn封装引脚的射频发射地引脚,芯片的射频接收地引脚通过第四绑定线连接至qfn封装引脚的射频接收地引脚;

13.芯片的射频发射引脚分别与芯片的射频发射地引脚、芯片的射频接收引脚相邻;芯片的射频接收引脚与芯片的射频接收地引脚相邻;

14.qfn封装引脚的射频发射引脚分别与qfn封装引脚的射频发射地引脚、芯片的射频接收引脚相邻;qfn封装引脚的射频接收引脚与qfn封装引脚的射频接收地引脚相邻。

15.根据第一方面,在一种可能的实现方式中,第一绑定线与第三绑定线之间的距离大于或者等于30um并且小于或者等于100um,第三绑定线的打线弧高等于第一绑定线的打

线弧高;

16.第一绑定线的长度小于或者等于第三绑定线、第四绑定线的长度。

17.根据第一方面,在一种可能的实现方式中,芯片内设置有滤波电容,滤波电容与芯片的射频发射地引脚与芯片的射频发射引脚连接。

18.本技术的实施例的第二方面提供了一种qfn封装结构,包括基板、epad焊接区、芯片和qfn封装引脚,epad焊接区设置于基板的表面,芯片设置于epad焊接区的表面;

19.qfn封装引脚围绕epad焊接区并且设置于基板的表面;qfn封装引脚用于与qfn封装结构的外部的器件连接;qfn封装引脚与芯片连接;

20.芯片设置于epad焊接区的非中心位置的表面;

21.芯片的射频收发引脚通过至少三根第一绑定线连接至qfn封装引脚的射频收发引脚。

22.根据第二方面,在一种可能的实现方式中,第一绑定线的打线弧高大于或者等于70um并且小于或者等于80um。

23.根据第二方面,在一种可能的实现方式中,芯片的射频发射地引脚通过第三绑定线连接至qfn封装引脚的射频发射地引脚,芯片的射频接收地引脚通过第四绑定线连接至qfn封装引脚的射频接收地引脚;

24.芯片的射频收发引脚分别与芯片的射频发射地引脚、芯片的射频接收地引脚相邻;

25.qfn封装引脚的射频收发引脚与qfn封装引脚的射频发射地引脚、qfn封装引脚的射频接收地引脚相邻。

26.根据第二方面,在一种可能的实现方式中,第一绑定线与第三绑定线之间的距离大于或者等于30um并且小于或者等于100um,第三绑定线的打线弧高等于第一绑定线的打线弧高;第一绑定线的长度小于或者等于第三绑定线、第四绑定线的长度。

27.根据第二方面,在一种可能的实现方式中,芯片内设置有滤波电容,滤波电容与芯片的射频发射地引脚与芯片的射频收发引脚连接。

28.本技术的实施例的第三方面提供了一种射频收发模组结构,包括天线、匹配网络电路、第一电感和第一方面中任一项的qfn封装结构,天线与匹配网络电路连接,匹配网络电路与qfn封装引脚的射频发射引脚连接;第一电感分别连接匹配网络电路与qfn封装引脚的射频接收引脚连接。

29.根据第三方面,在一种可能的实现方式中,匹配网络电路包括第一电容、第二电容、第三电容以及第二电感;

30.天线与第一电容的第一端连接;

31.第一电容的第二端分别连接至第二电容的第一端与第二电感的第一端;

32.第二电容的第二端接地;

33.第二电感的第二端分别连接第三电容的第一端、qfn封装引脚的射频发射引脚以及第一电感;

34.第三电容的第二端接地。

35.本技术的实施例的第四方面提供了一种射频收发模组结构,包括天线、匹配网络电路与第二方面中任一项的qfn封装结构,天线与匹配网络电路连接,匹配网络电路与qfn

封装引脚的射频收发引脚连接。

36.根据第四方面,在一种可能的实现方式中,匹配网络电路包括第一电容、第二电容、第三电容以及第二电感;

37.天线与第一电容的第一端连接;

38.第一电容的第二端分别连接至第二电容的第一端与第二电感的第一端;

39.第二电容的第二端接地;

40.第二电感的第二端分别连接第三电容的第一端与qfn封装引脚的射频收发引脚;

41.第三电容的第二端接地。

42.本技术的实施例的第五方面提供了一种电子设备,包括外壳和第三方面和第四方面中任一项的射频收发模组结构,射频收发模组结构设置于外壳内。

43.与现有技术相比,本技术实施例的有益效果在于,芯片的射频发射引脚通过至少三根第一绑定线连接至所述qfn封装引脚的射频发射引脚,使得第一绑定线与epad焊接区的寄生电容较大,从而增强对谐波的滤波作用,从而减少谐波对外的辐射,成本较低的改善了辐射超标的问题。

附图说明

44.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

45.图1为本技术实施例提供的一三元素匹配网络电路的示意图;

46.图2为本技术实施例提供的一三元素匹配网络电路的谐波特性的示意图;

47.图3为本技术实施例提供的一五元素匹配网络电路的示意图;

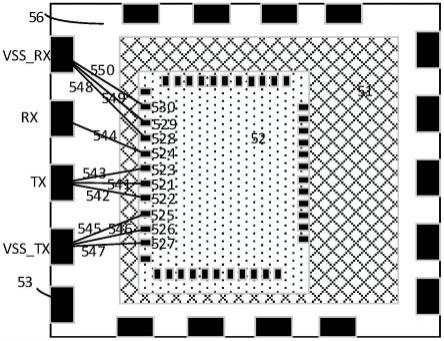

48.图4为本技术实施例提供的一qfn封装结构的示意图;

49.图5为本技术实施例提供的又一qfn封装结构的示意图;

50.图6为本技术实施例提供的再一qfn封装结构的示意图;

51.图7为本技术实施例提供的再一qfn封装结构的示意图;

52.图8为本技术实施例提供的再一qfn封装结构的示意图;

53.图9为本技术实施例提供的再一qfn封装结构的示意图;

54.图10为本技术实施例提供的一射频收发模组结构的示意图;

55.图11为本技术实施例提供的又一射频收发模组结构的示意图。

具体实施方式

56.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术的部分实施例采用举例的方式进行详细的阐述。然而,本领域的普通技术人员可以理解,在各例子中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。

57.以蓝牙的辐射法规为例进行说明,表1为全球针对蓝牙模组的辐射法规,不同国家均对2.4ghz以外的谐波的能量有要求,并且该要求日益严苛。

58.表1:辐射法规

[0059][0060]

以ble(bluetooth of low energy,低功耗蓝牙)芯片为例,目前市面上的ble芯片的辐射能量容易超标,不容易通过国际标准认证。例如,当蓝牙芯片需要发射15dbm功率时,测试得到的辐射超标20db。辐射超标是因为ble芯片本身会因为非线性失真等原因产生带外的干扰,因此容易影响其他设备。简单来说,非线性失真会使得谐波的占比提高,这种现象称之为thd(total harmonic distortion,总谐波失真)。ble芯片的发射功率增加,谐波能量也会增加,因而导致ble芯片的谐波辐射超出规定的谐波辐射限制。

[0061]

图1示意了发射引脚(tx)的一种匹配网络电路以用于实现阻抗匹配,该匹配网络电路还用于对发射能量进行滤波处理,可以采用三元素匹配网络(3elements c-l-c matching network)电路的方案进行阻抗匹配。如图2所示为图1所示的三元素匹配网络电路的谐波特性,可以看出,图1所示的三元素匹配网络电路针对二次及以上谐波的截止深度不太够。截止深度又称之为阻带抑制度,阻带抑制度是衡量滤波器选择性能好坏的重要指标,该指标越高说明对带外干扰信号抑制的越好。本技术实施例中,匹配网络电路的作用是把芯片的pa(power amplifier,功率放大器)的阻抗匹配到和天线(antenna)一样,因此,匹配网络电路对电感和电容的取值要求较高。在一些实施例中,pa内部可以集成50欧姆的阻抗匹配设计网络,对于一些高功率pa,可以将匹配网络电路设置在集成芯片的外部,以减小芯片面积。高功率pa的输出阻抗例如为10ω,小功率pa的输出阻抗例如为25ω,对于高功率pa来说,可以通过π型匹配电路实现50欧姆的阻抗匹配,pa的特性阻抗影响外围匹配电路的值。

[0062]

下面的实施例通过qfn封装结构形成电容和电感,因此,匹配网络电路对电容和电感的取值要求宽松了很多。下面的实施例通过qfn封装结构形成寄生电容和寄生电感,也可以理解为是在qfn封装结构内形成了低通滤波器以实现对谐波的过滤。下面的实施例通过优化qfn封装结构以引入寄生电容和寄生电感,另外qfn封装结构还可以跟qfn封装结构外

部的三元素匹配网络电路组合起来以形成如图3所示的五元素匹配网络(5elements c-l-c matching network)电路的方案,可以提升对谐波的抑制强度,从而降低谐波辐射能量,图3所示的五元素匹配网络电路可以适用于需要发射15dbm功率的蓝牙芯片,本实施例中的芯片可以包括pa,该pa在15dbm的发射功率下的输出阻抗大约为10ω。如图4所示为图3所示的五元素匹配网络电路的谐波特性,可以看出,滤波器的阶数更多,过渡带(2.4ghz-4.8ghz)的下降速度更快,增益曲线的斜率更大,这样在4.8ghz的时候对谐波的能量可以抑制得更低。

[0063]

如图5所示的qfn封装(quad flat no-leads package,方形扁平无引脚封装)结构的底视图,包括epad(exposed pad)焊接区51、芯片52和qfn封装引脚53,其中,epad焊接区51设置于基板56的表面,芯片52设置于epad焊接区51的表面,qfn封装引脚53与芯片52连接,qfn封装引脚53包括射频发射地引脚vss_tx、射频接收地引脚vss_rx、射频接收引脚rx和射频发射引脚tx,qfn封装引脚53围绕epad焊接区51并且设置于基板56的表面的边缘位置,qfn封装引脚53用于与qfn封装结构的外部的器件电连接,例如,与qfn封装结构外部的匹配网络电路连接,或者qfn封装引脚53还用于与其他芯片连接以实现用户预设的功能。芯片52设置于epad焊接区51的非中心位置的表面,即芯片52设置于偏离epad焊接区51的中心位置。如图5所示,相比于qfn封装引脚的其他引脚,芯片52设置于更靠近qfn封装引脚的射频发射引脚tx。epad焊接区51可以理解为金属的裸露焊盘,一般来说,epad焊接区51的中心与qfn封装结构的中心重合,epad焊接区51处于基板56的下方,芯片52处于epad焊接区51的下方,epad焊接区51的中心与基板56的中心重合,epad焊接区可以为设置于qfn封装结构的中心区域的一块铜皮,epad焊接区一般用作gnd,epad焊接区与gnd相连,可以用来散热,例如,epad焊接区可以连接到外围pcb(printed circuit board,印制电路板)上的gnd。芯片52的至少三个射频发射引脚521、522、523分别通过第一绑定(bounding)线541、542、543连接至qfn封装引脚的射频发射引脚tx。本实施例通过增加第一绑定线的数目,可以减小等效电阻(equivalent series resistance,esr),从而可以减小第一绑定线对发射功率形成插损(insertion loss),避免导致芯片的发射功率降低。可以理解的是并联的第一绑定线越多,第一绑定线引入的电阻越小,因此,插损越小。本技术实施例设置了2根以上的射频发射引脚的绑定线,通过并联至少三根第一绑定线来减小插损。

[0064]

本实施例中,一方面,芯片的射频发射引脚与qfn封装引脚的射频发射引脚之间的第一绑定线的数目设置为至少3根可以增加寄生电容,以增强对谐波的滤波器效果,避免了额外增加滤波器件或增加芯片屏蔽罩,可以低成本的改善辐射超标的问题,同时也避免了增加芯片体积。

[0065]

另外一方面,绑定线越多,对芯片的射频发射引脚来说,2.4ghz工作频率下的插损越小。一般来说,芯片之外都会存在插损,比如绑定线带来的插损,比如外围pcb走线带来的插损,以及匹配器件用到的电感带来的插损。对于tx而言,因为是芯片发出的干净的特定频率的信号,而且发射功率大,所以关键的是减小通过tx发射的信号的损失。

[0066]

基于上述实施例公开的内容,本实施例中,如图5所述,qfn封装结构还包括基板56,epad焊接区设置于基板的表面,qfn封装引脚设置于基板的表面的边缘。

[0067]

基于上述实施例公开的内容,本实施例中,第一绑定线的打线弧高大于或者等于50um并且小于100um。tx的寄生电容是第一绑定线和epad焊接区51共同形成,类似极板电容

原理。如图6所示,第一绑定线542越靠近epad焊接区51,第一绑定线和epad焊接区之间形成的寄生电容就越大。因此,图5中第一绑定线542的打线弧高h1设置得尽可能小,使得第一绑定线542尽量靠近epad焊接区51,以使得寄生电容尽可能大,以便于更好的过滤谐波。但是h1太小不利于工艺实现,因此,h1设置为大于或者等于50um并且小于100um。例如,h1可以设计为大于或者等于70um并且小于或者等于80um,h1设置为大于或者等于70um并且小于或者等于80um可以增加第一绑定线和epad焊接区51之间形成的寄生电容并且便于工艺实现,另外,qfn封装结构的可靠性较好。在工艺允许且不增加成本的情况下,h1尽量取小,h1可以设置为70um。另外,绑定线本身具备寄生电感,tx处的寄生电感由自身绑定线的长度决定,一般情况下,1mm长度的绑定线对应有1nh的寄生电感。因此,可以通过在qfn封装结构内引入寄生电容和寄生电感,并且与qfn封装结构外部的匹配网络电路一起对谐波进行滤波。

[0068]

基于上述实施例公开的内容,本实施例中,如图5所示,芯片的射频发射地引脚525、526、527分别通过第三绑定线545、546、547连接至qfn封装引脚的射频发射地引脚vss_tx,芯片的射频接收地引脚528、529、530通过第四绑定线548、549、550连接至qfn封装引脚的射频接收地引脚vss_rx。根据平行板电容器的电容的计算公式c=ε*s/d,其中,ε为极板间介质的介电常数,s为极板面积,d为极板间的距离,本实施例中,为了增加第一绑定线与第三绑定线形成的寄生电容和寄生电感,还可以使得第一绑定线与和第三绑定线之间的距离d1尽量小,具体的,第一绑定线542与第三绑定线545之间距离d1小于或者等于100um,并且,第三绑定线的打线弧高等于第一绑定线的打线弧高,使得第一绑定线与和第三绑定线之间的距离d1尽量小。又因为绑定线之间的距离太近不便于工艺实现,因此,请参考图6,第一绑定线542与第三绑定线545之间距离d1可以配置为大于或者等于30um并且小于或者等于100um,例如为50um,以增加第一绑定线与和第三绑定线形成的寄生电容,使得第一绑定线与和第三绑定线形成的寄生电容满足1pf≥c≤7pf,例如为3.6pf。本实施例中,寄生电感的取值满足:1nh≥l≤5nh,例如为2.4nh。本实施例中,为了统一封装工艺,第二绑定线的打线弧高与第四绑定线的打线弧高h2的值可以设置为与h1相等。

[0069]

基于上述实施例公开的内容,本实施例中,请参考图5,芯片52设置于epad焊接区51的非中心位置的表面,具体的,芯片52的射频发射引脚521、522、523靠近qfn封装引脚的射频发射引脚tx。相较于芯片52的其他引脚,芯片52的射频发射引脚521、522、523与qfn封装引脚的射频发射引脚tx的距离最近,因此,相较于其他绑定线来说,第一绑定线521、522、523的长度小于或者等于其他绑定线的长度,例如,第一绑定线的长度小于或者等于第二绑定线544、第三绑定线545、546、547、第四绑定线548、549、550的长度。芯片设置于所述epad焊接区的非中心位置的表面可以使得第一绑定线的长度尽可能短,例如,可以使得qfn封装引脚的射频发射引脚tx正对着芯片52的射频发射引脚。一般情况下,绑定线的长度可以约束寄生电感,比如1mm的绑定线有1nh的寄生电感,绑定线可以引入的寄生电感为2.4nh,另外,绑定线也不是越长越好,因为绑定线越长,自身寄生电阻会影响发射功率插损。本实施例可以采用3mm以内的绑定线长度,第一绑定线的长度可以设置得最小以减小插损。对于射频信号的发射来说,因为是芯片发出的干净的特定频率的信号,而且发射功率大,所以关键的是减小通过tx发射的信号的损失,即减小插损对射频的发射性能尤为重要。

[0070]

基于上述实施例公开的内容,本实施例中,为了增加接收灵敏度,芯片的射频接收引脚与qfn封装引脚的射频接收引脚仅仅通过一根第二绑定线连接,目的为了通过一根第

二绑定线形成较大的寄生电感从而对谐波形成抑制,进而提高芯片接收射频信号时的snr(signal-noise ratio,信噪比)。可以理解的是,绑定线的存在会导致寄生电感的产生,电感并联时,总电感量减少,因此只设置一根第二绑定线可以保证寄生电感最大从而对谐波进行抑制。对于射频信号的接收来说,较为关键的参数是snr,rx的绑定线形成的寄生电感可以抑制2.4g以外的干扰,可以提升snr,所以本实施例中rx的绑定线的寄生电感可以设置得稍大,因为多组绑定线并联以后电感是成倍减小的,那么就可以不用多组绑定线并联。另外绑定线数量增加也会导致成本增加,所以芯片的射频接收引脚与qfn封装引脚的射频接收引脚可以仅仅通过一根第二绑定线连接。如图5所示,芯片52的射频接收引脚524通过第二绑定线544连接至qfn封装引脚的射频接收引脚rx,第二绑定线的数量为1。本实施例中,芯片的射频接收性能受寄生电感的影响较大,芯片的射频接收性能主要包括接收灵敏度,可以通过引入寄生电感以阻止高频噪声,从而实现在高发射功率时也可以有较高的接收灵敏度。芯片的射频发射性能受寄生电容的影响较大,芯片的射频发射引脚的谐波可以通过寄生电容传输到芯片的射频发射地引脚。对于射频信号的接收而言,最重要的参数是snr,在有用信号的功率较小的情况下,如果接收灵敏度较低的话很难被成功接收,例如,接收灵敏度为-99dbm,在这种情况下减小输入信号的噪声是比较关键的,所以针对rx的绑定线,可以增加寄生电感,这样可以抑制2.4ghz以外的干扰,以提高snr。

[0071]

基于上述实施例公开的内容,本实施例中,如图5所示,芯片的射频发射地引脚525、526、527和芯片的射频接收地引脚524分别设置在芯片的射频发射引脚521、522、523的两旁,qfn封装引脚的射频发射地引脚vss_tx和qfn封装引脚的射频接收地引脚rx分别设置在qfn封装引脚的射频发射引脚tx的两旁。芯片的射频发射引脚分别与芯片的射频发射地引脚、芯片的射频接收引脚相邻,芯片的射频接收引脚524与芯片的射频接收地引脚528相邻。qfn封装引脚的射频发射引脚tx分别与qfn封装引脚的射频发射地引脚vss_tx、qfn封装引脚的射频接收引脚rx相邻。qfn封装引脚的射频接收引脚rx与qfn封装引脚的射频接收地引脚vss_rx相邻。采用这种引脚的排布方式的话,可以便于通过多根第一绑定线引入的寄生电容将高次谐波从芯片的射频发射引脚导入到芯片的射频发射地引脚,这样高次谐波就不容易传导到qfn封装结构外的射频通路,以减少对外的辐射,从而可以通过各种法规对辐射能量的测试要求。若在芯片的内部设置有连接到tx与vss_tx的电容c4,例如,c4的大小可以为1~8pf,也可以通过电容c4将高次谐波从芯片的射频发射引脚导入到芯片的射频发射地引脚,这样高次谐波就不容易传导到qfn封装结构外的射频通路,以减少对外的辐射。本实施例中,射频发射引脚的两端设置有射频发射地引脚和射频接收地引脚,射频发射引脚的谐波更容易传导到射频发射地引脚和射频接收地引脚,减少了谐波对外的辐射能量。本实施例通过在tx的上下端用vss_rx和vss_tx进行包围,这样谐波能量可以在qfn封装结构内部通过vss_rx或vss_tx形成的闭合地回路传导,减少对外的辐射。

[0072]

基于上述实施例公开的内容,请参考图7,本实施例中,也可以通过在芯片52的内部增加设置于芯片的射频发射引脚521与芯片的射频发射地引脚526之间的滤波电容c4,即在芯片内部加入滤波电容c4,滤波电容c4分别与芯片的射频发射地引脚526、芯片的射频发射引脚521连接,并且,滤波电容c4与芯片和qfn封装引脚的绑定线引入的寄生电感一起形成滤波电路,对高次谐波有过滤作用。

[0073]

基于上述实施例公开的内容,本实施例提出另一种qfn封装结构,与前述实施例不

同的是,本实施例的qfn封装结构中的芯片的射频接收引脚与芯片的射频发射引脚共用一个引脚,其共用的引脚称之为射频收发引脚。请参考图8所示的qfn封装结构的底视图,包括epad焊接区81、芯片82和qfn封装引脚83,芯片82设置于epad焊接区81的表面,qfn封装引脚83与芯片82连接,qfn封装引脚83包括射频收发引脚trx、射频发射地引脚vss_tx与射频接收地引脚vss_rx,芯片82设置于epad焊接区81的非中心位置的表面。芯片82的射频收发引脚821、822、823分别通过至少三根第一绑定线841、842、843连接至qfn封装引脚的射频收发引脚trx。qfn封装结构还包括基板86,epad焊接区81设置于基板86的表面,qfn封装引脚83围绕epad焊接区81并且设置于基板86的表面的边缘,qfn封装引脚83用于与qfn封装结构的外部的器件连接。

[0074]

基于上述实施例公开的内容,本实施例中,请参考图9,第一绑定线的打线弧高h1大于或者等于50um并且小于100um。trx的寄生电容是第一绑定线和epad焊接区51共同形成,类似极板电容原理。如图9所示,第一绑定线821越靠近epad焊接区81,第一绑定线821和epad焊接区81之间形成的寄生电容就越大。因此,图9中第一绑定线821的打线弧高h1设置得尽可能小,使得第一绑定线821尽量靠近epad焊接区81,但是h1太小不利于工艺实现,因此,h1设置为大于或者等于50um并且小于100um。例如,h1可以设计为大于或者等于70um并且小于或者等于80um。h1设置为大于或者等于70um并且小于或者等于80um可以增加绑定线和epad焊接区81之间形成的寄生电容并且便于工艺实现,另外,qfn封装结构的可靠性较好。在工艺允许且不增加成本的情况下,h1尽量取小,h1可以设置为70um。另外,绑定线本身具备寄生电感,trx处的寄生电感由自身绑定线的长度决定,比如一般情况下1mm长度的绑定线对应有1nh的寄生电感。因此,可以通过在qfn封装结构内引入寄生电容和寄生电感,并且可以与qfn封装结构外部的匹配网络电路一起对谐波进行滤波。

[0075]

基于上述实施例公开的内容,本实施例中,请参考图8,芯片的射频发射地引脚825、826、827分别通过第三绑定线845、846、847连接至qfn封装引脚的射频发射地引脚vss_tx,芯片的射频接收地引脚828、829、830分别通过第四绑定线848、849、850连接至qfn封装引脚的射频接收地引脚vss_rx。芯片的射频收发引脚分别与芯片的射频发射地引脚、芯片的射频接收地引脚相邻,qfn封装引脚的射频收发引脚trx分别与qfn封装引脚的射频发射地引脚vss_tx、qfn封装引脚的射频接收地引脚vss_rx相邻。本实施例中,射频收发引脚的两端设置有射频发射地引脚和射频接收地引脚,射频收发引脚的谐波更容易传导到射频发射地引脚和射频接收地引脚,减少了谐波对外的辐射能量。本实施例通过在trx的上下端用vss_rx和vss_tx进行包围,这样谐波能量可以通过封装内部的vss_rx或vss_tx形成闭合地回路,减少对外的辐射。

[0076]

基于上述实施例公开的内容,本实施例中,为了增加第一绑定线与第三绑定线形成的寄生电容和寄生电感,还可以使得第一绑定线与和第三绑定线之间的距离d1尽量小,具体的,请参考图9,第一绑定线842与第三绑定线845之间距离d1小于或者等于100um,并且,第三绑定线的打线弧高等于第一绑定线的打线弧高,使得第一绑定线与和第三绑定线之间的距离d1尽量小。又因为绑定线之间的距离太近不便于工艺实现,因此,第一绑定线842与第三绑定线845之间的距离大于或者等于30um并且小于或者等于100um,例如为50um,以增加第一绑定线与和第三绑定线形成的寄生电容,使得第一绑定线与和第三绑定线形成的寄生电容满足1pf≥c≤7pf,例如为3.6pf。第一绑定线841、842、843的长度小于或者等于

其他绑定线的长度,例如,第一绑定线841、842、843的长度小于或者等于第三绑定线845、846、847、第四绑定线848、849、850的长度。本实施例中,为了统一封装工艺,第四绑定线的打线弧高h2的值可以设置为与h1相等。

[0077]

另外,本实施例中,也可以通过在芯片82的内部增加设置于芯片的射频收发引脚822与芯片的射频发射地引脚825之间的滤波电容c4,即在芯片内部加入滤波电容c4,滤波电容c4的两端分别与芯片的射频发射地引脚825、芯片的射频收发引脚822连接,并且,滤波电容c4与芯片和qfn封装引脚的绑定线引入的寄生电感一起形成滤波电路,对高次谐波有过滤作用。

[0078]

本技术实施例提出了封装级的解决方案,可以应用于蓝牙芯片中,能够更好的解决辐射超标的问题,以支持更高的发射功率,本技术实施例的方案也可以应用于物联网领域需要射频收发的应用场景。

[0079]

基于上述实施例公开的内容,本实施例提出射频收发模组结构,如图10所示,包括qfn封装结构101、天线102、匹配网络电路103和第一电感l1,天线102与匹配网络电路103连接,匹配网络电路103与qfn封装引脚连接,qfn封装引脚的射频发射引脚tx与qfn封装引脚的射频接收引脚rx通过第一电感l1连接。本实施例中的qfn封装结构与前述实施例相同或者近似,可以参考前述实施例中的qfn封装结构,因此,此处对qfn封装结构101不再赘述。qfn封装结构形成的寄生电容和寄生电感与qfn封装结构外部的匹配网络电路相结合,形成了多阶滤波电路,可以通过加大滤波电路的阶数,提高对谐波的抑制效果,从而降低谐波能量辐射强度。在qfn封装结构内,tx的绑定线设置在vss_rx的绑定线与vss_tx的绑定线之间,可以理解为tx的绑定线被二者包围。对于射频收发模组结构的qfn封装结构之外的走线,连接tx的走线设置在连接vss_rx的走线与连接vss_tx的走线之间,可以理解为连接tx的走线被二者包围,这样可以减小tx谐波对外的辐射,因为连接tx的走线被连接vss_rx的走线与连接vss_tx的走线包围以后,其能量更为集中,不会发散。

[0080]

基于上述实施例公开的内容,本实施例中,如图10所示,匹配网络电路103包括第一电容c1、第二电容c2、第三电容c3以及第二电感l2,其中,天线102与第一电容c1的第一端连接,第一电容c1的第二端分别连接至第二电容c 2的第一端与第二电感l2的第一端,第二电容c2的第二端接地,第二电感l2的第二端分别连接第三电容c3的第一端、qfn封装引脚的射频发射引脚以及第一电感l1,第三电容c3的第二端接地。本实施例中,qfn封装结构101外部的3元素匹配网络电路可以形成2阶低通滤波器,qfn封装结构形成的寄生电感和寄生电容也可以看成为二阶低通滤波器,因此,图10所示的射频收发模组结构整体形成4阶的低通滤波器,从而对高次谐波有更好的抑制效果。本实施例中,阶数越多,对谐波的抑制效果越好,但是阶数越多,插损也会越多,图10所示的形成4阶的低通滤波器可以在保证对谐波抑制效果的同时将插损控制在一定限度内。

[0081]

基于上述实施例公开的内容,本实施例提出另一种射频收发模组结构,如图11所示,包括qfn封装结构111、天线112和匹配网络电路113,天线112与匹配网络电路113连接,匹配网络电路103与qfn封装引脚的射频收发引脚trx连接。本实施例中的qfn封装结构与前述实施例相同或者近似,可以参考前述实施例中的qfn封装结构,本实施例中的qfn封装结构111中的射频发射引脚和射频接收引脚共用同一个射频收发引脚,此处对qfn封装结构111不再赘述。qfn封装结构形成的寄生电容和寄生电感与qfn封装结构外部的匹配网络电

路相结合,形成了多阶滤波电路,可以通过加大滤波电路的阶数,提高对谐波的抑制效果,从而降低谐波能量辐射强度。

[0082]

基于上述实施例公开的内容,本实施例中,如图11所示,匹配网络电路113包括第一电容c1、第二电容c2、第三电容c3以及第二电感l2,其中,天线112与第一电容c1的第一端连接,第一电容c1的第二端分别连接至第二电容c2的第一端与第二电感l2的第一端,第二电容c2的第二端接地,第二电感l2的第二端分别连接第三电容c3的第一端与qfn封装引脚的射频收发引脚,第三电容c3的第二端接地。本实施例中,qfn封装结构101外部的3元素匹配网络电路可以形成2阶低通滤波器,qfn封装结构形成的寄生电感和寄生电容也可以看成为二阶低通滤波器,因此,图11所示的射频收发模组结构整体形成4阶的低通滤波器,从而对高次谐波有更好的抑制效果。本实施例中,阶数越多,对谐波的抑制效果越好,但是阶数越多,插损也会越多,图11所示的形成4阶的低通滤波器可以在保证对谐波抑制效果的同时将插损控制在一定限度内。

[0083]

本实施例提供的电子设备包括前述实施例中的任意一种射频收发模组结构,还包括一个外壳,外壳还设置有屏幕,射频收发模组结构设置于所述外壳内。本技术实施例提供的qfn封装结构的具体实现方式及有益效果上述参见上述实施例,此处不再赘述。

[0084]

应理解,在本技术实施例中,“与a相应的b”表示b与a相关联,根据a可以确定b。但还应理解,根据a确定b并不意味着仅仅根据a确定b,还可以根据a和/或其它信息确定b。

[0085]

另外,本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。

[0086]

所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的系统、装置和单元的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

[0087]

在本技术所提供的几个实施例中,应该理解到,所揭露的系统、装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

[0088]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0089]

另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

[0090]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1