一种改善器件应力的扇出型封装结构和电子设备的制作方法

1.本实用新型涉及半导体封装领域,尤其涉及一种改善器件应力的扇出型封装结构和电子设备。

背景技术:

2.从晶圆代工厂、封装厂到ic设计公司和系统厂商,都开始将先进封装作为突破摩尔定律的一个方向。先进封装作为晶圆制造的后道工序,在持续压缩芯片体积、提高加工效率、提高设计效率和减少设计成本方面不断发挥重要作用。相比于传统封装,先进封装具有提升芯片功能密度、缩短互联长度和进行系统重构三大功能。这其中,rdl(re-distributed layer,重布线层)技术的运用功不可没。也正是这项技术的兴起,使得封装厂得以在扇出型封装技术上与晶圆厂一较高下。扇出型封装又分为扇出型晶圆级封装(fan-out wafer level packaging;fowlp),以及扇出型面板级封装(fan-out panel level packaging;foplp)。

3.其中,foplp顾名思义就是把已知合格芯片kgd重排在一个板级大小的载体上进行整体封装后再切割,因为板的尺寸比晶圆大,一次可以封装更多芯片,所以理论上产能和成本都更有优势。但是对应地,由于封装时尺寸过大以及材料间的热膨胀(cte)的不匹配,在封装工艺中,无法实现内部应力的平衡,最终导致注塑材料冷却过程中产生翘曲。

4.现有技术(申请号为cn202210407062.9的发明专利)公开了一种扇出型封装结构和扇出型封装结构的制备方法,涉及半导体封装技术领域,该扇出型封装结构包括缓冲层、芯片、塑封层、第一组合布线层和第一焊球,通过设置缓冲层,并将芯片贴附在缓冲层上,然后设置包覆在芯片外的塑封层,缓冲层的热膨胀系数小于塑封层的热膨胀系数,第一焊球与第一组合布线层电连接,第一组合布线层与芯片电连接,实现了扇出型封装。其在塑封层和第一组合布线层之间形成缓冲层,使得器件受力时缓冲层能够优先于塑封层变形,吸收塑封层产生的结构应力,防止变形。然而由于其仅在塑封层和第一组合布线层之间形成缓冲层,而在塑封层和芯片之间并未设置缓冲层,当芯片与塑封层之间由于热膨胀(cte)不匹配时会导致翘曲增大,同时影响可靠性。

5.因此,针对上述问题,提供一种改善器件应力的扇出型封装结构和电子设备,是本领域亟待解决的技术问题。

技术实现要素:

6.本实用新型的目的在于克服现有技术的不足,提供一种改善器件应力的扇出型封装结构和电子设备。

7.本实用新型的目的是通过以下技术方案来实现的:

8.本实用新型的第一方面,提供一种改善器件应力的扇出型封装结构,包括:

9.塑封层;

10.芯片,设置于所述塑封层内;

11.重布线子结构,位于所述塑封层正面和芯片正面的上方,与芯片正面电连接;

12.第一应力缓冲层,设置于塑封层正面与所述重布线子结构之间;

13.第二应力缓冲层,设置于芯片背面与塑封层之间。

14.进一步地,所述重布线子结构包括:

15.第一介质层,设置于第一塑封层和芯片上方,所述第一介质层上设置有通电通孔;

16.重布线层,设置于第一介质层上方,且通过所述通电通孔与所述芯片正面电连接;

17.外接焊球,设置于所述重布线层上方,且与所述重布线层连接。

18.进一步地,所述重布线子结构还包括:

19.第二介质层,位于所述第一介质层和所述重布线层上方,所述第二介质层上设置有焊球通孔。

20.进一步地,所述第一应力缓冲层和第二应力缓冲层均为聚酰亚胺缓冲层或pbo缓冲层。

21.进一步地,所述芯片正面高于所述塑封层正面第一高度;所述第一应力缓冲层的正面与所述芯片正面持平。

22.进一步地,所述第一应力缓冲层厚度与第二应力缓冲层厚度相同。

23.进一步地,所述塑封层上设置有若干均匀排布的芯片。

24.本实用新型的第二方面,提供一种电子设备,包括所述的改善器件应力的扇出型封装结构。

25.本实用新型的有益效果是:

26.(1)在本实用新型一示例性实施例中,第一应力缓冲层设置于塑封层正面与所述重布线子结构之间,从而使得器件受力时第一应力缓冲层能够优先于塑封层变形,吸收塑封层产生的结构应力,防止变形;同时,第二应力缓冲层设置于芯片背面与塑封层之间,改善封装中芯片与塑封层之间应力引起的翘曲和可靠性问题,即进一步改善器件受力,从而改善封装翘曲使得封装结构的翘曲值更低,从而改善封装可靠性。

27.(2)在本实用新型的又一示例性实施例中,公开了重布线子结构的具体实现方式,其中第一介质层起到芯片与上方电气器件的绝缘和机械保护作用,重布线层起着在xy平面电气延伸和互联的作用,外接焊球起到封装结构与外面电路和或系统的电和或信号连接作用。

28.(3)在本实用新型的又一示例性实施例中,第二介质层设置于第一介质层和重布线层上方,不仅起到重布线层的电气隔离和机械保护,还通过焊球通孔的设置实现了对外接焊球的支撑。

29.(4)在本实用新型的又一示例性实施例中,芯片正面高于所述塑封层正面第一高度;第一应力缓冲层的正面与所述芯片正面持平。采用该种方式设置,可以使得形成的封装结构具有较好的平整性,保证了封装结构的可靠性。

附图说明

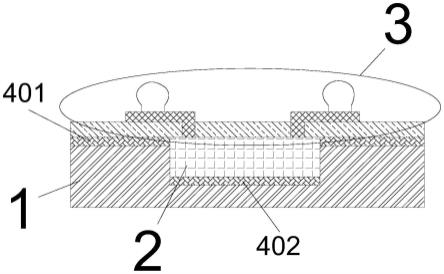

30.图1为本实用新型一示例性实施例中提供的一种改善器件应力的扇出型封装结构的示意图;

31.图2为本实用新型的一示例性实施例中提供的重布线子结构的示意图;

32.图3为本实用新型的又一示例性实施例中提供的重布线子结构的示意图;

33.图4为本实用新型的一示例性实施例中提供的一种改善器件应力的扇出型封装结构的制备流程示意图;

34.图5为本实用新型的又一示例性实施例中提供的一种改善器件应力的扇出型封装结构的制备流程示意图;

35.图6为本实用新型的又一示例性实施例中提供的一种改善器件应力的扇出型封装结构的制备流程示意图;

36.图7为本实用新型的又一示例性实施例中提供的一种改善器件应力的扇出型封装结构的制备流程示意图;

37.图8为本实用新型的又一示例性实施例中提供的一种改善器件应力的扇出型封装结构的制备流程示意图;

38.图中,1-塑封层,2-芯片,3-重布线子结构,301-第一介质层,30101-通电通孔,302-重布线层,303-外接焊球,304-第二介质层,30401-焊球通孔,401-第一应力缓冲层,402-第二应力缓冲层。

具体实施方式

39.下面结合附图对本实用新型的技术方案进行清楚、完整地描述,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

40.在本实用新型的描述中,需要说明的是,属于“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方向或位置关系为基于附图所述的方向或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

41.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,属于“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

42.在本技术使用的术语是仅仅出于描述特定实施例的目的,而非旨在限制本技术。在本技术和所附权利要求书中所使用的单数形式的“一种”、“所述”和“该”也旨在包括多数形式,除非上下文清楚地表示其他含义。还应当理解,本文中使用的术语“和/或”是指并包含一个或多个相关联的列出项目的任何或所有可能组合。

43.应当理解,尽管在本技术可能采用术语第一、第二、第三等来描述各种信息,但这些信息不应限于这些术语。这些术语仅用来将同一类型的信息彼此区分开。例如,在不脱离本技术范围的情况下,第一信息也可以被称为第二信息,类似地,第二信息也可以被称为第一信息。取决于语境,如在此所使用的词语“如果”可以被解释成为“在

……

时”或“当

……

时”或“响应于确定”。此外,属于“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。

44.此外,下面所描述的本实用新型不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

45.参见图1,图1示出了本实用新型一示例性实施例中提供的一种改善器件应力的扇出型封装结构,包括:

46.塑封层1;

47.芯片2,设置于所述塑封层1内;

48.重布线子结构3,位于所述塑封层1正面和芯片2正面的上方,与芯片2正面电连接;

49.第一应力缓冲层401,设置于塑封层1正面与所述重布线子结构3之间;

50.第二应力缓冲层402,设置于芯片2背面与塑封层1之间。

51.具体地,在本示例性实施例中,与现有技术相同的,第一应力缓冲层401设置于塑封层1正面与所述重布线子结构3之间,从而使得器件受力时第一应力缓冲层401能够优先于塑封层1变形,吸收塑封层1产生的结构应力,防止变形;而与现有技术不同的,第二应力缓冲层402设置于芯片2背面与塑封层1之间,封装中芯片2和塑封层1应力降低,进一步改善器件受力,从而改善封装翘曲使得封装结构的翘曲值更低,从而改善封装可靠性。

52.更优地,在一示例性实施例中,如图2所示,所述重布线子结构3包括:

53.第一介质层301,设置于第一塑封层1和芯片2上方,所述第一介质层301上设置有通电通孔30101;

54.重布线层302,设置于第一介质层301上方,且通过所述通电通孔30101与所述芯片2正面电连接;

55.外接焊球303,设置于所述重布线层302上方,且与所述重布线层302连接。

56.具体地,在本示例性实施例中,第一介质层301设置于第一塑封层1和芯片2上方,起到芯片2与上方电气器件的绝缘和机械保护作用,同时第一介质层301提供通电通孔30101,实现芯片2与上方期间的电连接。

57.重布线层302起着在xy平面电气延伸和互联的作用,原来设计的芯片2线路接点位置(i/o pad)通过布线制程改变其接点位置,使芯片2能适用于不同的封装形式;而在如图2所示的示例性实施例中,首先通过通电通孔30101在y平面进行电气延伸、之后在第一介质层301的x平面进行电器延伸,从而使得芯片2的接点延伸至第一介质层301上方。

58.外接焊球303设置于重布线层302的上方,起到本示例性实施例的封装结构与外面电路和或系统的电和或信号连接作用。

59.更优地,在一示例性实施例中,如图3所示,所述重布线子结构3还包括:

60.第二介质层304,位于所述第一介质层301和所述重布线层302上方,所述第二介质层304上设置有焊球通孔30401。

61.具体地,在该示例性实施例中,所述第二介质层设置于第一介质层301和所述重布线层302上方,不仅起到重布线层302的电气隔离和机械保护,还通过焊球通孔30401的设置实现了对外接焊球303的支撑。

62.更优地,在一示例性实施例中,所述第一应力缓冲层401和第二应力缓冲层402均为聚酰亚胺缓冲层或pbo缓冲层。

63.具体地,聚酰亚胺(polyimide,简写为pi)指主链上含有酰亚胺环的一类聚合物,是综合性能最佳的有机高分子材料之一。其耐高温达400℃以上,长期使用温度范围-200~

300℃,部分无明显熔点,高绝缘性能,103赫兹下介电常数4.0,介电损耗仅0.004~0.007,属f至h级绝缘。而聚对苯撑苯并双噁唑又称聚对苯撑苯并二噁唑,简称pbo,是一种液晶芳香族杂环聚合物,合成pbo的主要单体之一是4,6-二氨基间苯二酚。聚对苯撑苯并双噁唑聚合物采用空气间隙-湿法纺丝制成的聚对苯撑苯并双噁唑(pbo)纤维是一种高性能的芳香族聚酰胺纤维。聚对苯撑苯并双噁唑(pbo)纤维具有优良的力学性能、耐热性、难燃性能高,且具有耐冲击性、耐摩擦性和尺寸稳定性优异的特点。

64.聚酰亚胺缓冲层或pbo缓冲层的热膨胀系数小于塑封层1的热膨胀系数,使得器件受力时第一应力缓冲层401和第二应力缓冲层402能够优先于塑封层1变形,吸收塑封层1产生的结构应力,防止变形。

65.更优地,在一示例性实施例中,如图1~图3所示,所述芯片2正面高于所述塑封层1正面第一高度;所述第一应力缓冲层401的正面与所述芯片2正面持平。

66.具体地,在该示例性实施例中,采用该种方式设置,可以使得形成的封装结构具有较好的平整性,保证了封装结构的可靠性。

67.更优地,在一示例性实施例中,所述第一应力缓冲层401厚度与第二应力缓冲层402厚度相同。

68.而当为了实现上述该技术手段,可以采用如下的制备方式:

69.首先,如图4所示,将芯片2贴装在基板5上,芯片2背面朝上;之后如图5所示,在芯片2背面上部以及两侧(基板5上部)沉积应力缓冲层,其中沉积于芯片2背面上的为第二应力缓冲层402,沉积于基板5上的为第一应力缓冲层401;再之后,如图6所示,在第二应力缓冲层402和第一应力缓冲层401上进行第一塑封层1的制作;之后,如图7所示,去除基板5;最后,完成重布线子结构3的制作,得到如图1~如图3所示的示例性实施例的结构。

70.其中,重布线子结构3的制作,可以如图8所示,先制作其中一实例性实施例中公开的第一介质层301、通电通孔30101和重布线层302;然后再制作外接焊球303和第二介质层304(若有)。

71.由上可知,增加第二应力缓冲层402并不会增加额外制作流程,并且相较于现有技术中采用蚀刻的方式(需要精准掌控),上述方式仅为沉积,降低工艺难度l。并且,通过沉积应力缓冲层的方式,使得第一应力缓冲层401厚度与第二应力缓冲层402厚度相同。

72.更优地,在一示例性实施例中,所述塑封层1上设置有若干均匀排布的芯片2。

73.本实用新型的第二方面,提供一种电子设备,包括所述的改善器件应力的扇出型封装结构。

74.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其他不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本实用新型创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1