防辐射粘接胶组件、封装芯片、电子装置及电子设备的制作方法

本技术涉及半导体,特别涉及一种防辐射粘接胶组件、封装芯片、电子装置及电子设备。

背景技术:

1、随着存储芯片朝向大容量发展,会给容量的增加带来收益,使得存储芯片内的一个存储单元内可存储更多的有效数据,这对存储芯片的数据可靠性要求极高。

2、目前,存储芯片中具有多个存储数据的裸芯片,每个裸芯片中具有多个存储颗粒,存储颗粒作为裸芯片中最小的存储数据的存储单元。大容量的存储单元,对存储芯片朝向大容量发展起中重要的作用,但是对存储单元的稳定性要求更高。当辐射作用在存储单元上时,会使得存储单元内的遂穿层的空洞缺陷增加,导致电荷容易丢失,引起数据失效。为此,相关技术中,提出对存储芯片中的多个裸芯片进行封装级防护,通过封装级防护将各裸芯片从外部整体包裹,以实现对各裸芯片的辐射防护。然而,这种防护方式,会导致存储芯片的封装尺寸过大,在电子装置上无法应用。

3、因此,如何在提升存储芯片的防辐射性能的同时,不会对存储芯片的封装尺寸造成过大的影响,已成为有待解决的技术问题。

技术实现思路

1、本技术提供了一种防辐射粘接胶组件、封装芯片、电子装置及电子设备,通过防辐射粘接胶组件的设置,在提升封装芯片的防辐射性能的基础上,还能够简化封装芯片的防护工艺,有助于封装芯片的小型化。

2、本技术实施例第一方面提供了一种防辐射粘接胶组件,应用于封装芯片的裸芯片,防辐射粘接胶组件包括第一粘接层、防辐射金属层和第二粘接层,第一粘接层被构造为粘接于裸芯片的具有功能区的一面;第二粘接层被构造为粘接于封装芯片中的遮挡物,其中,遮挡物与裸芯片相对设置,防辐射金属层连接于第一粘接层和第二粘接层之间,并遮挡功能区。

3、本技术通过防辐射粘接胶组件中第一粘接层和第二粘接层的设置,能够利用封装芯片现有的裸芯片的粘接工艺,将封装芯片中的裸芯片与遮挡物粘接。并且,通过防辐射粘接胶组件中防辐射金属层的设置,由于防辐射金属层连接于第一粘接层和第二粘接层之间,且第一粘接层粘接于裸芯片具有功能区的一面,并遮挡功能区,这样在裸芯片与遮挡物通过封装芯片中现有的粘接工艺粘接的同时,还能够通过防辐射金属层遮挡功能区,从而对裸芯片进行辐射防护,提升封装芯片的防辐射性能,简化封装芯片的防护工艺的同时,还能够避免对封装芯片的封装尺寸造成过大影响,有利于封装芯片的小型化。

4、在一些可选的实施方式中,第一粘接层的周侧边缘均粘接于裸芯片,且第一粘接层的覆盖范围大于功能区,以确保第一粘接层完整遮挡于功能区,有利于实现防辐射金属层对功能区的完全遮挡,提升裸芯片以及封装芯片的防辐射性能。

5、在一些可选的实施方式中,第一粘接层的形状与功能区的形状相适配,防辐射金属层的形状与第一粘接层的形状相适配,并遮挡功能区,以确保防辐射金属层能够完全遮挡在功能区,提升裸芯片以及封装芯片的防辐射性能。

6、在一些可选的实施方式中,第二粘接层的形状与防辐射金属层的形状相适配,以便防辐射金属层能够通过第二粘接层完全粘接于封装芯片中,增强防辐射粘接胶组件在封装芯片中的粘接效果。

7、在一些可选的实施方式中,防辐射金属层为钨层或者钨合金层,以便利用钨或者钨合金所具有的较好的防辐射性能的同时,由于钨和钨合金为无毒的环保材料,因此还能够增强防辐射粘接胶组件以及封装芯片的环保性能。

8、在一些可选的实施方式中,第一粘接层的厚度大于或者等于5um,且小于或者等于10um;第二粘接层的厚度大于或者等于5um,且小于或者等于10um;防辐射金属层的厚度大于或者等于5um,且小于或者等于20um。

9、这样通过对第一粘接层、第二粘接层和防辐射金属层的厚度进行限定,在确保提升封装芯片的防辐射性能的同时,能够避免防辐射粘接胶组件对封装芯片的封装厚度造成过大影响。

10、在一些可选的实施方式中,防辐射粘接胶组件还包括第一绝缘层,第一绝缘层连接于防辐射金属层与第一粘接层之间,以阻隔封装芯片的键合线与防辐射金属层接触;

11、第一粘接层内设置有封装芯片的键合线,键合线被构造为将裸芯片与封装芯片中的基板导通。

12、这样通过第一绝缘层的设置,由于第一绝缘层连接于防辐射金属层与第一粘接层之间,且第一粘接层内设置有键合线,能够通过第一绝缘层阻隔键合线与防辐射金属层接触,以避免键合线短路。

13、在一些可选的实施方式中,第一绝缘层覆盖于防辐射金属层朝向第一粘接层的一面,以便通过第一绝缘层能够遮挡在防辐射金属层朝向第一粘接层的一面,增强第一绝缘层对键合线的阻隔性能。第一绝缘层的形状与防辐射金属层的形状相适配,以便通过第一绝缘层实现对防辐射金属层的完全覆盖和遮挡。

14、在一些可选的实施方式中,防辐射粘接胶组件还包括第二绝缘层,第二绝缘层连接于防辐射金属层与第二粘接层之间,以覆盖防辐射金属层朝向第二粘接层的一面。

15、这样通过第二绝缘层的设置,能够简化防辐射粘接胶组件在封装芯片的晶圆上的贴合。

16、在一些可选的实施方式中,防辐射粘接胶组件还包括保护膜,保护膜连接并覆盖于第一粘接层和第二粘接层,以便通过保护膜实现对第一粘接层和第二粘接层的防污保护。

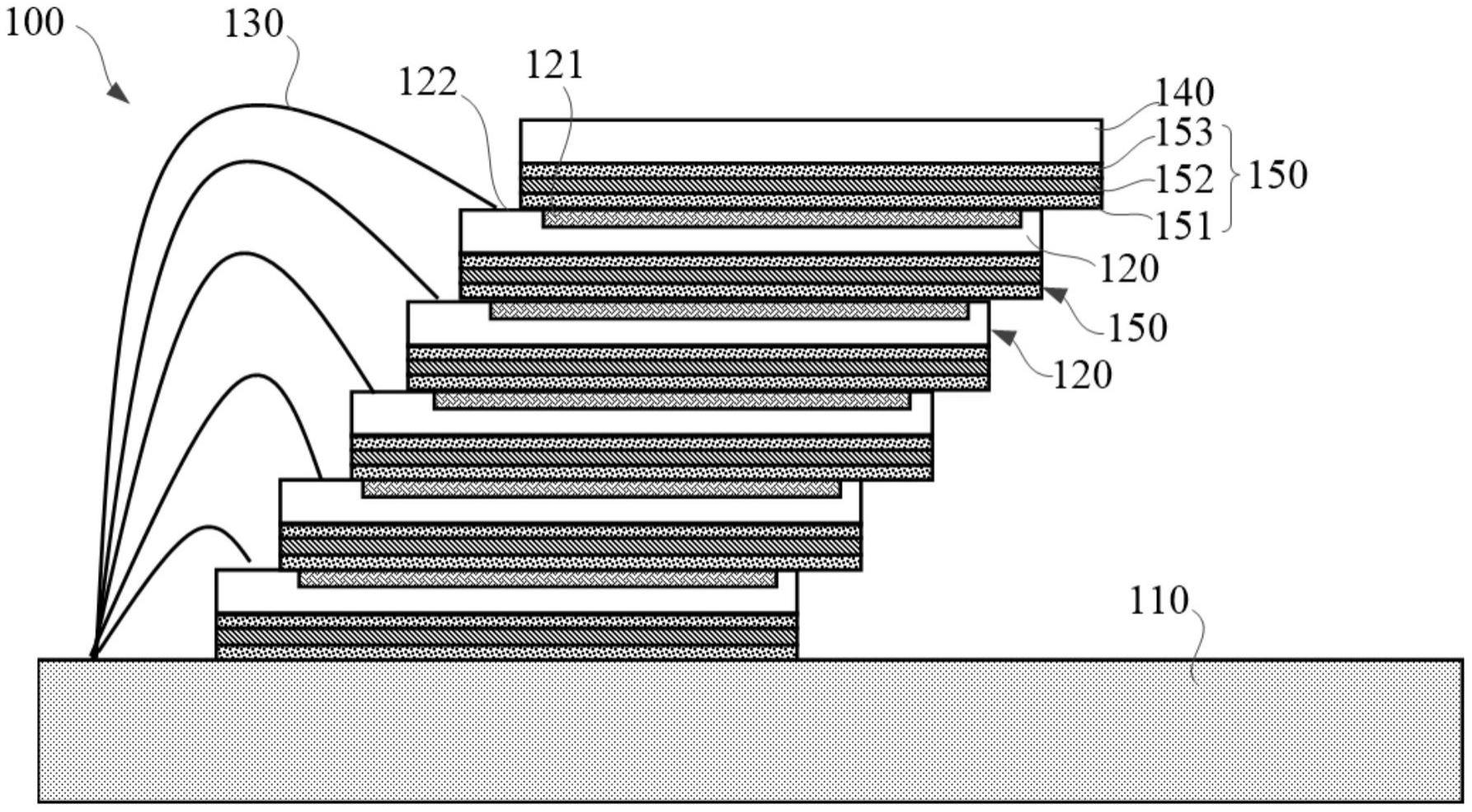

17、本技术实施例第二方面提供了一种封装芯片,该封装芯片包括基板、裸芯片组件和至少一个如上任一项的防辐射粘接胶组件,裸芯片组件包括至少一个裸芯片;

18、防辐射粘接胶组件连接于裸芯片和遮挡物之间,并遮挡裸芯片的功能区。

19、这样通过封装芯片中防辐射粘接胶组件的设置,由于防辐射粘接胶组件连接于裸芯片和遮挡物之间,并遮挡功能区,以便实现对裸芯片的功能区的辐射防护,提升封装芯片的防辐射性能,简化封装芯片的防护工艺的同时,还能够避免对封装芯片的封装造成影响,有利于封装芯片的小型化。

20、在一些可选的实施方式中,防辐射粘接胶组件的第一粘接层连接于裸芯片,防辐射粘接胶组件的第二粘接层连接于遮挡物,遮挡物与裸芯片的功能区相对设置,以便在实现裸芯片和遮挡物连接的同时,能够通过遮挡物实现防辐射粘接胶组件在封装芯片内固定。

21、在一些可选的实施方式中,裸芯片组件包括至少两个依次叠设于基板的板面上的裸芯片,各裸芯片的功能区均朝向远离基板的一侧设置;

22、防辐射粘接胶组件的第一粘接层连接于至少两个裸芯片中的一者上,遮挡物为遮挡件或者封装芯片中的其它裸芯片。

23、这样当遮挡物为遮挡件时,能够通过遮挡件所连接的防辐射粘接胶组件实现对裸芯片组件的表层的裸芯片的辐射防护,在遮挡物为封装芯片中的其它裸芯片时,能够通过与封装芯片中的其它裸芯片连接的防辐射胶,实现对裸芯片组件内与其它裸芯片相邻的裸芯片的辐射防护。

24、在一些可选的实施方式中,裸芯片为具有功能区的辐射敏感裸芯片,遮挡件为金属片、非功能裸芯片或者非辐射敏感裸芯片。

25、这样通过防辐射粘接胶组件设置,在提升对裸芯片的功能区的防辐射性能的同时,还能够实现裸芯片与遮挡件的连接。由于遮挡件为金属片、非功能裸芯片或者非辐射敏感裸芯片,还能够避免辐射对遮挡物的性能造成影响,实现对裸芯片组件的表层的裸芯片的辐射防护。

26、在一些可选的实施方式中,所述遮挡物为所述封装芯片中的其它所述裸芯片时,第一粘接层粘接于其中一个裸芯片的具有功能区的一面,第二粘接层粘接于相邻的裸芯片朝向基板的一面;

27、防辐射粘接胶组件的防辐射金属层粘接于第一粘接层和第二粘接层之间,以遮挡第一粘接层所连接的裸芯片的功能区。

28、这样通过防辐射粘接胶组件连接相邻两个裸芯片的同时,能够实现对朝向基板一侧的裸芯片的辐射防护,以提升封装芯片在厚度方向上的防辐射性能。

29、在一些可选的实施方式中,裸芯片背离基板的一面还具有布设键合线的键合区,键合区位于功能区的侧方;

30、键合线的一端连接基板,另一端在键合区朝向背离基板的一侧弯折后,连接于裸芯片。

31、这样通过键合线的设置,能够将裸芯片与基板导通。

32、在一些可选的实施方式中,沿基板到遮挡件的方向上,上方的裸芯片堆叠在下方的裸芯片的一侧,并覆盖于下方的裸芯片的功能区,键合线位于防辐射粘接胶组件之外。

33、这样通过防辐射粘接胶组件在连接相邻两个裸芯片的同时,能够杜绝键合线与防辐射粘接胶组件中的防辐射金属层接触短路。

34、在一些可选的实施方式中,沿基板到遮挡件的方向上,上方的裸芯片覆盖于下方的裸芯片的功能区和键合区,键合线的端部设置于对应的第一粘接层内。

35、这样在通过防辐射粘接胶组件提升封装芯片的防辐射性能的同时,还能够使得裸芯片组件的堆叠方式更加多样化。

36、在一些可选的实施方式中,防辐射粘接胶组件还包括第一绝缘层,第一绝缘层连接于防辐射金属层和第一粘接层之间,并覆盖防辐射金属层。

37、这样通过第一绝缘层的设置,能够阻隔键合线与防辐射金属层接触,以避免键合线短路。

38、在一些可选的实施方式中,防辐射粘接胶组件还包括第二绝缘层,第二绝缘层连接于防辐射金属层和第二粘接层之间,并覆盖防辐射金属层。

39、这样通过第二绝缘层的设置,能够简化防辐射粘接胶组件在封装芯片的晶圆上的贴合。

40、在一些可选的实施方式中,防辐射粘接胶组件连接于裸芯片组件和基板之间,以便在实现裸芯片组件与基板连接的同时,还能够增强裸芯片组件中底层的裸芯片的防辐射性能。

41、在一些可选的实施方式中,裸芯片还包括防辐射填充物,裸芯片在功能区的外围具有至少一个防护槽,防辐射填充物填充于防护槽内。

42、这样通过防护槽的设置,在实现防辐射填充物在裸芯片上固定的同时,还能够实现对裸芯片在功能区的外围的防护,以确保实现对裸芯片的全方位防护。

43、在一些可选的实施方式中,防护槽包括第一防护槽,第一防护槽的槽深大于或者等于功能区的深度,以增强防辐射填充物对裸芯片在功能区的外围的防护性能。

44、在一些可选的实施方式中,防护槽还包括第二防护槽,第二防护槽与第一防护槽呈夹角设置,并相互连通,以便进一步增强防辐射填充物对裸芯片在功能区的外围的防护性能的同时,还能够改变裸芯片在拆装时的应力分布。

45、在一些可选的实施方式中,封装芯片为存储芯片或者逻辑芯片,以便提升对存储芯片或者逻辑芯片的防辐射性能,增强存储芯片或者逻辑芯片的可靠性和稳定性。

46、本技术实施例第三方面提供了一种电子装置,该电子装置包括控制器和如上任一项的封装芯片,封装芯片与控制器电连接。

47、本技术通过电子装置中上述封装芯片的设置,使得电子装置中的封装芯片不仅具有较好的防辐射性能,有利于增强电子装置的可靠性和稳定性,而且具有较简单的防护工艺,有利于电子装置的小型化。

48、本技术实施例第四方面提供了一种电子设备,电子设备包括处理器和如上的电子装置,电子装置与处理器电连接。

49、这样能够便于通过处理器对电子装置进行控制的同时,不仅能够提升电子装置的防辐射性能,有利于增强电子装置的可靠性和稳定性,而且有利于电子装置以及电子设备的小型化。

- 还没有人留言评论。精彩留言会获得点赞!