具有用于平衡接通/关断行为的不对称集成集总栅极电阻器和/或用于改善功率处置的多个间隔开的集总栅极电阻器的半导体器件的制作方法

本发明涉及半导体器件,更特别地,涉及具有集总栅极电阻器的半导体器件。

背景技术:

1、本领域已知多种功率半导体器件,包括例如功率金属氧化物半导体场效应晶体管(“mosfet”)、绝缘栅双极晶体管(“igbt”)和各种其它器件。这些功率半导体器件常常由宽带隙半导体材料制成,诸如碳化硅或氮化镓基材料,在本文中,术语“宽带隙半导体”涵盖具有至少1.4ev的带隙的任何半导体。功率半导体器件被设计为选择性地阻止或通过大电压和/或电流。例如,在阻断状态下,功率半导体器件可以被设计为维持数百或数千伏的电势。

2、诸如功率mosfet的功率半导体器件可以具有横向结构或垂直结构。具有横向结构的功率mosfet在器件的半导体层结构的同一主表面(即,上部或下部)上具有mosfet的源极区和漏极区。作为对照,具有垂直结构的功率mosfet在其半导体层结构的一个主表面上具有其源极区,并且在其另一个(相对的)主表面上具有其漏极区。垂直器件结构通常用于非常高功率的应用,因为垂直结构允许厚的半导体漂移层,该漂移层可以支持高电流密度并阻止高电压。在本文中,术语“半导体层结构”是指包括其中形成p-n结的一个或多个半导体层的结构。半导体层结构通常包括其上形成有多个半导体外延层的半导体基板。宽带隙半导体层结构是指其中p-n结形成在一种或多种宽带隙半导体材料中的半导体层结构。

3、常规的垂直碳化硅功率mosfet包括形成在碳化硅基板(诸如碳化硅晶片)上的碳化硅漂移区。具有与漂移区相反的导电类型的所谓“阱”区形成在漂移区的上部中,并且具有与漂移区相同的导电类型的碳化硅源极区形成在阱区内。碳化硅基板、碳化硅漂移区、碳化硅阱区和碳化硅源极区形成功率mosfet的半导体层结构。栅极指形成在半导体层结构中或半导体层结构上以形成单独的单位单元晶体管。

4、单位单元晶体管形成在mosfet的所谓“有源区”中。mosfet还包括一个或多个无源区,诸如可以围绕有源区和/或栅极接合衬垫区的终端区。有源区充当主结,用于在反向偏置操作期间阻挡电压并在正向偏置操作期间提供电流。功率mosfet通常具有单位单元(unit cell)结构,意味着有源区包括大量单独的“单位单元”mosfet,这些mosfet并联电连接以用作单个功率mosfet。在高功率应用中,这样的器件可以包括数千或数万个单位单元。

5、许多功率半导体器件,诸如功率mosfet和igbt,都具有栅极结构。这些器件可以通过向其栅极结构施加不同的偏置电压来导通和截止。栅极结构具有分布式栅极电阻,它是从栅极接合衬垫(或其它栅极端子)到每个单独单位单元的栅极指的电路径长度以及形成栅极结构的材料的薄层电阻的函数。栅极结构可以包括例如栅极接合衬垫、器件的有源区中的多个栅极指、栅极衬垫,以及在栅极衬垫与栅极指之间延伸的一个或多个栅极总线。在许多应用中,可能期望通过例如在栅极结构内添加一个或多个分立或“集总”栅极电阻器来增加栅极电阻的量。增加的栅极电阻可以例如用于限制器件的开关速度或减少可以生成会导致器件发生故障的振动的电振铃和/或噪声。

技术实现思路

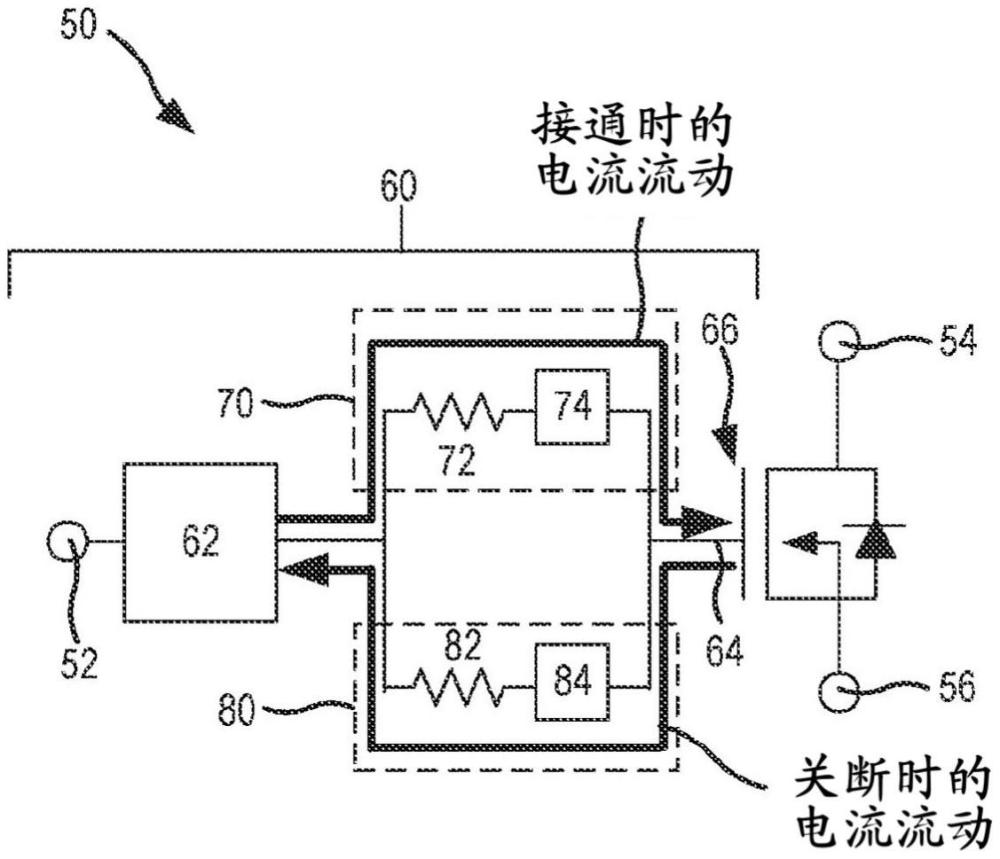

1、根据本发明的实施例,提供了包括栅极衬垫、多个栅极指以及耦合在栅极衬垫与栅极指之间的第一栅极电阻器和第一开关的半导体器件。

2、在一些实施例中,第一开关可以是二极管。在一些实施例中,二极管可以在第一栅极电阻器内实现。

3、在一些实施例中,半导体器件还包括耦合在栅极衬垫与栅极指之间的第二栅极电阻器和第二开关,诸如二极管。第一二极管在正向偏置时允许电流从栅极衬垫流向栅极指,并且第二二极管在正向偏置时允许电流从栅极指流向栅极衬垫。

4、半导体器件可以对于从栅极衬垫流向栅极指的栅极电流具有第一总栅极电阻值,并且可以对于从栅极指流向栅极衬垫的栅极电流具有第二总栅极电阻值,其中第二总栅极电阻值与第一总栅极电阻值不同。

5、第一栅极电阻器可以包括形成第一二极管的第一区段和第二区段,其中第一区段包括n型半导体材料并且第二区段包括p型半导体材料。在一些实施例中,第一栅极电阻器还包括第三区段,第三区段包括p型半导体材料,其中第一区段位于第二区段和第三区段之间。在一些实施例中,第二栅极电阻器包括第四区段、第五区段和第六区段,第四区段包括n型半导体材料,并且第五和第六区段包括p型半导体材料,其中第四区段介于第五与第六区段之间,并且其中第四区段和第六区段形成第二二极管。在一些实施例中,第二区段比第三区段更靠近栅极衬垫,并且第五区段比第六区段更靠近栅极衬垫。在一些实施例中,半导体器件还包括将第一区段短路到第三区段的第一金属连接器以及将第四区段短路到第五区段的第二金属连接器。

6、在一些实施例中,第一栅极电阻器包括n型半导体材料的第一区段和p型半导体材料的第二区段,其中第一区段可以直接接触第二区段。第一栅极电阻器还可以包括p型半导体材料的第三区段,其中第一区段位于第二区段与第三区段之间。n型半导体材料可以是n型多晶硅并且p型半导体材料可以是p型多晶硅。半导体器件还可以包括将第一区段短路到第三区段的金属连接器。金属连接器可以包括延伸穿过在第一栅极电阻器的上表面上形成的电介质层的通孔中的金属化部。

7、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、多个栅极指以及电插入在栅极衬垫与栅极指之间的栅极电阻器,其中栅极电阻器包括n型半导体材料的第一区段和p型半导体材料的第二区段。

8、在一些实施例中,第一区段可以直接接触第二区段。

9、在一些实施例中,n型半导体材料包括n型多晶硅并且p型半导体材料包括p型多晶硅。

10、在一些实施例中,栅极电阻器还包括p型半导体材料的第三区段,其中第一区段位于第二区段和第三区段之间。

11、在一些实施例中,半导体器件还包括将第一区段短路到第二区段的金属连接器。金属连接器可以包括延伸穿过在栅极电阻器的上表面上形成的电介质层的通孔中的金属化部。

12、在一些实施例中,n型半导体材料和p型半导体材料在栅极电阻器内形成二极管。

13、在一些实施例中,栅极电阻器是第一栅极电阻器,并且第一区段和第二区段之间的结形成第一二极管,半导体器件还包括与第一栅极电阻器和第一二极管并联电耦合的第二栅极电阻器和第二二极管。

14、在一些实施例中,第一二极管在正向偏置时被配置为允许电流从栅极衬垫流到栅极指,并且第二二极管在正向偏置时被配置为允许电流从栅极指流到栅极衬垫。

15、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、多个栅极指,以及电插入在栅极衬垫与栅极指之间的第一栅极电阻器和第一电路元件。第一电路元件被配置为在栅极衬垫与栅极指之间仅在第一方向上传导电流。

16、在一些实施例中,第一电路元件包括第一二极管。在一些实施例中,第一二极管在第一栅极电阻器内实现。

17、在一些实施例中,半导体器件还包括电插入在栅极衬垫与栅极指之间的第二栅极电阻器和第二二极管,其中第二二极管被配置为在栅极衬垫与栅极指之间仅在第二方向上传导电流,第二方向与第一方向相反。在一些实施例中,第二二极管在第二栅极电阻器内实现。

18、在一些实施例中,第一栅极电阻器包括n型半导体材料的第一区段和p型半导体材料的第二区段。

19、在一些实施例中,半导体器件还包括第一金属连接器,其将第一栅极电阻器的第一区段短路到第一栅极电阻器的第二区段。在一些实施例中,金属连接器包括延伸通过形成在第一栅极电阻器的上表面上的电介质层的通孔中的金属化部。

20、在一些实施例中,第一栅极电阻器的第一区段直接接触第一栅极电阻器的第二区段,并且n型半导体材料包括n型多晶硅并且p型半导体材料包括p型多晶硅。

21、在一些实施例中,半导体器件还包括宽带隙半导体层结构,并且第一栅极电阻器位于宽带隙半导体层结构的上侧。

22、在一些实施例中,半导体器件还包括直接位于第一栅极电阻器的上侧上的内部电介质图案。

23、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、栅极总线以及电插入在栅极衬垫与栅极总线之间的栅极电阻器结构,该栅极电阻器结构具有相对于从栅极衬垫流向栅极总线的电流的第一电阻以及相对于从栅极总线流向栅极衬垫的电流的第二电阻,第一电阻与第二电阻不同。

24、在一些实施例中,半导体器件还包括宽带隙半导体层结构,宽带隙半导体层结构包括具有多个单位单元晶体管的有源区域,并且栅极电阻器结构位于宽带隙半导体层结构的上侧。

25、在一些实施例中,半导体器件还包括直接位于栅极电阻器的上侧上的内部电介质图案。

26、在一些实施例中,栅极电阻器结构包括多个第一栅极电阻器、多个第一开关、多个第二栅极电阻器以及多个第二开关。

27、在一些实施例中,每个第一栅极电阻器和相应的一个第一开关耦合在栅极衬垫与栅极指之间,并且每个第二栅极电阻器和相应的一个第二开关耦合在栅极衬垫与栅极指之间。

28、在一些实施例中,每个第一开关包括第一二极管,并且每个第二开关包括第二二极管。

29、在一些实施例中,每个第一二极管在相应的一个第一栅极电阻器内实现,并且每个第二二极管在相应的一个第二栅极电阻器内实现。

30、在一些实施例中,第一二极管在正向偏置时被配置为允许电流从栅极衬垫流向栅极总线,并且第二二极管在正向偏置时被配置为允许电流从栅极总线流向栅极衬垫。

31、在一些实施例中,第一栅极电阻器的数量与第二栅极电阻器的数量不同。

32、在一些实施例中,每个第一栅极电阻器与至少一个第二栅极电阻器直接相邻。

33、在一些实施例中,每个第一栅极电阻器和每个第二栅极电阻器包括形成n-p-n结的n型半导体材料的第一区段、p型半导体材料的第二区段和p型半导体材料的第三区段。

34、在一些实施例中,半导体器件还包括多个第一金属连接器和多个第二金属连接器,每个第一金属连接器将相应的一个第一栅极电阻器的第一区段短路到相应的第一栅极电阻器的第三区段,每个第二金属连接器将相应的一个第二栅极电阻器的第一区段短路到相应的第二栅极电阻器的第二区段。

35、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、多个栅极指以及电插入在栅极衬垫与栅极指之间的栅极电阻器结构,该栅极电阻器结构在器件导通期间具有第一电阻并且在器件关断期间具有第二电阻,第一电阻与第二电阻不同。

36、在一些实施例中,半导体器件还包括宽带隙半导体层结构,该宽带隙半导体层结构包括有源区域,并且栅极电阻器结构位于宽带隙半导体层结构的上侧。

37、在一些实施例中,半导体器件还包括直接位于栅极电阻器结构的上侧上的内部金属电介质图案。

38、在一些实施例中,栅极电阻器结构包括形成耦合在栅极衬垫与栅极指之间的第一电路的第一栅极电阻器和第一开关,以及形成耦合在栅极衬垫与栅极指之间的第二电路的第二栅极电阻器和第二开关。

39、在一些实施例中,第一开关包括当正向偏置时允许电流从栅极衬垫流向栅极指的第一二极管,并且第二开关包括当正向偏置时允许电流从栅极指流向栅极衬垫的第二二极管。

40、在一些实施例中,栅极电阻器结构包括多个第一栅极电阻器电路以及多个第二栅极电阻器电路,每个第一栅极电阻器电路包括耦合在栅极衬垫与栅极指之间的第一栅极电阻器和第一开关,每个第二栅极电阻器包括耦合在栅极衬垫与栅极指之间的第二栅极电阻器和第二开关,其中所有第一栅极电阻器电路和所有第二栅极电阻器电路彼此并联电布置。

41、在一些实施例中,所有第一栅极电阻器的组合电阻与所有第二栅极电阻器的组合电阻不同。

42、在一些实施例中,第一栅极电阻器的数量与第二栅极电阻器的数量不同。

43、在一些实施例中,每个第一栅极电阻器与至少一个第二栅极电阻器直接相邻。

44、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、多个栅极指、电插入在栅极衬垫与栅极指之间的多个第一栅极电阻器,以及电插入在栅极衬垫与栅极指之间的多个第二栅极电阻器。在器件接通期间,在栅极衬垫与栅极指之间流动的栅极电流至少主要流过第一栅极电阻器,并且在器件关断期间,栅极电流至少主要流过第二栅极电阻器。

45、在一些实施例中,半导体器件还包括被配置为控制流过第一栅极电阻器的电流的多个第一二极管,其中第一二极管被配置为仅将电流从栅极衬垫传导到栅极指。半导体器件还可以包括被配置为控制流过第二栅极电阻器的电流的多个第二二极管,其中第二二极管被配置为仅将电流从栅极指传导到栅极衬垫。

46、在一些实施例中,第二栅极电阻器的总电阻与第一栅极电阻器的总电阻相差至少10%。

47、在一些实施例中,每个第一二极管是相应的一个第一栅极电阻器的一部分。

48、在一些实施例中,第一栅极电阻器的数量与第二栅极电阻器的数量不同。

49、在一些实施例中,第一栅极电阻器中的第一个的第一电阻与第二栅极电阻器中的第一个的第二电阻不同。

50、在一些实施例中,每个第一栅极电阻器与至少一个第二栅极电阻器直接相邻。

51、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、栅极总线、具有直接连接到金属栅极衬垫的第一端和直接连接到栅极总线的第二端的第一栅极电阻器,以及将第一栅极电阻器的第一内部部分电连接到栅极电阻器的第二内部部分的金属连接器。

52、在一些实施例中,半导体器件还包括集成在第一栅极电阻器内的第一二极管。

53、在一些实施例中,半导体器件还包括耦合在金属栅极衬垫与栅极总线之间的第二栅极电阻器和第二二极管。

54、在一些实施例中,第一二极管被配置为使得当其正向偏置时其允许电流从金属栅极衬垫流向栅极总线,并且第二二极管被配置为使得当其正向偏置时其允许电流从栅极总线流向金属栅极衬垫。

55、在一些实施例中,半导体器件在金属栅极衬垫与栅极总线之间具有用于从金属栅极衬垫行进到栅极总线的信号的第一电阻,并且在金属栅极衬垫与栅极总线之间具有用于从栅极总线行进到金属栅极衬垫的信号的第二电阻,第二电阻与第一电阻不同。

56、在一些实施例中,第一栅极电阻器和第二栅极电阻器各自包括n型半导体材料的第一区段和p型半导体材料的第二区段。

57、在一些实施例中,金属连接器包括延伸通过在第一栅极电阻器的上表面上形成的电介质层的通孔中的金属化部。

58、根据本发明的进一步实施例,提供了半导体器件,其包括栅极衬垫、多个栅极指、位于栅极衬垫与栅极指之间在器件接通期间但不在器件关断期间传导电流的第一导电路径,以及位于栅极衬垫与栅极指之间在器件关断期间传导电流但不在器件接通期间传导电流的第二导电路径。

59、在一些实施例中,第一导电路径包括彼此电并联部署的多个第一栅极电阻器电路,并且第二导电路径包括彼此电并联部署的多个第二栅极电阻器电路。

60、在一些实施例中,每个第一栅极电阻器电路包括第一栅极电阻器和第一二极管,并且每个第二栅极电阻器电路包括第二栅极电阻器和第二二极管。

61、在一些实施例中,第一栅极电阻器的数量与第二栅极电阻器的数量不同。

62、在一些实施例中,第一栅极电阻器中的至少一个的第一电阻与第二栅极电阻器中的至少一个的第二电阻不同。

63、在一些实施例中,每个第一栅极电阻器与至少一个第二栅极电阻器直接相邻。

64、根据本发明的进一步实施例,提供了半导体器件,其包括宽带隙半导体层结构、宽带隙半导体层结构上的栅极衬垫、宽带隙半导体层结构上的多个栅极指,以及电耦合在栅极衬垫与栅极指之间的多个集总栅极电阻器。

65、在一些实施例中,半导体器件还可以包括栅极总线,并且每个集总栅极电阻器可以连接在栅极衬垫与栅极总线之间。

66、在一些实施例中,集总栅极电阻器中的至少两个从栅极衬垫的侧边缘朝外延伸以接触沿着半导体器件的第一外边缘延伸的栅极总线的一部分。

67、在一些实施例中,集总栅极电阻器的第一子集从栅极衬垫的第一侧朝外延伸,并且多个集总栅极电阻器的第二子集从栅极衬垫的第二侧朝外延伸。在一些实施例中,多个集总栅极电阻器的第三子集从栅极衬垫的第三侧朝外延伸,第三侧与第一侧相对。在一些实施例中,多个集总栅极电阻器的第四子集从栅极衬垫的第四侧朝外延伸,第四侧与第二侧相对。

68、在一些实施例中,当在平面图中观看半导体器件时,多个集总栅极电阻器中的至少相应的一个集总栅极电阻器从栅极衬垫的每一侧(each and every side)朝外延伸。在一些实施例中,当在平面图中观看半导体器件时,集总栅极电阻器从栅极衬垫朝外延伸并且基本上包围栅极衬垫。

69、在一些实施例中,多个集总栅极电阻器可以包括第一集总栅极电阻器、第二集总栅极电阻器和第三集总栅极电阻器,它们各自从栅极衬垫延伸,其中第二集总栅极电阻器与第一集总栅极电阻器和第三集总栅极电阻器直接相邻并位于第一集总栅极电阻器与第三集总栅极电阻器之间。第二集总栅极电阻器的宽度可以小于第一集总栅极电阻器与第二集总栅极电阻器之间的第一距离,并且第二集总栅极电阻器的宽度还可以小于第二集总栅极电阻器与第三集总栅极电阻器之间的第二距离。

70、在一些实施例中,第一距离可以大于第二集总栅极电阻器的宽度的两倍,并且第二距离可以大于第二集总栅极电阻器的宽度的两倍。在其它实施例中,第一距离可以大于第二集总栅极电阻器的宽度的三倍,并且第二距离可以大于第二集总栅极电阻器的宽度的三倍。

71、在一些实施例中,第二集总栅极电阻器的长度可以是第二集总栅极电阻器的宽度的至少两倍。在一些实施例中,第二集总栅极电阻器的长度小于第二集总栅极电阻器的宽度的五倍。在一些实施例中,第二集总栅极电阻器的长度小于第二集总栅极电阻器的宽度。在一些实施例中,多个集总栅极电阻器中的每个集总栅极电阻器具有小于相应集总栅极电阻器的宽度的三倍的相应长度。

72、在一些实施例中,集总栅极电阻器可以彼此间隔开,使得在半导体器件的正常操作期间在相邻的集总栅极电阻器对中生成的热量基本上通过半导体层结构的不同部分从半导体器件消散。

73、在一些实施例中,半导体层结构具有厚度d和热扩散角α,并且相邻集总栅极电阻器的面对侧彼此间隔开至少2*d*tan(α)。

74、在一些实施例中,半导体器件还包括与栅极衬垫和栅极指之间的集总栅极电阻器中的第一集总栅极电阻器串联耦合的第一开关以及与栅极衬垫和栅极指之间的集总栅极电阻器中的第二集总栅极电阻器串联耦合的第二开关。在一些实施例中,第一开关可以是在第一栅极电阻器内实现的二极管。在一些实施例中,第一开关包括第一二极管,其在正向偏置时允许电流从栅极衬垫流向栅极指,并且第二开关包括第二二极管,其在正向偏置时允许电流从栅极指流向栅极衬垫。在一些实施例中,半导体器件对于从栅极衬垫流向栅极指的栅极电流具有第一总栅极电阻值,并且对于从栅极指流向栅极衬垫的栅极电流具有第二总栅极电阻值,其中第二总栅极电阻值与第一总栅极电阻值不同。

75、在一些实施例中,当在平面图中观看时,栅极衬垫具有倒l形或l形。

76、根据本发明的还有进一步实施例,提供了半导体器件,其包括宽带隙半导体层结构、宽带隙半导体层结构上的栅极衬垫、宽带隙半导体层结构上的栅极总线,以及在栅极衬垫与栅极总线的一部分之间延伸的集总栅极电阻器,栅极总线的该部分与半导体器件的第一外边缘相邻地延伸。

77、根据本发明的还有附加的实施例,提供了半导体器件,其包括宽带隙半导体层结构、宽带隙半导体层结构上的栅极衬垫,以及多个集总栅极电阻器,每个集总栅极电阻器电耦合到栅极衬垫,当在平面图中观看半导体器件时,多个集总栅极电阻器中的至少相应的一对集总栅极电阻器从栅极衬垫的至少三侧中的每一侧朝外延伸。

- 还没有人留言评论。精彩留言会获得点赞!