芯片级封装件的制作方法

本公开的各方面涉及包括竖直半导体装置的芯片级封装件。本公开的各方面还涉及用于制造这种封装件的方法。在本公开的上下文中,竖直半导体装置应当被解释为包括半导体裸片的装置,其中该装置包括在半导体裸片的相对侧上的装置端子,通过该装置端子可以将电信号供应给该装置和/或从该装置提取电信号。此外,在本公开的上下文中,芯片级封装件对应于直接表面可安装封装件,其尺寸基本上对应于其所包括的单个半导体裸片的尺寸。

背景技术:

1、通常同时大量制造半导体装置。例如,可以使用被分成多个基本相同的区段的半导体晶圆,其中每个半导体装置使用相应的区段来实现。

2、图1(顶部)示出了这种分区段的示例。在这里,示出了半导体晶圆100的被分成区段110的部分。每个区段110包括内部部分111和周边部分112。实际的装置在内部部分111内部实现,而周边部分112包括用于分割各个区段110的锯切线或切割道。在至少部分分割之后,区段也被称为半导体裸片。

3、图1(底部)示出了从半导体晶圆100获得的半导体裸片的示例性截面。在这里,半导体裸片110构成双端子二极管,其具有布置在第一表面s1上的第一端子t1和布置在与第一表面s1相对的第二表面s2上的第二端子t2。法线方向d可被标识为垂直于第一表面s1并从第一表面s1向第二表面s2延伸。

4、如图1(底部)所示,半导体裸片110的内部部分111包括一个或多个电绝缘层120(在下文中统称为钝化层)。第二端子t2通过钝化层120中的一个或多个开口暴露。钝化层120不存在于或者不完全存在于半导体裸片110的周边部分112中。

5、半导体裸片110的周边部分112包括优选地围绕内部部分111的所有侧面的锯切线或切割道的剩余部分。当例如通过穿过锯切通道的锯切来分割半导体裸片110时,去除来自对应区段110的周边部分112的材料。因此,切割或锯切之前的区段110的周边部分112大于半导体裸片110的周边部分112。

6、半导体裸片110可以形成具有布置在虚线l1上方的p型掺杂区域和布置在虚线l1下方的n型掺杂区域的竖直pn二极管。

7、图1所示类型的半导体裸片不能总是用作芯片级封装件。例如,当将半导体裸片110安装在诸如印刷电路板的载体上时,可能存在短路的风险。接下来结合图2对此进行解释。

8、图2(顶部)示出了图1所示类型的半导体裸片110,其被布置为安装在印刷电路板200上的芯片级封装件。如图所示,法线方向d平行于印刷电路板200。

9、印刷电路板200包括在两侧上覆盖有金属迹线210a、210b、211a、211b的介电层201。例如,在其顶表面上,印刷电路板200包括第一接触焊盘210a、第二接触焊盘210b和阻焊层(solder mask layer)220。使用焊料230或另一导电附接材料,半导体裸片110的端子t1连接到第一接触焊盘210a,并且半导体裸片110的端子t2连接到第二接触焊盘210b。

10、如图2(顶部)所示,布置在虚线l1上方的p型掺杂区域上的端子t1经由焊料230连接到半导体裸片110的侧壁。在那里,如箭头a所示,它可以接触在虚线l1下方的n型掺杂区域。因此,在端子t1和t2之间产生短路。

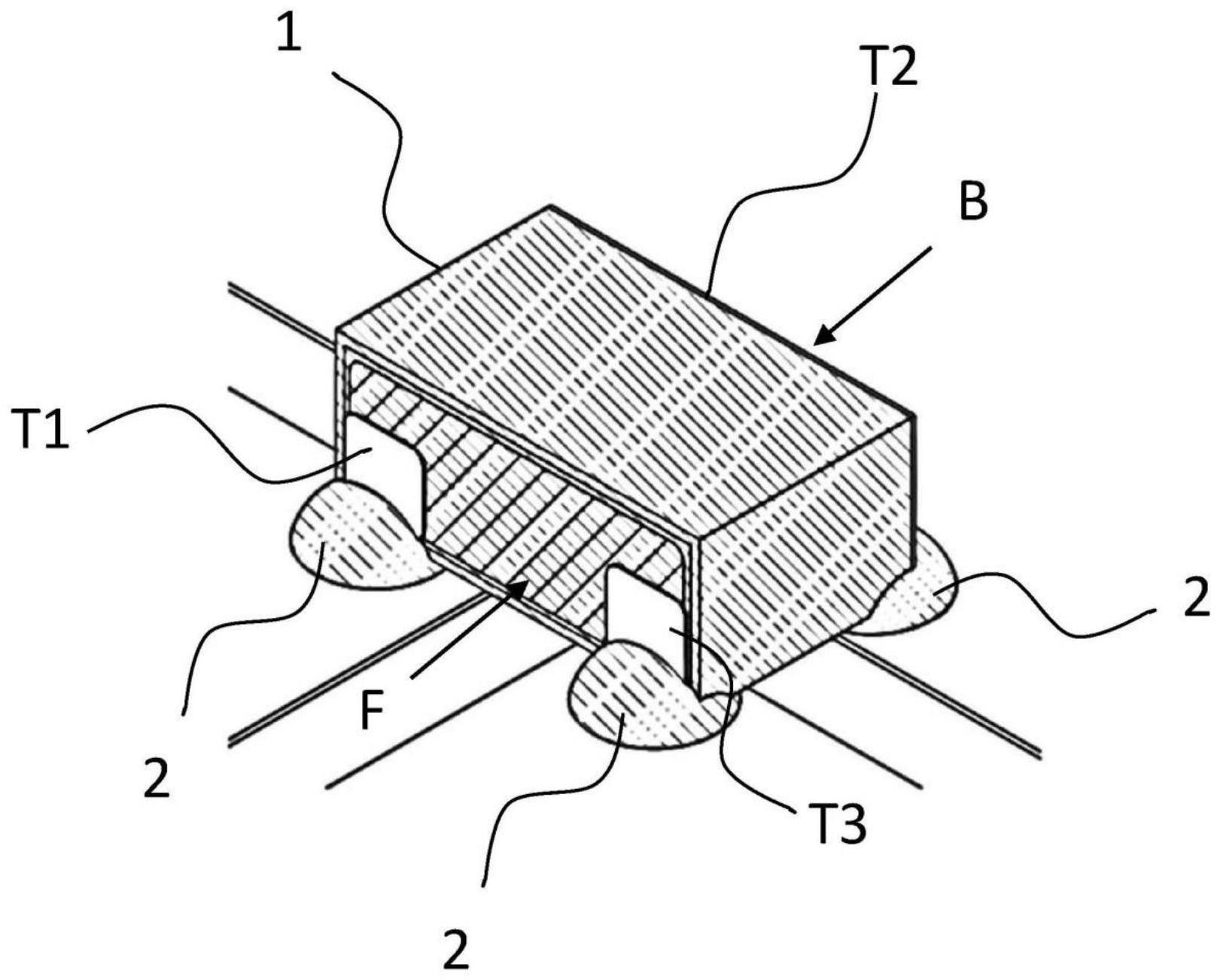

11、图2示出了安装双端子半导体裸片作为芯片级封装件。图3示出了其中三端子半导体裸片被安装为芯片级封装件的示例。在这里,示出了双极型晶体管,双极型晶体管具有布置在半导体裸片1的前侧f处的两个端子t1、t3和布置在半导体裸片1的背侧b处的一个端子t2。例如,端子t1、t2、t3可以分别连接到双极型晶体管的基极、发射极和集电极。前侧f设置有钝化层,该钝化层覆盖除了端子t1、t3的位置之外的前侧f,而背侧b完全被端子t2覆盖。

12、在切割或锯切晶圆之前施加钝化层。因此,在切割或锯切晶圆之后,半导体裸片1的侧壁被暴露。此外,即使在切割之前钝化层覆盖整个前侧,而不是仅存在于半导体裸片的内部部分中,与锯切相关联的机械动作也可能导致钝化层的至少一部分从半导体裸片110分离,从而暴露半导体裸片的半导体主体并且增加电短路的风险。

13、特别是对于本公开的各方面涉及的高电压装置,终止(termination)结构被布置在竖直半导体装置周围。这些终止结构通常被布置成靠近周边部分和内部部分之间的边界,并且用于防止在装置的边缘附近发生过早的电压击穿。在图2和图3中,在焊料与半导体裸片的周边部分中的半导体主体和/或与侧壁电接触的情况下,可能影响电场分布并且可以观察到电压击穿的降低。对于高电压装置重要的另一性能参数是在反向偏置条件下的泄漏电流。申请人已经发现,当焊料与半导体裸片的周边部分中的半导体主体和/或与侧壁电接触时,泄漏电流通常恶化。

14、在本领域中,已知用于获得用于将半导体裸片的侧壁电绝缘的电绝缘层的技术。例如,us2018233426a1公开了一种用于通过原子层沉积(ald)实现水平装置的6侧(6s)保护的方法。在沉积期间,装置的半导体裸片的一侧被布置在载体上,从而防止绝缘层将覆盖布置在该侧上的装置端子。然而,对于竖直装置,存在绝缘层将沉积在布置在半导体裸片的另一侧上的装置端子上的问题。因此,在沉积之后,需要从这些端子去除绝缘层。

15、ald是一种高度共形的沉积技术,通过该技术可以在相对低的温度下沉积非常薄的层。ald涂层的介电强度通常是优异的,允许在半导体裸片的拐角周围和侧壁上的良好的电绝缘。ald涂层的另一个优点是它们提供足够的强度,使得它们保持附着到半导体主体,并且在处理或安装半导体装置期间不被损坏。

16、申请人已经发现,找到一方面提供足够的机械稳健性(mechanical robustness)、但另一方面可以没有太多困难地从(一个或多个)装置端子去除的合适的绝缘层是非常困难的。例如,尽管使用ald技术获得的共形层显示出优异的机械稳健性,但是在沉积之后它们不能被容易地去除,因为这些层至少在很大程度上是化学惰性的。

17、ep3113219a1公开了一种具有台面型结构的竖直半导体装置,该台面型结构的侧壁被使用原子层沉积所沉积的绝缘层覆盖。在沉积该绝缘层之前,在顶侧上沉积牺牲层。通过去除牺牲层,可以从顶侧去除绝缘层,从而暴露该侧上的电端子。

18、ep3113219a1中公开的容纳竖直半导体装置的半导体裸片被配置为将其背侧平坦地安装在诸如印刷电路板的载体上。然后可以使用诸如接合线的常规手段来进行到顶侧的连接。

19、申请人已经发现ep3113219a1中公开的用于将侧壁绝缘的方法不适用于使半导体裸片能够用作芯片级封装件。

技术实现思路

1、根据本公开的一方面,提供了一种用于制造诸如芯片级封装件的半导体装置的方法,在该方法中上述问题不发生或至少在较小程度上发生。该方法包括提供布置在载体上的多个半导体裸片,其中半导体裸片具有第一表面和与第一表面相对的第二表面,半导体裸片通过第一表面布置在载体上。

2、半导体裸片各自包括内部部分和围绕内部部分的周边部分,其中半导体裸片各自在周边部分中至少包括曾用于或将用于将半导体裸片与半导体晶圆上的其它半导体裸片分割的锯切线或切割道的剩余部分,并且半导体裸片各自包括在内部部分内部实现的半导体竖直装置。钝化层至少布置在半导体裸片的内部部分中。

3、每个半导体裸片包括:至少一个第一端子,其被布置在该半导体裸片的第一表面处;至少一个第二端子,其被布置在该半导体裸片的内部部分中的第二表面处,并且通过钝化层中的一个或多个开口至少部分地暴露;以及侧壁,其在第一表面和第二表面之间。

4、根据本公开的一方面,在半导体裸片的第二表面处提供牺牲层,其中牺牲层至少部分地覆盖至少一个第二端子,并且包括与相邻半导体裸片之间的空间对准的第一开口和至少部分地与半导体裸片的周边部分对准的第二开口。第一开口和第二开口可以合并。

5、该方法还包括通过第一开口和第二开口在半导体裸片上布置共形涂层。

6、此外,该方法包括通过去除牺牲层来去除布置在牺牲层上的共形涂层。保留在半导体裸片上的共形涂层覆盖半导体裸片的周边部分,并且至少部分地覆盖半导体裸片的侧壁。以这种方式制造的半导体裸片可以用作芯片级封装件。

7、共形涂层应当优选地至少覆盖周边部分的其中半导体裸片的半导体主体否则将暴露的那些区域。在一些实施例中,周边部分完全被共形涂层覆盖。

8、根据本公开的一方面,不是通过例如使用蚀刻技术直接化学接合(engage)共形涂层,而是通过去除下面的牺牲层,来去除布置在第二端子上方的共形涂层。以这种方式,可以使用具有优异的机械稳健性的绝缘层(即,共形涂层),即使该绝缘层本身基本上是化学惰性的。通常,绝缘层将包括不同材料的多个层。作为示例,绝缘层将包括交替堆叠的两种不同材料。

9、因为共形涂层覆盖周边部分和侧壁,所以在焊料或其它导电附接材料与半导体裸片在侧壁和/或第二表面处的暴露部分之间不可能有任何直接接触。以这样的方式,可以避免如图1和图2所示的短路。此外,因为在焊料和侧壁之间不存在直接接触,所以在安装半导体裸片时不会干扰电场分布。

10、保留在半导体裸片上的共形涂层可以至少部分地覆盖半导体裸片的内部部分。此外,共形涂层可以包括一个或多个开口,至少一个第二端子通过该一个或多个开口至少部分地暴露。该一个或多个开口的表面面积可以小于至少一个第二端子的表面面积,至少一个第二端子通过该一个或多个开口至少部分地暴露。例如,至少一个第二端子可以在共形涂层下面延伸,共形涂层优选地在至少一个第二端子的所有侧面上。此外,保留在半导体裸片上的共形涂层可以至少部分地覆盖钝化层。为了暴露至少一个第二端子,可以将保留在半导体裸片上的共形涂层中的一个或多个开口与钝化层中的一个或多个开口对准。优选地,共形涂层中的一个或多个开口优选地在所有侧面上大于钝化层中的所述一个或多个开口。

11、周边部分可以不被钝化层覆盖或不被钝化层完全覆盖。这避免了在锯切或切割期间钝化层的部分的不受控制的断裂。钝化层可以是由氮化硅、氧化硅和氮氧化硅组成的组中的一种或多种。

12、多个半导体裸片可以对应于布置在载体上的经过切割的半导体晶圆。经过切割的晶圆可以对应于部分割切的经过切割的晶圆,例如半割切的经过切割的晶圆,在部分割切的经过切割的晶圆中裸片通过半导体晶圆的一部分仍然互连。可替换地,经过切割的晶圆可以对应于其中半导体裸片已经被物理分离的完全割切的经过切割的晶圆。然而,本公开不排除半导体裸片已经被布置在载体上而不属于一个晶圆的实施例。例如,可以已经使用拾取和放置设备将半导体裸片布置在载体上。

13、可以通过执行原子层沉积来布置共形涂层。执行原子层沉积可以包括使用三甲基铝和水、以及四氯化钛和水作为前体对。使用这些前体对,可以沉积al2o3和tio2的交替层堆叠件。

14、可以当在切割之前半导体裸片在晶圆中仍然互连时将牺牲层布置在半导体裸片上。例如,当半导体裸片在晶圆中仍然互连时并且在将该晶圆布置在载体上之前,牺牲层可以例如通过沉积、旋涂、蒸发、喷墨印刷或模版印刷被布置在半导体裸片上。牺牲层可以选自由光致抗蚀剂、聚合物、薄金属层、自组装单层和/或其组合组成的组。此外,该方法可包括在牺牲层上布置并图案化掩模层,以及通过掩模层中的开口去除牺牲层。在半导体裸片的对应于这些开口的区域中,由于在这些区域中在共形涂层下方不存在牺牲层,因此在稍后的阶段将不去除共形涂层。

15、可以使用包括多个金属层的金属层堆叠件形成至少一个第二端子,其中牺牲层由被布置为距第二表面最远的一个或多个金属层或其一部分形成。该金属层堆叠件可以例如包括tinivag、niau、ni、al、tiniag、auniag、auasniag和/或其组合。通过去除形成牺牲层的一个或多个金属层或其一部分,将去除位于牺牲层正上方的共形涂层,并且剩余的金属层将形成至少一个第二端子。此外,同样在这种情况下,晶圆切割的工艺将导致在牺牲层中形成开口。

16、可以通过借助于光烧蚀来烧蚀牺牲层而去除牺牲层。在这种情况下,使用具有适当波长、脉冲持续时间和/或功率的光照射牺牲层。包含在光中的能量在牺牲层内部被转换成热量。由于所产生的热量,牺牲层将剧烈地烧蚀,从而也破坏了与牺牲层接触的共形涂层。通常,以基本上均匀的方式提供光。在一些实施例中,更具体地在其中牺牲层的存在不影响半导体裸片的机械或电气行为的那些实施例中,光可不被均匀地提供。相反,可以例如使用光掩模或阴影掩模并使用标准曝光技术来对光进行图案化。以这种方式,可以局部地去除牺牲层。

17、本公开不排除去除牺牲层的其它手段,只要这些手段不干扰或损坏半导体裸片的其它组件。例如,去除牺牲层可以包括向牺牲层和共形涂层提供热冲击,从而导致共形涂层和牺牲层相互分层。随后去除由于施加热冲击而可能是薄片形式的分层的共形涂层。牺牲层优选是光敏层,例如光致抗蚀剂。在这种情况下,可以通过例如使用激光源施加光能来提供热冲击。可以可选地执行清洁步骤,例如清洁等离子体,以去除剩余的牺牲层。

18、可替换地,去除牺牲层可以包括执行研磨、切割、割切或其他机械操作,以去除牺牲层和覆盖该牺牲层的共形涂层。在这种情况下,共形涂层和牺牲层物理地接合(engage)。可以可选地执行清洁步骤,例如清洁等离子体,以去除剩余的牺牲层。

19、代替牺牲层是金属堆叠件的一部分或沉积牺牲层,还可以通过将第一箔附接到半导体裸片的第二表面来形成牺牲层。第一箔可以设置有上述第一开口和第二开口。当使用第一箔作为牺牲层时,可以通过从第二表面去除第一箔来去除牺牲层。如果第一箔包括布置在至少一个第二端子上的开口,则在已经去除第一箔之后,共形涂层可以仍然存在于至少一个第二端子上。只要保持足够的端子面积未被共形涂层覆盖,与这种端子的电接触的电特性就不会或几乎不会受到影响。

20、载体可以包括第二箔。第二箔可以是切割箔。此外,第二箔可以包括多个开口以允许共形涂层通过这些开口形成在侧壁上。在布置共形涂层之后,半导体裸片和第二箔可以被分离。这可以例如在拾取和放置过程期间完成,在该过程中从第二箔拾取半导体裸片。如果第二箔包括布置在至少一个第一端子上的开口,则在已经去除第二箔之后,共形涂层可以仍然存在于至少一个第一端子上。只要保持足够的端子面积未被共形涂层覆盖,与这种端子的电接触的电特性就不会或几乎不会受到影响。

21、根据本公开的另一方面,提供了一种诸如芯片级封装件的半导体装置,其包括具有内部部分和围绕内部部分的周边部分的半导体裸片,其中半导体裸片在周边部分中至少包括曾用于将半导体裸片与半导体晶圆上的其它半导体裸片分离的锯切线或切割道的剩余部分,并且半导体裸片包括在内部部分内部实现的半导体竖直装置,其中钝化层至少布置在半导体裸片的内部部分中。

22、半导体裸片包括第一表面和与第一表面相对的第二表面。半导体裸片包括布置在其第一表面处的至少一个第一端子、布置在其第二表面处并且通过钝化层中的一个或多个开口至少部分地暴露的至少一个第二端子、以及在第一表面和第二表面之间延伸的侧壁。

23、半导体裸片还包括覆盖周边部分和侧壁的至少一部分的共形涂层,以防止在将半导体装置安装在载体上时在至少一个第一端子和至少一个第二端子之间发生短路。共形涂层可以至少部分地覆盖内部部分,其中共形涂层包括一个或多个开口,至少一个第二端子通过该一个或多个开口至少部分地暴露。该一个或多个开口的表面面积可以小于至少一个第二端子的表面面积,该至少一个第二端子通过该一个或多个开口至少部分地暴露。例如,至少一个第二端子可以在共形涂层下面延伸,共形涂层优选地在至少一个第二端子的所有侧面上。

24、共形涂层可以至少部分地覆盖钝化层。为了暴露至少一个第二端子,共形涂层中的一个或多个开口可以与钝化层中的一个或多个开口对准。优选地,共形涂层中的一个或多个开口优选地在所有侧面上大于钝化层中的所述一个或多个开口。

25、周边部分可以不被钝化层覆盖或不被钝化层完全覆盖。这避免了在锯切或切割期间钝化层的部分的不受控制的断裂。在实施例中,在切割之前的区段的周边部分中提供钝化层达周边部分的面积的50%,优选地达25%。对于在切割或锯切之后获得的半导体裸片,在周边部分中提供钝化层达周边部分的面积的75%,优选达50%。如上所述,其中在周边部分中不设置钝化层的实施例也是可以的。钝化层可以是由氮化硅、氧化硅和氮氧化硅组成的组中的一种或多种。

26、至少一个第一端子和/或第二端子可以设置有包括共形涂层的多个岛。这些岛例如在使用第一箔时形成,第一箔包括如上所述在至少一个第二端子上方形成的开口。至少一个第一端子可以覆盖整个第一表面。

27、共形涂层可以包括通过原子层沉积获得的涂层,并且优选包括交替布置的al2o3和tio2层。层的这种组合提供了在焊接和粘合过程中对化学品的防护,并且提供了对湿气和离子污染的防护。此外,它提供了高的电击穿强度并构成了良好的电绝缘体。半导体竖直装置可以是从由沟槽mosfet、平面mosfet、pn二极管、肖特基二极管、齐纳二极管和双极结型晶体管组成的组中选择的装置。额外地或可替换地,半导体裸片可包括导电半导体衬底,例如n型掺杂晶圆衬底或p型掺杂晶圆衬底。

28、半导体装置可以包括垂直于第一表面并从第一表面向第二表面延伸的法线方向。半导体装置可以被配置为被布置在诸如印刷电路板的载体上,并且其法线方向平行于载体,其中至少一个第一端子被配置为连接到载体上的至少一个第一接触焊盘,并且其中至少一个第二端子被配置为连接到载体上的至少一个第二接触焊盘。

29、根据另一方面,本公开提供了一种包括诸如印刷电路板的载体的系统,载体包括至少一个第一接触焊盘和与至少一个第一接触焊盘间隔开的至少一个第二接触焊盘。该系统还包括如上所述的半导体装置,该半导体装置以其法线方向平行于载体的方式安装到载体。至少一个第一端子使用导电附接材料电连接到至少一个第一接触焊盘,并且至少一个第二端子使用导电附接材料电连接到至少一个第二接触焊盘。导电附接材料可以是由焊料、导电胶和银烧结材料组成的组中的一种或多种。

- 还没有人留言评论。精彩留言会获得点赞!