热电堆像元阵列芯片与驱动电路芯片的集成电路的制作方法

本发明涉及半导体器件领域,尤其涉及一种热电堆像元阵列芯片与驱动电路芯片的集成电路。

背景技术:

1、传统的热电堆阵列主流技术是通过底硅刻蚀实现热电偶与支撑硅的热隔离。通过干法或湿法刻蚀掉热电偶下面的硅,是热电偶底部悬空以实现绝热,由于工艺和roic限制底硅刻蚀技术留下的硅基底会占很大的面积,该面积对单个热电堆像元来说属于“无效”面积,这部分面积严重限制了热电堆阵列像元的小型化。

2、另一方面,热电堆单个像元与iorc并排放置,导致芯片面积很大,也严重限制了热电堆阵列芯片的小型化。

3、因而,研发一种减小芯片尺寸的热电堆阵列与读出电路的集成结构与制作工艺,成为本领域技术人员亟待要解决的技术重点。

技术实现思路

1、本发明提供一种热电堆像元阵列芯片与驱动电路芯片的集成电路,以解决如何减小热电堆像元阵列芯片与驱动电路芯片的集成电路尺寸的问题。

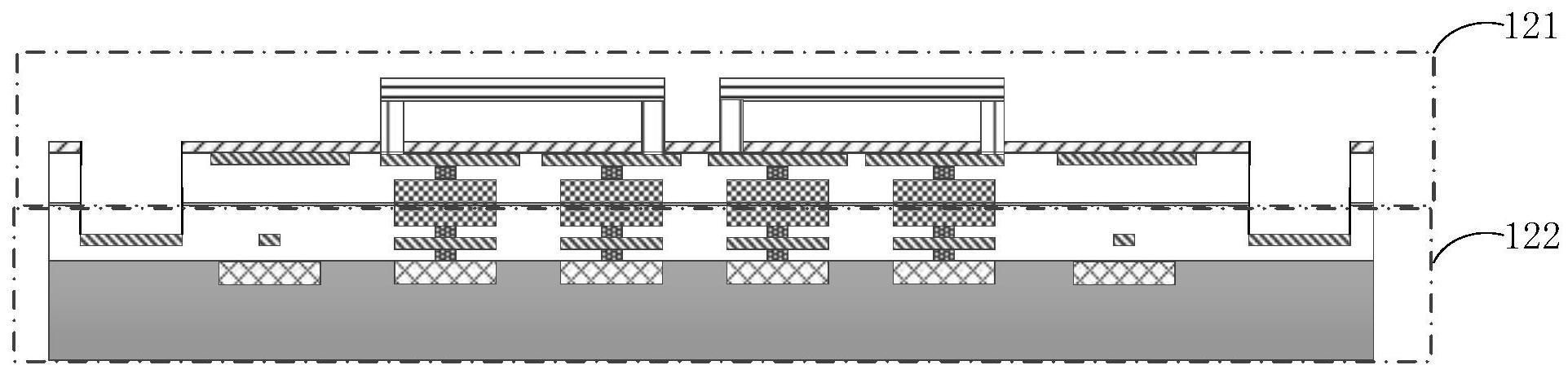

2、根据本发明的第一方面,提供了一种热电堆像元阵列芯片与驱动电路芯片的集成电路,包括:

3、热电堆像元阵列芯片,包括:第一热电偶与第二热电偶;所述第一热电偶与所述第二热电偶沿水平方向相对设置;

4、驱动电路芯片,所述驱动电路与所述第一热电偶和/或所述第二热电偶沿竖直方向依次堆叠,且所述热电堆像元阵列芯片电性连接于所述驱动电路芯片上。

5、可选的,所述驱动电路芯片包括:若干第一互连结构,所述若干第一互连结构形成于所述驱动电路芯片的第一侧;所述驱动电路芯片的第一侧表征了所述驱动电路芯片的靠近所述第一热电偶或所述第二热电偶的一侧;

6、所述热电堆像元阵列芯片还包括若干第二互连结构,所述若干第二互连结构形成于所述热电堆像元阵列芯片的第一侧;所述热电堆像元阵列芯片的第一侧表征了所述热电堆像元阵列芯片的靠近所述驱动电路芯片的一侧;

7、其中,所述若干第二互连结构形成于所述若干第一互连结构的顶端,以使得所述热电堆像元阵列芯片与所述驱动电路芯片电性连接。

8、可选的,所述热电堆像元阵列芯片还包括:

9、第一支撑柱,形成于所述第一热电偶与对应的第二互连结构之间,且连接所述第一热电偶与对应的所述第二互连结构,用于将所述第一热电偶的热量通过所述第一支撑柱与所述驱动电路芯片传递出去;

10、第二支撑柱,形成于所述第二热电偶与对应的第二互连结构之间,且连接所述第二热电偶与对应的所述第二互连结构,用于将所述第二热电偶的热量通过所述第二支撑柱与所述驱动电路芯片传递出去。

11、可选的,所述热电堆像元阵列芯片与驱动电路芯片的集成电路还包括:

12、绝缘介质层,填充于所述第二互连结构与所述第一互连结构之间的空隙中。

13、可选的,所述热电堆像元阵列芯片还包括:

14、释放阻挡层,成于所述若干第二互连结构的顶端与所述绝缘介质层的表面。

15、可选的,所述第二互连结构包括:

16、若干第一金属层、若干第一金属塞以及若干第一金属互连层;其中,所述若干第一金属层形成于所述释放阻挡层的背离所述第一热电偶或所述第二热电偶的表面上;所述若干第一金属互连层通过对应的第一金属塞连接对应的第一金属层。

17、可选的,所述热电堆像元阵列芯片与驱动电路芯片的集成电路还包括:

18、第二金属层与第三金属层,分别形成于所述驱动电路芯片中远离所述若干第一互连结构的两端;

19、若干pad开孔,分别形成于所述第二金属层与所述第三金属层的顶部,且贯穿所述释放阻挡层与部分所述绝缘介质层。

20、可选的,热电堆像元阵列芯片与驱动电路芯片的集成电路还包括:

21、封盖晶圆,所述封盖晶圆的中心包括一沟槽,所述沟槽形成封盖窗口;

22、若干吸气剂结构;依次分布于所述第一热电偶与所述第二热电偶相互背离的两侧的所述释放阻挡层的表面,以及所述封盖窗口的侧壁、部分表面以及部分底部上;其中,所述封盖窗口中的所述若干吸气剂结构与对应的所述释放阻挡层上的所述若干吸气剂结构沿第一方向相对设置;所述第一方向表征了所述第二互连结构与所述第一互连结构的堆叠方向;

23、若干第一闭环键合环与若干第二闭合键合环;所述若干第一闭环键合环分别形成于所述第一热电偶和所述第二热电偶与相邻的pad开孔之间的所述释放阻挡层的表面;若干所述第二闭环键合环形成于封盖窗口外的所述封盖晶圆表面,且所述第二闭环键合环与对应的所述第一闭环键合环相对设置。

24、根据本发明的第二方面,提供了一种热电堆像元阵列芯片与驱动电路芯片的集成电路的制作方法,用于制作本发明第一方面的任一项所述的热电堆像元阵列芯片与驱动电路芯片的集成电路,包括:

25、形成所述驱动电路芯片;

26、形成热电堆像元阵列芯片结构;所述热电堆像元阵列芯片结构包括:所述热电堆像元阵列芯片、牺牲层以及第一衬底;其中,所述热电堆像元阵列芯片包括所述第一热电偶与所述第二热电偶,所述第一热电偶与所述第二热电偶形成于所述第一衬底上;所述牺牲层填充于所述第一衬底与所述热电堆像元阵列芯片之间的空隙中;

27、将所述驱动电路芯片键合于所述热电堆像元阵列芯片的第一侧上;

28、去除所述第一衬底;

29、释放所述牺牲层。

30、可选的,去除所述第一衬底之后还包括:形成所述若干pad孔。

31、可选的,形成所述热电堆像元阵列芯片结构具体包括:

32、提供一所述第一衬底;

33、在所述第一衬底上形成所述第一热电偶与所述第二热电偶;

34、形成所述第一支撑柱、所述第二支撑柱、所述牺牲层以及所述释放阻挡层;其中,所述牺牲层形成于所述第一衬底、所述第一热电偶以及所述第二热电偶的表面,且填充于所述第一支撑柱与所述第二支撑柱之间的空隙中;所述释放阻挡层形成于所述牺牲层的表面;所述第一支撑柱形成于所述第一热电偶的表面,且贯穿所述释放阻挡层与所述牺牲层;所述第二支撑柱形成于所述第二热电偶的表面,且贯穿所述释放阻挡层与所述牺牲层;

35、形成所述若干第二互连结构与所述绝缘介质层:其中,所述若干第二互连结构通过所述第一支撑柱或所述第二支撑柱连接对应的所述第一热电偶与对应的所述第二热电偶;所述绝缘介质层形成于所述释放阻挡层的表面,且填充于若干所述第一互连结构之间的空隙中。

36、可选的,形成所述若干第二互连结构与所述绝缘介质层,具体包括:

37、形成若干所述第一金属层;若干所述第一金属层形成于所述释放阻挡层的表面,且所述第一金属层接触对应的所述第一支撑柱或对应的所述第二支撑柱;

38、形成图形化的绝缘层;所述图形化的绝缘层覆盖所述释放阻挡层与所述第一金属层的部分表面,以暴露出所述第一金属层的部分表面;

39、形成第一金属塞与所述第一金属互连层;所述第一金属塞形成于所述暴露出来的所述第一金属层的部分表面上;所述第一互连层形成于所述第一金属塞的顶端;

40、在所述形成图形化的绝缘层表面与所述第一金属互连层表面沉积绝缘层材料。

41、可选的,形成所述若干pad孔之前还包括:

42、形成图形化的牺牲层;所述图形化的牺牲层形成于所述释放阻挡层表面,且暴露出所述第一热电偶与所述第二热电偶相互背离的一侧的所述释放阻挡层的表面;

43、形成所述若干吸气剂结构、所述第一闭环键合环、所述第二闭环键合环以及所述封盖晶圆;

44、去除图形化的牺牲层;

45、将所述第一闭环键合环与对应的所述第二闭环键合环键合,以形成封装后的所述热电堆像元阵列芯片与驱动电路芯片的集成电路。

46、根据本发明的第三方面,提供了一种传感器,包括本发明第一方面的任一项所述的热电堆像元阵列芯片与驱动电路芯片的集成电路。

47、根据本发明的第四方面,提供了一种传感器的制作方法,包括本发明的第二方面的任一项所述的热电堆像元阵列芯片与驱动电路芯片的集成电路的制作方法。

48、本发明提供的一种热电堆像元阵列芯片与驱动电路芯片的集成电路,巧妙的将驱动电路芯片电性连接于热电堆像元阵列芯片的底部,形成垂直堆叠的集成电路结构,相对于现有技术而言,合理利用了热电堆像元阵列芯片底部悬空的硅所占用的空间,可以最大化热电堆像元阵列芯片的有效面积,缩小热电堆像元阵列芯片的尺寸。同时,由于读出电路芯片移到热电堆像元阵列芯片的下面,而非与热电堆像元阵列并排设计,因而进一步地减小了芯片尺寸。可见,本发明提供的技术方案,解决了如何减小热电堆像元阵列芯片与驱动电路芯片的集成电路尺寸的问题;另外,本发明提出的设计与cmos工艺全兼容,适合大规模量产。

- 还没有人留言评论。精彩留言会获得点赞!