一种低关断损耗的IGBT开关器件

本发明涉及一种带内置的偏置电路的igbt(insulated gate bipolartransistor,绝缘栅双极型晶体管)结构,属于功率电子器件领域。

背景技术:

1、在igbt器件中,器件导通时集电极向漂移区注入大量载流子,利用电导调制效应使得igbt功率器件拥有很小的导通电压。然而在器件关断过程中,漂移区中的大量过剩载流子将造成较长的拖尾电流,使得器件的关断时间长、关断损耗大。通过控制载流子注入的方法,能够较好地控制电导调制效应,实现在不影响导通电压的前提下减小关断损耗。

2、目前,一种集电极辅助栅技术被提出(j.wei,x.luo,g.deng,t.sun,c.wang,k.zhu,w.cui,z.wang,z.li and b.zhang,“ultrafast and low-turn-off loss lateraliegt with amos-controlled shorted anode,”ieee trans.electron devices,vol.66,no.1,pp.533-538,jan.2019,doi:10.1109/ted.2018.2873766),通过在集电极利用辅助栅控制空穴注入来调控电导,然而该辅助栅结构需要一个浮空栅极驱动信号驱动,技术困难。

3、目前,一种能实现阳极短路的外电路技术被提出(j.wu,m.kong,b.yi andx.b.chen,“an ultralow turn-off loss soi-ligbt with a high-voltage p-i-n diodeintegrated on field oxide,”ieee trans.electron devices,vol.66,no.4,pp.1831-1836,apr.2019,doi:10.1109/ted.2019.2898232),通过外电路自动实现阳极短路来调控电导,然而该外电路结构复杂,且需要绝缘层上硅(soi)技术,工艺复杂,成本更高,难以集成。

技术实现思路

1、为了实现低关断损耗的igbt器件,本发明提出了一种带内置偏置电路的igbt器件结构,该器件结构能够在不影响导通电压的同时降低关断损耗。同时,该器件和内置偏置电路采用同种工艺,易于集成,且驱动方式简单。

2、本发明的技术方案如下:

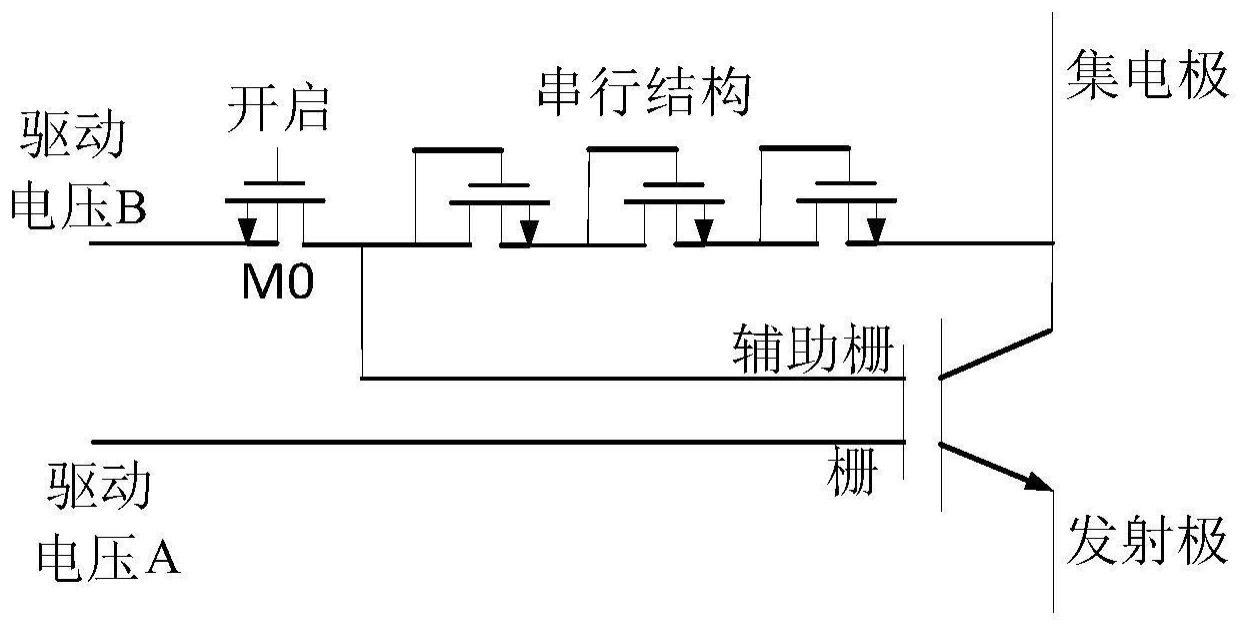

3、本发明的igbt器件是在传统横向igbt器件基础上,在集电极附近增加了一个辅助栅,并且在集电极下方的p注入区里通过离子注入在辅助栅旁形成了一个n+区(n型重掺杂区),辅助栅以及其旁边的n+区、p注入区、缓冲区构成了一个n型mosfet。参见图4,igbt的栅极和驱动电压a相连。内置偏置电路则由x+1个n型mosfet构成,其中一个mosfet(命名为m0)的漏极和igbt的辅助栅极相连,源极和驱动电压b相连,而其余的x个mosfet各自栅漏短接,再首尾相接串联起来,形成串行结构,一端的漏极和igbt器件的辅助栅极相连,另一端的源极和igbt器件的集电极相连。其中x需要满足的条件是:这x个串联的mosfet的阈值电压之和应大于驱动电压b,以防止在关断过程中串行结构正向导通而导致集电极电流增大、关断损耗增大。在满足上述条件的情况下,x应尽量小,以简化工艺、减小器件总面积。

4、具体的,在本发明的igbt开关器件中,所述igbt器件包括衬底、埋氧化层、漂移区、发射极、集电极、栅和栅极、辅助栅和辅助栅极,其中:埋氧化层和漂移区依次层叠在衬底上;发射极和集电极设置在漂移区上的有源区,栅极位于发射极和集电极之间;在发射极正下方漂移区内部形成有p型基区和位于该p型基区上的重掺杂p+区和重掺杂n+区;在集电极正下方漂移区内部形成有p注入区,该p注入区与漂移区之间为缓冲区;所述栅嵌入到漂移区中,位于所述p型基区及其上的重掺杂n+区旁边,或者,所述栅位于所述p型基区之上,栅与p型基区、重掺杂n+区和漂移区之间为栅氧化层,栅上设置栅极;所述辅助栅嵌入到所述p注入区、缓冲区及下方的漂移区中,或者,所述辅助栅位于所述p注入区之上,在p注入区内通过离子注入在辅助栅旁边形成有重掺杂n+区,辅助栅与p注入区、重掺杂n+区、缓冲区和漂移区之间为辅助栅氧化层,辅助栅上设置辅助栅极。

5、所述igbt器件为满足耐压需求,位于栅氧化层和缓冲区之间的漂移区长度≤150μm,优选范围为2~70μm,更优选为20~50μm;宽度≤150μm,优选范围为2~70μm,更优选为5~20μm。

6、图1展示了本发明的一种嵌入栅式igbt器件结构。该igbt器件结构包括衬底1、埋氧化层2、漂移区3、p型基区4、发射极正下方的重掺杂p+区5和重掺杂n+区6、栅7、栅氧化层8、p注入区9、集电极正下方的重掺杂n+区10、缓冲区11、辅助栅12和辅助栅氧化层13。发射极14和集电极16设置在有源区,栅极15位于发射极14和集电极16之间。当栅极15和发射极14之间的电压差大于栅7的阈值电压,并且集电极16和发射极14之间加正电压时,该igbt器件导通,p注入区9向漂移区3中注入空穴,漂移区3中载流子数目大大增加,引发电导调制效应,使得该器件的导通电压很小。当器件关断时,先提前在辅助栅极17上加正电压,使得辅助栅12开启,辅助栅12右侧的n型mosfet导通,p注入区9和缓冲区11发生短路,抑制了p注入区9的空穴注入,漂移区3中电导调制效应减弱。随后撤去栅极15电压,关断器件,这样漂移区3中载流子下降速度更快,以此获得更快的开关速度和更低的关断损耗。

7、在本发明的igbt开关器件中,所述内置偏置电路和所述igbt器件采用同种工艺制备在同一个衬底上。内置偏置电路中的n型mosfet包括衬底、埋氧化层、漂移区、源极、栅极和漏极,其中:埋氧化层和漂移区依次层叠在衬底上;源极和漏极设置在漂移区上的有源区,栅极位于源极和漏极之间;在源极正下方漂移区内部形成有p型基区和位于该p型基区上的重掺杂p+区和重掺杂n+区;在漏极正下方漂移区内部形成有重掺杂n+区;所述栅嵌入到漂移区中,位于所述p型基区及其上的重掺杂n+区旁边,或者,所述栅位于所述p型基区之上,栅与p型基区、p型基区上的重掺杂n+区和漂移区之间为栅氧化层,栅上设置栅极。

8、在所述内置偏置电路中,组成串行结构的各n型mosfet中位于栅氧化层与漏极下方重掺杂n+区之间的漂移区的长度≤150μm,优选范围≤10μm,而m0中位于栅氧化层与漏极下方重掺杂n+区之间的漂移区的长度≤150μm,优选范围为2~70μm,更优选为5~20μm。

9、图4展示了本发明的igbt器件和内置偏置电路的等效电路图。该内置偏置电路由x+1个n型mosfet构成,其中一个mosfet(m0)的漏极和igbt器件的辅助栅极相连,源极和驱动电压b相连;而其余的x个mosfet各自栅漏短接,再首尾相接串联起来,形成串行结构,一端的漏极和igbt器件的辅助栅极相连,另一端的源极和igbt器件的集电极相连。其中x需要满足的条件是:这x个mosfet的阈值电压之和应大于驱动电压b,以防止在关断过程中串行结构正向导通而导致集电极电流增大、关断损耗增大。在满足上述条件的情况下,x应尽量小,以简化工艺、减小器件总面积。

10、器件在导通状态时,驱动电压a开启,驱动电压b关断,此时栅开启,辅助栅关断,p注入区向漂移区中注入大量空穴,器件处于双极性导电状态,拥有很低的开态导通电压。

11、器件关断过程中,提前开启驱动电压b,辅助栅开启,串行结构阻止辅助栅极电压传到集电极造成影响。集电极空穴注入受到抑制,器件从双极性导电状态变成单极性导电状态。随后关断驱动电压a,栅关断,由于漂移区中载流子数量大大下降,器件能够更快关断,有效降低了关断损耗。

12、器件在关断状态时,驱动电压a关断,驱动电压b开启,此时栅关断。辅助栅极电压随着集电极电压上升到高电位,此时m0的栅源电压为0,m0不导通,将高电位阻断在辅助栅极。

13、器件在开启过程中,先开启驱动电压a,栅开启,器件导通,集电极电压下降到较低的导通电压,随后关断驱动电压b,辅助栅关断,集电极重新开始注入空穴,器件从单极性导电状态变成双极性导电状态。

14、本发明的有益效果:

15、通过本发明所提供的带内置偏置电路的igbt器件,能够有效地降低关断损耗,提高开关速度,且导通电压不会增大。同时,该igbt器件和内置偏置电路采用同种工艺制造,易于集成,工艺简单,驱动方式简单。

- 还没有人留言评论。精彩留言会获得点赞!