一种具有P型掺杂结构的半导体异质结场效应管

本发明属于微电子领域,具体为一种具有p型掺杂结构的半导体异质结场效应管。

背景技术:

1、氮化镓材料(gan)具有禁带宽度大、临界击穿场强高、电子迁移率高、导电性好、抗辐射及化学性质稳定等优点,同时由于其自身存在较强的自发极化效应,可以与铝镓氮(algan)等材料在界面处形成高浓度和高迁移率的二维电子气导电沟道,这也使得氮化镓基异质结场效应晶体管(gan hfet)在微波大功率器件上具有很大的应用前景。

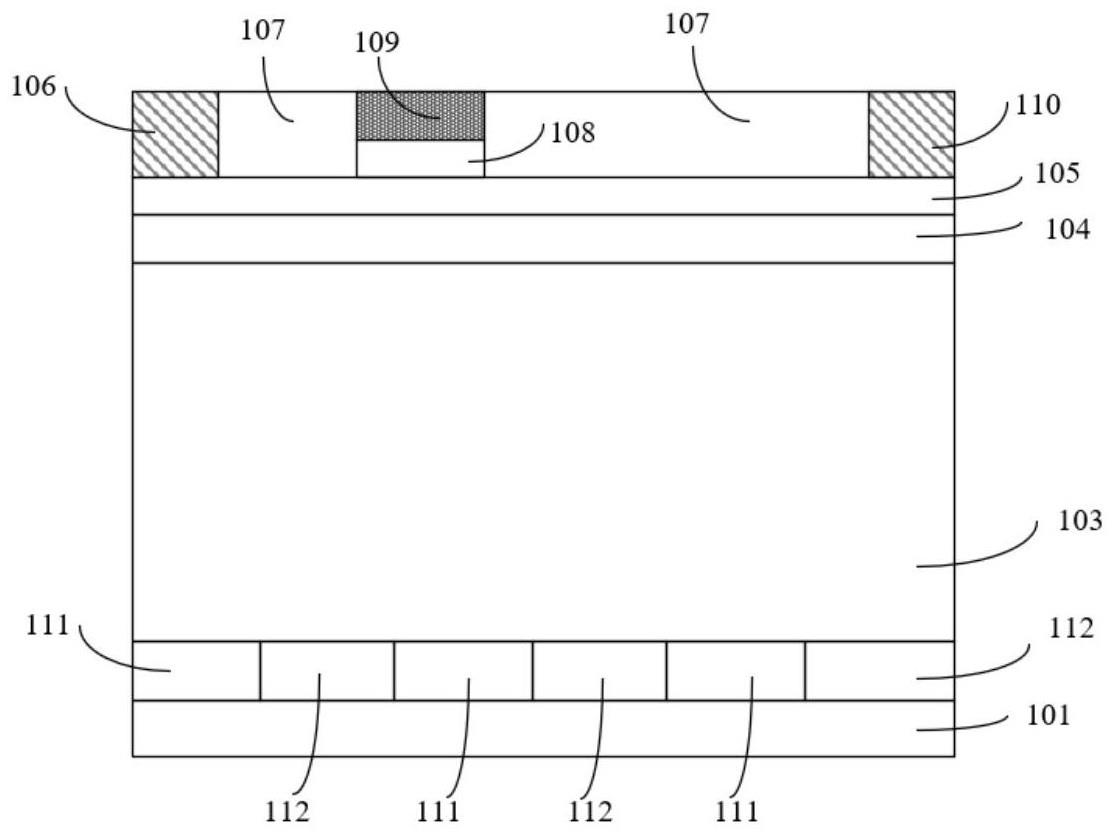

2、图1为常规增强型gan hfet结构示意图。该结构从下至上依次包括:衬底(101)、氮化镓缓冲层(103)、氮化镓沟道层(104)、铝镓氮势垒层(105),铝镓氮势垒层(105)上方设有源极(106)、漏极(110)、p型氮化镓层(108)和栅极(109),其中源极(106)与漏极(110)均与铝镓氮势垒层(105)形成欧姆接触,栅极(109)与p型氮化镓层(108)形成欧姆接触,器件上表面源极(106)与栅极(109)之间、以及栅极(109)与漏极(110)之间都覆盖有一层钝化层(107)。

3、对于常规gan hfet器件,在承受耐压时栅极与漏极之间的沟道二维电子气无法完全耗尽导致耗尽区宽度较窄,沟道电场主要集中于栅极边缘或漏极边缘,从而使得器件的击穿电压较低,同时,由于缓冲层材料为gan材料,沟道内的二维电子气无法得到限制,在缓冲层里会形成漏电路径,形成较大的泄漏电流,这也会导致器件提前击穿。

4、为了提高击穿电压,诸多措施被陆续提出,常见的有场板技术、背势垒、缓冲层掺杂、高/低k介质、衬底转移技术等方法。2004年,saito等人(saito w,takada y,etal.design and demonstration of high breakdown voltage gan high electronmobility transistor(hemt)using field plate structure for power electronicsapplications[j].japanese journal of applied physics,2004,43(4):2239-2242.)利用源场板技术制作出了击穿电压为600v的algan/gan hemt器件,其导通电阻为3.3mω·cm2。使用场板虽然可以降低栅极边缘电场,提高击穿电压,但同样会带来额外的寄生电容,使器件的频率特性和开关特性退化。

5、除了场板技术以外,其他提高击穿电压的技术也相继得到了大量研究。2010年,lu等人在文献(bin lu.high breakdown(>1500v)algan/gan hemts by substrate-transfertechnology[j].ieee electron device letters,2010,31(9):951-953.)中提出了一种衬底转移技术,先将gan hemt中的si衬底去除,然后将其转移到绝缘载体晶圆上,所实现的gan hemt结构得到了1500v以上的击穿电压以及5.3mω·cm2的ron·sp。

6、2016年,luo jun等人在文献(luo j,zhao s l,lin z y,et al.enhancement ofbreakdown voltage in algan/gan high electron mobility transistors usingdouble buried p-type layers[j].chinese physics letters,2016.)中使用了在n掺杂缓冲层中插入双掩埋p型层的结构,使用p型埋层部分耗尽沟道2deg二维电子气,耐压提升较多。但这种方法同样会部分耗尽2deg,导致器件导通电阻上升。栅下方的二维电子气部分耗尽也会影响器件阈值电压。对缓冲层进行n型掺杂也会导致器件漏电增大。

7、图2为带有单一p型均匀掺杂半导体层的gan hfet结构图,在氮化镓缓冲层下方设置一层单一p型均匀掺杂半导体层,可以通过提高缓冲层能带抑制缓冲层漏电和改善缓冲层及沟道层的电场分布,从而显著提高器件的击穿电压,降低漏电同时又不会增加器件导通电阻,其击穿电压为905v,远高于图1所示的常规器件的基穿电压405v。然而,使用单一p型均匀掺杂半导体层虽然可以降低栅极漏端电场峰值,改善缓冲层及沟道层的电场分布,但也在漏极边缘引入了一个较高的电场峰值,使得击穿点从栅极漏端转移到了漏极边缘,同样会造成器件提前击穿。同时其平均击穿电场强度依然远低于gan材料的临界击穿电场强度3mv/cm。

8、综上所述,针对目前电力电子器件应用领域,需要找到一种高耐压、高阈值电压、低导通电阻的gan基hfet实现方式。

技术实现思路

1、针对上述存在问题或不足,为解决现有gan hfet器件耐压不足的问题,本发明提供了一种具有p型掺杂结构的半导体异质结场效应管。

2、一种具有p型掺杂结构的半导体异质结场效应管,从下至上依次包括:衬底101、p型掺杂层102、氮化镓缓冲层103、氮化镓沟道层104和铝镓氮势垒层105,铝镓氮势垒层105上方还设有源极106、漏极110、p型氮化镓层108、栅极109,其中源极106与漏极110均与铝镓氮势垒层105形成欧姆接触,栅极109与p型氮化镓层108形成欧姆接触,器件上表面源极106与栅极109之间、以及栅极109与漏极110之间都覆盖有一层钝化层107。

3、所述p型掺杂层102的材料为alxinygazn材料,其中x+y+z=1,0≤x≤1,0≤y≤1,0≤z≤1;厚度小于氮化镓缓冲层103的厚度。通过p型掺杂层102对栅极漏端和漏极边缘的电场峰值以及沟道的平均电场进行调制,使其分布更加均匀;同时由于氮化镓缓冲层103的厚度大于p型掺杂层102厚度的屏蔽作用又避免了饱和输出电流的退化和导通电阻的增加,从而提高了器件的击穿电压和优值。

4、进一步的,所述p型掺杂层102为单一的p型非均匀掺杂区域111,或非均匀掺杂区域111与p型均匀掺杂区域112的组合结构,或掺杂浓度不同的第一p型均匀掺杂区域114和第二p型均匀掺杂区域115。

5、进一步的,所述非均匀掺杂区域111与p型均匀掺杂区域112两者多轮交替设置构成p型掺杂层102。

6、进一步的,所述第一p型均匀掺杂区域114和第二p型均匀掺杂区域115两者多轮交替设置构成p型掺杂层102。

7、进一步的,所述p型掺杂层102包括p型非均匀掺杂区域111、p型均匀掺杂区域112和本征半导体区域113,其中本征半导体区域113位于p型非均匀掺杂区域111与p型均匀掺杂区域112之间,不作任何掺杂。

8、进一步的,所述p型非均匀掺杂区域111、本征半导体区域113和p型均匀掺杂区域112三者依次交替排布n轮,n≥2。

9、根据电场连续性原则,上述p型掺杂层102当选用大于一种材料构成p型掺杂层,且多轮交替排布时,器件在承受耐压时多种材料掺杂区域间的界面处电场会发生突变,接触界面处会产生一个电场尖峰,该电场尖峰可以对沟道电场进行有效地调制,交替设置的多种材料掺杂区域可以形成多个电场尖峰,使得耐压效果更好。

10、进一步的,p型非均匀掺杂区域111的掺杂浓度范围为1×1016cm-3~1×1020cm-3;p型均匀掺杂区域的掺杂浓度范围为1×1016cm-3~1×1020cm-3。

11、进一步的,p型掺杂层102的非均匀掺杂方式为高斯掺杂或余误差分布掺杂。

12、本发明针对gan hfet器件耐压不足的问题,在衬底上引入一层p型掺杂层结构,对衬底上的半导体层进行p型掺杂,其中p型掺杂可以吸引栅极边缘的部分电场线,改善电场集中现象,使得耗尽区向漏极边缘扩展,在降低栅极漏端边缘的电场峰值的同时会在漏极边缘引入一个新的电场峰值,从而使得氮化镓沟道内的平均电场整体提高并且分布地更加均匀,但如果p型掺杂浓度过高会在漏极边缘引入一个很高的电场峰值,同样会导致器件提前击穿,所以衬底上p型掺杂层102即可以保证栅极漏端边缘的电场峰值得到降低,又不会在漏极边缘引入一个较高的电场峰值,使沟道电场整体分布变得更加均匀进而提高器件的击穿电压。同时较厚的gan缓冲层可以屏蔽p型掺杂层102对沟道的影响,保证了器件的正向导通特性。p型掺杂层102可以提高缓冲层的能带,阻碍氮化镓沟道内的二维电子气泄漏到缓冲层中,减小了泄漏电流。

13、综上所述,本发明通过p型掺杂层结构的材料以及种类进行设定,从而对栅极漏端和漏极边缘的电场峰值以及沟道的平均电场进行调制,使其分布更加均匀;同时由于较厚氮化镓缓冲层的屏蔽作用又避免了饱和输出电流的退化和导通电阻的增加,从而提高了器件的击穿电压和优值。在保证器件性能的前提下,有效解决了现有gan hfet器件耐压不足的问题。

- 还没有人留言评论。精彩留言会获得点赞!