SiO2阻挡层Ga2O3垂直UMOS晶体管及其制备方法

本发明属于微电子,特别涉及一种umos晶体管,可用于制作高压电路变压器电路芯片、高速铁路输电系统和民用电动车充电模块。

背景技术:

0、技术背景

1、随着第四代超宽禁带半导体的发展,氧化镓材料逐渐成为新一代半导体材料的焦点。目前可制备的氧化镓材料有α、β、γ、δ和ε五种晶型,由于其他几种亚稳定相在进行高温工艺处理时会转化成β-ga2o3,所以单斜的β-ga2o3具有最好的热稳定性,目前大部分研究工作也都是围绕β-ga2o3展开的。β-ga2o3具有约为4.8ev的超大禁带宽度,这一特征使其电离率较低,从而击穿场强较高,理论计算极限约为8mv/cm,超过第一代半导体si的20倍,第三代半导体sic和gan的1-2倍。此外,由于β-ga2o3具有较高的电子迁移率、介电常数和临界电场强度,其baliga优质达到4h-sic的3倍、gan的1.5倍。另外,β-ga2o3材料的导通电阻理论值很低,因此对于相同击穿电压条件下的单极器件,其导通损耗比sic、gan器件低至少一个数量级,有利于提高功率器件的效率。所以氧化镓材料在功率器件的研究和制作方面具有巨大的潜力和发展前景。

2、氧化镓场效应晶体管主要有水平结构和垂直结构两类。由于工艺和结构更加成熟,在目前发布的文章中,氧化镓场效应晶体管还是以水平结构为主。对于水平结构场效应晶体管,如果想获得较大的饱和电流和较高的击穿电压,就必须增大沟道的尺寸,进而牺牲芯片面积,且在增大面积的同时又会由于体材料缺陷总数的增加带来新的可靠性问题。然而,由于氧化镓材料的价带过于平缓,和受主电离能过大,在氧化镓材料和器件的制备过程中很难实现p型掺杂,无法像传统垂直结构一样采用pn结来对源漏之间的漏电进行有效的阻隔。

3、为了充分发挥氧化镓材料在耐高压和大功率方面的优势,垂直结构的氧化镓场效应晶体管才是更好的选择,对于垂直结构器件,其反偏电场分布在整块体材料上,在增大电场承受区域的同时不仅可避免表面击穿带来的可靠性问题,而且可获得更高的击穿电压,并且由于其结构特点,可以很容易地获得较大的导通电流,并在不多牺牲芯片面积的情况下,通过提高漂移区的厚度来获得更高的击穿电压。

4、然而,由于氧化镓材料的价带过于平缓和受主电离能过大的影响,在氧化镓材料和器件的制备过程中很难实现p型掺杂,无法像传统垂直结构一样采用pn结来对源漏之间的漏电进行有效的阻隔。

5、目前垂直型氧化镓场效应晶体管有两种结构:

6、第一种为早期工作中被采用的非平面的多鳍型结构,如图1所示,该结构自下而上包括漏电极、氧化镓衬底层、氧化镓漂移层、鳍型沟道、氧化铝栅氧化层、二氧化硅隔离层、栅电极和源电极。该结构通过侧壁调制的方法来实现源漏之间的电学隔离并获得了不错的栅控能力,成功实现了垂直型氧化镓场效应晶体管的基本功能。但是鳍型结构的沟槽栅极氧化层的拐角处会受到强烈的场应力使器件的可靠性降低,击穿电压只有1000v,并且由于鳍型结构的工艺实现复杂、精度要求高使器件的生产过程十分困难。

7、第二种为具有全离子注入电流阻挡层结构的氧化镓场效应晶体管,如图2所示,该结构自下而上包括漏电极、锡重掺杂氧化镓衬底层、硅掺杂氧化镓漂移层、镁离子注入电流阻挡层、硅离子掺杂氧化镓沟道、源电极、氧化铝栅氧化层和栅电极,该结构通过引入平面栅结构降低了垂直型氧化镓场效应晶体管的生产难度,并且避免了器件拐角处强烈的场应力问题,但是由于该结构器件的制备过程中需要高温退火使注入离子激活,该高温会导致引入的电子陷阱中心离子发生扩散,使源漏之间产生非理想的漏电通道,从而产生较大的泄漏电流,其击穿电压也还无法超过300v,并且其栅控能力不错,器件性能十分不稳定。

技术实现思路

1、本发明的目的在于针对上述现有技术的不足,提出一种具有sio2阻挡层的ga2o3垂直umos场效应晶体管及其制备方法,以提高器件击穿电压,避免源漏之间由于热扩散产生的泄漏电流,提升晶体管漏极输出电流并提高器件的栅控能力。

2、为实现上述目的,本发明的技术方案如下:

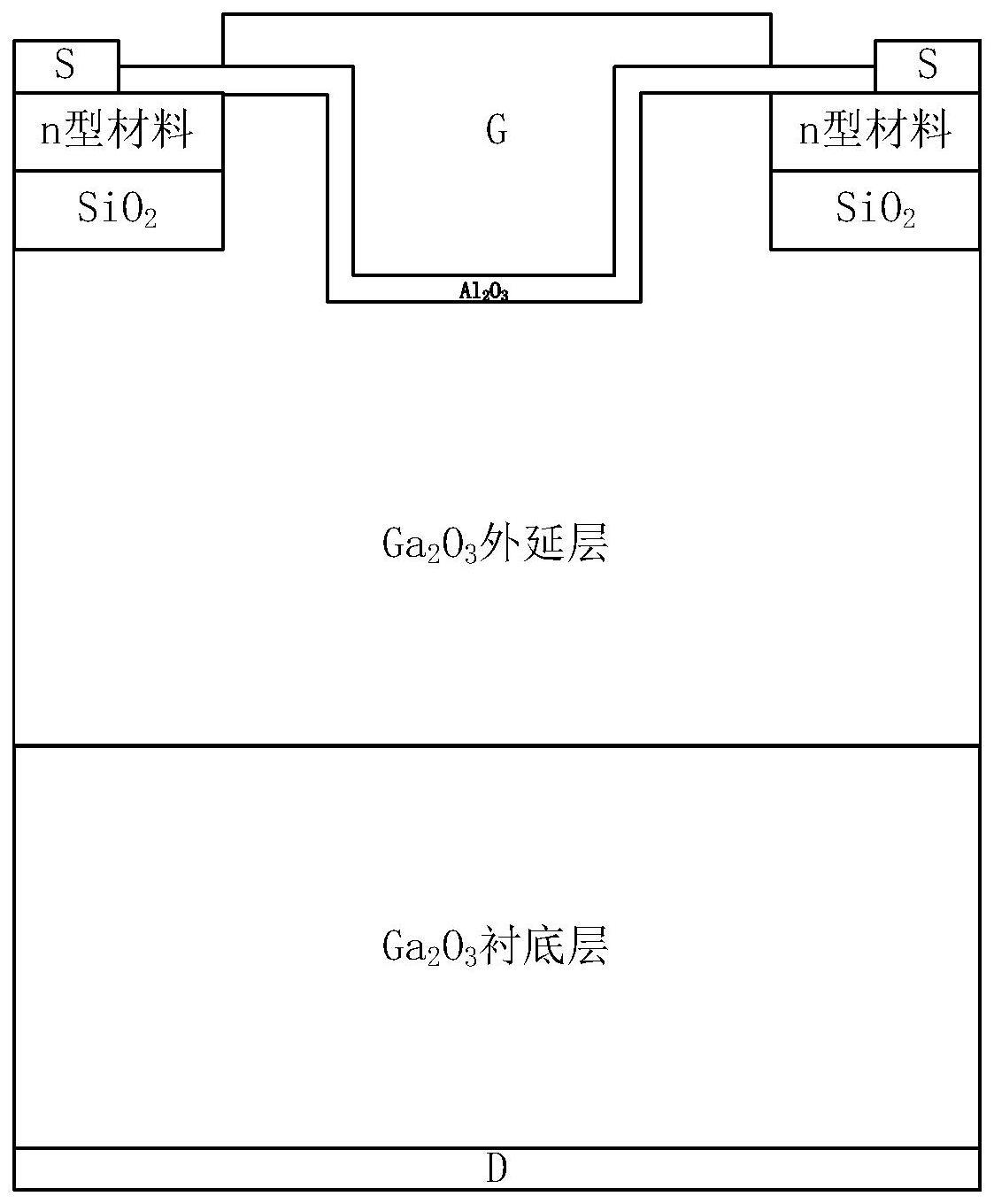

3、1.一种具有sio2阻挡层的ga2o3垂直umos场效应晶体管,包括氧化镓衬底层1、氧化镓外延层2、栅氧化层3,栅氧化层3上方设有t型栅电极g,氧化镓衬底层1下表面为漏电极d,其特征在于:

4、所述外延层2,其内部外围设有sio2电流阻挡层4,以实现有效的源漏间电学隔离,其中心设有u型栅凹槽5,以提高器件栅控能力并实现垂直导通沟道;其上方设有n型导电层6,以实现n型导电材料的再生长;

5、该n型导电层6的上方设有源电极s。

6、进一步,所述氧化镓衬底层1,采用厚度为500um-700um,浓度为1×1018-5×1018cm-3的n型高掺β-ga2o3材料。

7、进一步,所述氧化镓外延层2,其采用厚度为3um-10um,浓度为1.5×1016-1×1017cm-3的n型低掺β-ga2o3材料。

8、进一步,所述sio2电流阻挡层4,其厚度为500nm-1000nm。

9、进一步,所述n型导电层6,其采用厚度为5nm-50nm,浓度为1×1017-5×1019cm-3的n型高掺杂gan或sic或in2o3宽禁带或超宽禁带n型导电材料。

10、进一步,所述u型栅凹槽5,其深度为1um-10um。

11、2.一种制备sio2阻挡层ga2o3垂直umos晶体管的方法,其特征在于,包括如下步骤:

12、1)清洗外延片,即将同质外延的氧化镓片子依次放入丙酮溶液、无水乙醇溶液和去离子水中各超声清洗5min-10min,然后用氮气吹干;

13、2)在清洗后的外延片上进行光刻,形成待刻蚀区域,再将其放入反应离子刻蚀rie系统内,刻蚀掉外延片待刻蚀区域上的氧化镓并形成沟槽结构;

14、3)将刻蚀后的氧化镓外延片放入电感耦合等离子体增强化学气相淀积系统icp-cvd反应室内,设置反应室温度为80℃-90℃,在外延片表面淀积厚度为500nm-1000nm的sio2,再将淀积后的片子放入剥离液中,通过剥离形成sio2阻挡层;

15、4)通过原子层淀积ald工艺,在氧化镓外延片表面淀积厚度为10nm-20nm的n型导电材料;

16、5)在淀积后的外延片上进行光刻,形成待刻蚀区域,再将其放入反应离子刻蚀rie系统内,刻蚀掉外延片待刻蚀区域上的n型导电材料,形成第一欧姆接触区域;

17、6)在刻蚀后的外延片上进行光刻,形成待刻蚀区域,再将其放入icp刻蚀系统内,刻蚀掉待刻蚀区域的氧化镓,形成u型栅凹槽;

18、7)通过原子层淀积ald工艺,在刻蚀后的外延片表面淀积厚度为20nm-50nm的al2o3;

19、8)在淀积后的外延片表面光刻源端电极通孔,利用反应离子刻蚀rie系统刻蚀去掉电极通孔区域的al2o3;

20、9)将刻蚀完成的外延片再次光刻形成源端电极区域,通过电子束蒸发e-beam系统先在源端电极区域淀积ti/au,通过剥离形成源端电极,之后再在衬底表面淀积ti/au,形成漏端电极,并在n2环境中退火,形成第二欧姆接触区域;

21、10)在形成欧姆接触的外延片上表面通过光刻形成栅极区域,通过电子束蒸发e-beam系统在栅极区域淀积ni/au,通过剥离形成第一层栅电极;

22、11)在形成第一层栅金属后的外延片表面通过光刻形成栅极区域,再通过电子束蒸发e-beam系统在栅极区域淀积au,通过剥离形成第二层栅电极,完成器件制作。

23、本发明与现有技术相比,具有如下优点:

24、1.本发明由于在外延层中心设有u型栅刻蚀和t型栅结构,相比于现有的平面栅工艺,提高了器件的栅控能力,避免了器件因沟道夹断不充分而带来了源漏间漏电问题,提高了器件的耐压能力和对信号的控制能力。

25、2.本发明由于在外延层上部设有sio2高质量电流阻挡层结构,实现了源漏区域的电学隔离,同时由于sio2介电常数很高,将会显著提高垂直结构氧化镓的场效应晶体管器件击穿电压。

26、3.本发明由于在外延层上部设有sio2高质量电流阻挡层结构,相比现有的对离子注入区域注入mg离子或n离子形成源漏之间电流阻挡层的技术,避免了在后续高温工艺会引起mg离子或n离子的热扩散所产生较大的泄漏电流的问题。

27、4.本发明由于采用了原子层淀积ald工艺淀积的n型导电材料材料形成欧姆接触,相对现有技术采用离子注入工艺产生欧姆接触,避免了离子注入对晶格的损伤,使得半导体缺陷密度降低,晶格完整度提高,进而提高器件的耐压能力。

28、5.本发明由于在淀积的sio2电流阻挡层上通过原子层淀积ald工艺淀积n型导电材料形成高掺杂欧姆区域,避免了sio2阻挡层上再生长氧化镓材料工艺无法实现的问题。

- 还没有人留言评论。精彩留言会获得点赞!