功率半导体器件、功率器件模组、桥臂电路及电子设备的制作方法

本技术实施例涉及半导体器件技术,尤其涉及一种功率半导体器件、功率器件模组、桥臂电路及电子设备。

背景技术:

1、电力电子器件(power electronic device),又称为功率半导体器件,为用于电能变换和控制电路中的大功率电子器件;具有处理高电压、大电流的能力。功率半导体器件在电力电子电路中能够实现功率转换、功率开关、功率放大、线路保护和整流等功能。

2、在相关技术中的一些应用中,功率半导体器件可以作为开关器件应用在桥臂电路中。然而,在同一桥臂电路的上桥臂和下桥臂中,一个开关器件的动作会对另一个开关器件造成不利的影响,降低开关器件的可靠性或带来额外的开关损耗,该现象被称为“桥臂串扰”。

技术实现思路

1、本技术实施例提供一种功率半导体器件、功率器件模组、桥臂电路及电子设备,用于改善功率半导体器件作为开关器件应用到桥臂电路时,可能会产生桥臂串扰的问题。

2、为达到上述目的,本技术的实施例采用如下技术方案:

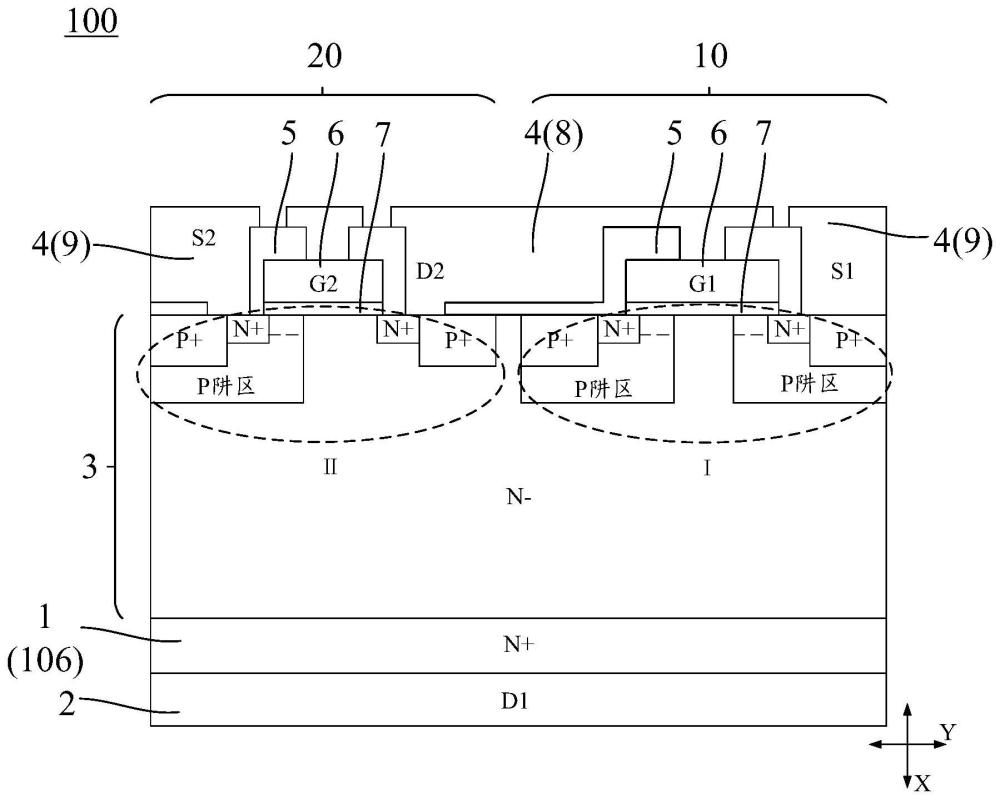

3、第一方面,本技术实施例提供了一种功率半导体器件,该功率半导体器件包括集成在片内的功率晶体管和泄放晶体管;

4、功率晶体管包括第一栅极、第一源极和第一漏极,泄放晶体管包括第二栅极、第二源极和第二漏极;第二源极和第二漏极中的一方与第一栅极相连,第二源极和第二漏极中的另一方与第一源极相连。

5、采用具有上述结构的功率半导体器件,可以通过控制泄放晶体管的导通和关断,控制功率晶体管中的第一栅极和第一源极是否导通。如此设计,在功率半导体器件作为开关器件应用到桥臂电路的场景中,可以在一个功率半导体器件动作过程中,控制同一桥臂中另一个功率半导体器件中的泄放晶体管导通,以控制功率晶体管中的第一栅极和第一源极导通,在功率晶体管的第一栅极和第一源极之间增加泄放串扰电流的通路,从而能够使功率半导体器件不受另一功率半导体器件的影响。因此可以改善桥臂串扰导致的功率晶体管无法可靠关断、误导通或影响可靠性等问题,进而可以减小功率半导体器件的开关损耗,提升开关效率;有利于高频、高dv/dt的功率半导体器件在桥臂电路中的应用。

6、另外,该功率半导体器件在片内集成功率晶体管和泄放晶体管,泄放串扰电流的通路设置在功率晶体管的栅源两端,且位于片内,从而能够降低甚至避免片外寄生电感和其他片外元器件对改善桥臂串扰效果的影响,提高功率半导体器件对桥臂串扰问题的改善效果。

7、同时,由于具有上述结构的功率半导体器件能够改善桥臂串扰的问题,因此可以采用较小的栅极负压(绝对值),甚至不用栅极负压进行关断;从而能够改善碳化硅功率半导体器件阈值电压漂移的问题,有利于功率半导体器件的并联使用。

8、在一些实施例中,功率晶体管为金属氧化物半导体场效应晶体管、纵向双扩散金属氧化物半导体场效应晶体管或横向双扩散金属氧化物半导体场效应晶体管;泄放晶体管为金属氧化物半导体场效应晶体管、纵向双扩散金属氧化物半导体场效应晶体管或横向双扩散金属氧化物半导体场效应晶体管。

9、在本技术实施例提供的功率半导体器件中,功率晶体管可以采用多种能够用作功率器件的晶体管,泄放晶体管可以采用多种能够用作控制开关的晶体管,适应性好,能够适配多种不同的应用场景;且功率晶体管和泄放晶体管在工艺上兼容,有利于功率晶体管和泄放晶体管的片内集成。

10、在一些实施例中,功率晶体管为vdmos管;功率半导体器件包括衬底、第一金属层、外延层、栅介质层、栅极层和第二金属层。

11、其中,具有第一掺杂类型的衬底包括第一漏区。

12、第一金属层设置在衬底一侧,第一金属层包括第一漏极,第一漏极与第一漏区接触连接。

13、外延层具有第一掺杂类型;外延层设置在衬底远离第一金属层的一侧;其中,外延层中包括第一阱区和第一漂移区,第一阱区位于外延层中远离衬底的顶部区域,具有第二掺杂类型;第一阱区中包括第一源区和第一沟道区,第一源区具有第一掺杂类型,第一沟道区连接第一漂移区和第一源区;

14、栅介质层设置于外延层远离衬底的一侧。

15、栅极层设置于栅介质层远离衬底的一侧;栅极层包括第一栅极,第一栅极与第一沟道区相对设置。

16、第二金属层设置于外延层远离衬底的一侧,第二金属层包括第一源极、第一连接部和第二连接部;第一源极与第一源区接触连接,第一连接部连接第一栅极和泄放晶体管;第二连接部连接第一源极和泄放晶体管;

17、其中,第一掺杂类型为p型掺杂,第二掺杂类型为n型掺杂;或者,第一掺杂类型为p型掺杂,第二掺杂类型为n型掺杂。

18、在本技术实施例提供的功率半导体器件中,功率晶体管采用vdmos管,vdmos管具有高输入阻抗,低驱动功率,高开关速度,优越的频率特性,低噪声以及很好的热稳定性,抗辐射能力及制造工艺简单等特点;较为适用于功率半导体器件。

19、在一些实施例中,泄放晶体管为ldmos管。

20、在功率半导体器件中,外延层中还包括第二阱区、第二漂移区和第二漏区,第二阱区、第二漂移区和第二漏区位于外延层中远离衬底的顶部区域;第二阱区具有第二掺杂类型,第二漏区和第二漂移区具有第一掺杂类型;第二阱区中包括第二沟道区和具有第一掺杂类型的第二源区,第二源区与第二沟道区接触;第二漂移区连接第二沟道区和第二漏区;

21、栅极层包括第二栅极,第二栅极与第二沟道区相对设置;

22、第二金属层包括第二源极和第二漏极,第一漏极与第一连接部相连,第二漏极与第二连接部相连。

23、在本技术实施例提供的功率半导体器件中,功率晶体管采用vdmos管,泄放晶体管采用ldmos管,ldmos管为电压控制型开关器件,具有易控制,结构简单,能够承受高压、导通电阻小和能够适用高频率等特性。ldmos管与vdmos管工艺兼容,ldmos管中栅极、漏极和源极均位于同一表面,方便与vdmos管连接,有利于与vdmos管实现片内集成。

24、在一些实施例中,泄放晶体管为mos管。

25、在功率半导体器件中,外延层中还包括具有第二掺杂类型的第二阱区,第二阱区位于外延层中远离衬底的顶部区域;第二阱区中包括第二源区、第二沟道区和第二漏区,第二源区和第二漏区具有第一掺杂类型,第二沟道区连接第二源区和第二漏区;

26、栅极层包括第二栅极,第二栅极与第二沟道区相对设置;

27、第二金属层包括第二源极和第二漏极,第二源极和第二漏极中的一方与第一连接部相连,第二源极和第二漏极中的另一方与第二连接部相连。

28、在本技术实施例提供的功率半导体器件中,功率晶体管采用vdmos管,泄放晶体管采用mos管,mos管为电压控制型开关器件,具有结构简单,易控制,开关性能好,与vdmos管工艺兼容等特性,另外,mos管中的栅极、漏极和源极均位于同一表面,方便与vdmos管连接;从而有利于与vdmos管在片内集成。

29、在一些实施例中,功率晶体管为ldmos管;功率半导体器件包括衬底、外延层、栅介质层、栅极层和第二金属层。

30、其中,具有第一掺杂类型的外延层设置在衬底的一侧;外延层中包括第一阱区、第一漂移区和第一漏区,第一阱区、第一漂移区和第一漏区位于外延层中远离衬底的顶部区域,第一漂移区和第一漏区具有第一掺杂类型,第一阱区具有第二掺杂类型;第一阱区中包括第一源区和第一沟道区,第一源区具有第一掺杂类型,第一沟道区连接第一漂移区和第一源区;

31、栅介质层设置于外延层远离衬底的一侧;

32、栅极层设置于栅介质层远离衬底的一侧;栅极层包括第一栅极,第一栅极与第一沟道区相对设置;

33、第二金属层设置于外延层远离衬底的一侧,第二金属层包括第一源极、第一漏极、第一连接部和第二连接部;第一源极与第一源区接触连接,第一漏极与第一漏区接触连接;第一连接部连接第一栅极和泄放晶体管;第二连接部连接第一源极和泄放晶体管;

34、其中,第一掺杂类型为p型掺杂,第二掺杂类型为n型掺杂;或,第一掺杂类型为p型掺杂,第二掺杂类型为n型掺杂。

35、在本技术实施例提供的功率半导体器件中,功率晶体管采用ldmos管,ldmos管具有能够承受高压、导通电阻小和能够适用高频率等特性,且ldmos的结构简单,容易制作,栅极、漏极和源极均位于同一表面,方便功率晶体管与泄放晶体管的连接,有利于功率晶体管与泄放晶体管的片内集成;并且方便功率半导体器件电极的引出。

36、在一些实施例中,泄放晶体管为ldmos管;

37、在功率半导体器件中,外延层中还包括第二阱区、第二漂移区和第二漏区,第二阱区、第二漂移区和第二漏区位于外延层中远离衬底的顶部区域;第二阱区具有第二掺杂类型,第二阱区中包括第二沟道区和具有第一掺杂类型的第二源区,第二源区与第二沟道区接触;第二漏区和第二漂移区具有第一掺杂类型,第二漂移区连接第二阱区中的第二沟道区和第二漏区;

38、栅极层包括第二栅极,第二栅极与第二沟道区相对设置;

39、第二金属层包括第二源极和第二漏极,第一漏极与第一连接部相连,第二漏极与第二连接部相连。

40、在本技术实施例提供的功率半导体器件中,功率晶体管和泄放晶体管均采用ldmos管,两者结构简单,工艺兼容,容易制作,栅极、漏极和源极均位于同一表面,方便功率晶体管与泄放晶体管的连接,从而有利于功率晶体管与泄放晶体管的片内集成;同时有利于在同一面引出功率半导体器件的电极,方便功率半导体器件的连接。另外,ldmos管具有能够承受高压、导通电阻小和能够适用高频率等特性。

41、在一些实施例中,泄放晶体管为mos管;

42、在功率半导体器件中:

43、外延层中还包括具有第二掺杂类型的第二阱区,第二阱区位于外延层中远离衬底的顶部区域;第二阱区中包括第二源区、第二沟道区和第二漏区,第二源区和第二漏区具有第一掺杂类型,第二沟道区连接第二源区和第二漏区;

44、栅极层包括第二栅极,第二栅极与第二沟道区相对设置;

45、第二金属层包括第二源极和第二漏极,第二源极和第二漏极中的一方与第一连接部相连,第二源极和第二漏极中的另一方与第二连接部相连。

46、在本技术实施例提供的功率半导体器件中,功率晶体管采用ldmos管,泄放晶体管采用mos管,mos管为电压控制型开关器件,具有易控制,结构简单,与ldmos工艺兼容等特性,ldmos管和mos管的栅极、漏极和源极均位于同一表面,方便ldmos管和mos管的连接,有利于ldmos管和mos管的片内集成,同时有利于在同一面引出功率半导体器件的电极,方便功率半导体器件的连接。

47、在一些实施例中,功率晶体管和泄放晶体管均为mos管。如此设计,能够进一步简化功率半导体器件的结构,有利于功率半导体器件的制作和尺寸的缩小。

48、在一些实施例中,衬底的半导体材料包括硅、锗、砷化镓、氮化镓、锑化铟、磷化铟、硅锗合金和碳化硅中的至少一种。在本技术实施例提供的功率半导体器件中,衬底可以采用多种不同的半导体材料,适应性好,能够适配多种不同的应用场景。

49、在一些实施例中,衬底和外延层的半导体材料均为碳化硅。

50、在本技术实施例提供的功率半导体器件中,衬底和外延层的半导体材料为碳化硅,功率晶体管和泄放晶体管均为碳化硅晶体管。碳化硅具有宽禁带、高临界击穿电场、高饱和漂移速率等特性;采用碳化硅形成的碳化硅晶体管具有输入阻抗高、开关速度稳定性高、导通电阻低等优点,适合用于高功率和高频应用领域。

51、另外,外延层和衬底采用相同的半导体材料,均为碳化硅,有利于在衬底上采用外延生长方式形成的外延层,能够使外延层与衬底具有较好的界面质量,从而有利于提高功率半导体器件的性能。

52、在一些实施例中,功率半导体器件包括多个功率晶体管和至少一个泄放晶体管。

53、功率晶体管与泄放晶体管一一对应连接;或者,至少两个功率晶体管与同一泄放晶体管连接。

54、在本技术实施例提供的功率半导体器件,功率晶体管与泄放晶体管可以一一对应设置,也可以至少两个功率晶体管共用一个泄放晶体管,具有不同的结构类型,能够适用不同的应用和制作场景。

55、在一些实施例中,功率半导体器件包括多个功率晶体管和至少一个泄放晶体管。

56、功率半导体器件包括多个元胞结构;在至少一个元胞结构中,包括一个功率晶体管和一个泄放晶体管。

57、在本技术实施例提供的功率半导体器件中,泄放晶体管可以集成在功率晶体管的元胞结构中,有利于泄放晶体管和功率晶体管的连接。

58、在一些实施例中,功率半导体器件包括多个功率晶体管和多个泄放晶体管。

59、功率半导体器件包括至少一个第一区域和至少一个第二区域,每个第一区域中设置有多个功率晶体管,每个第二区域中设置有多个泄放晶体管。

60、在本技术实施例提供的功率半导体器件,泄放晶体管和功率晶体管可以分区域集中设置,有利于功率晶体管和泄放晶体管的制作。

61、在一些实施例中,功率晶体管为平面栅或沟槽栅结构;和/或,泄放晶体管为平面栅或沟槽栅结构。在本技术实施例提供的功率半导体器件,功率晶体管和泄放晶体管具有不同的结构类型,能够适用不同的应用和制作场景。

62、第二方面,本技术实施例提供了一种功率器件模组,该功率器件模组包括多个并联的第一方面实施例中任一项的功率半导体器件。

63、第三方面,本技术实施例提供了一种桥臂电路,该桥臂电路包括上桥臂和下桥臂,上桥臂和下桥臂中包括第一方面任一项实施例中所述的功率半导体器件;或,包括第二方面任一项实施例中所述的功率器件模组。

64、第四方面,本技术实施例提供了一种电子设备,该电子设备包括:第一方面任一项实施例中所述的功率半导体器件;第二方面任一项实施例中所述功率器件模组;和/或,第三方面任一项实施例中所述的桥臂电路。

65、本技术实施例所提供的功率器件模组、桥臂电路和电子设备所能够达到的技术效果与上述任一实施例中的功率半导体器件所能够达到的技术效果相同,在此不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!