提高器件抗浪涌能力的SGTMOSFET结构、方法及结构制备方法与流程

本发明属于mosfet领域,具体涉及一种提高器件抗浪涌能力的sgt mosfet结构、方法及sgt mosfet结构制备方法。

背景技术:

1、由于sgt mosfet内阻较低,开关速度较快,可以使电源系统效率大幅提升,因此,sgt(屏蔽栅)mosfet被广泛应用在消费电子、工业控制以及汽车电子等领域。但在一些特殊应用中,如热插拔电路,在sgt mosfet导通工作时电源系统会突然出现高的浪涌电流,此时的浪涌电流很容易导致sgt mosfet过流烧坏,从而降低整个电源系统的可靠性。

技术实现思路

1、本发明的目的在于解决sgt mosfet导通时电源系统突然出现高的浪涌电流,导致sgt mosfet过流烧坏进而降低整个电源系统可靠性低的技术问题,从而提供一种提高器件抗浪涌能力的sgt mosfet结构、方法及结构制备方法。

2、为了实现上述目的,本发明的技术解决方案为:

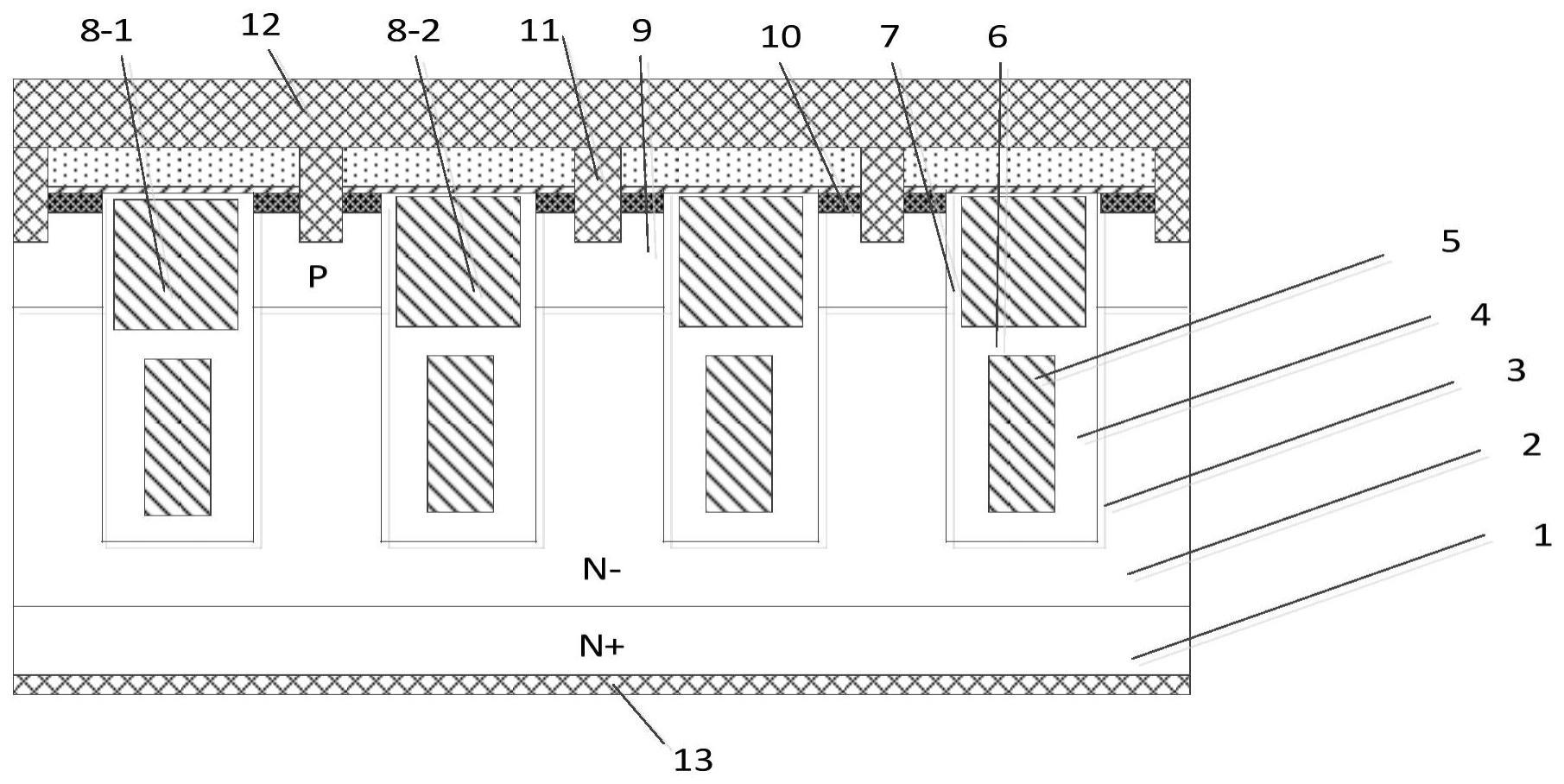

3、一种提高器件抗浪涌能力的sgt mosfet结构,其特殊之处在于,包括衬底;

4、位于衬底上表面的外延层;

5、位于外延层上表面的k个沟槽,k为大于等于2的整数;

6、位于k个沟槽内表面相应的k个底部氧化层,也称厚氧化层;所述底部氧化层为凹槽结构;

7、位于k个底部氧化层凹槽结构内相应的k个源极多晶,所述源极多晶的上表面低于底部氧化层的上表面;

8、位于k个底部氧化层上表面的k个中间氧化层;

9、位于k个中间氧化层上表面相应的k个栅氧化层,所述栅氧化层为凹槽结构;所述k个中间氧化层和k个栅氧化层均位于相应的沟槽内;

10、分别位于k个栅氧化层凹槽结构内相应的m个第一栅极和(k-m)个第二栅极,其中,m个第一栅极之间电连接,(k-m)个第二栅极之间电连接,且m个第一栅极和(k-m)个第二栅极呈比例交错设置;

11、位于k个栅氧化层两侧的(k+1)个阱区,所述阱区的底部不低于第一栅极和第二栅极的底部;

12、位于阱区上表面的源区;

13、位于源区、第一栅极和第二栅极上表面的介质层;

14、位于介质层上且对应各源区的(k+1)个源极接触孔,所述源极接触孔的下端与相应的阱区接触;

15、位于介质层上表面且与源极接触孔连接的源极;

16、以及位于衬底下表面的漏极。

17、进一步地,所述衬底、源区为n+型,外延层为n-型,阱区为p型;

18、或者,所述衬底、源区为p+型,外延层为p-型,阱区为n型。

19、进一步地,所述m:(k-m)=1:1,或者m:(k-m)=1:2,或者m:(k-m)=1:3。

20、进一步地,所述介质层包括由上至下设置的bpsg层和usg层。

21、基于上述的一种提高器件抗浪涌能力的sgt mosfet结构,本发明还提供了一种提高器件抗浪涌能力的方法,其中,m个所述第一栅极与其对应的源极和漏极构成第一mos管m1,(k-m)个所述第二栅极与其对应的源极和漏极构成第二mos管m2,其特殊之处在于,包括以下步骤:

22、1】将第一mos管m1和第二mos管m2并联设置;

23、2】通电后监测当前是否存在浪涌电流;

24、若不存在浪涌电流,则控制第一mos管m1完全导通,第二mos管m2不完全导通或者关断,或者,控制第二mos管m2完全导通,第一mos管m1不完全导通或者关断。

25、基于上述的一种提高器件抗浪涌能力的sgt mosfet结构,本发明还提供了一种提高器件抗浪涌能力的sgt mosfet结构的制备方法,其特殊之处在于,包括以下步骤:

26、1】在衬底上层叠外延层;

27、2】在外延层上表面定义出沟槽区域;再在沟槽区域定义出k个沟槽,k为大于等于2的整数;

28、3】在外延层上表面、k个沟槽的底部及侧壁上制备一体的氧化层,使其在沟槽内形成凹槽结构的底部氧化层;

29、4】在底部氧化层的上部及其沟槽结构内整体淀积多晶硅,然后对淀积的多晶硅进行回刻,去除底部氧化层上部的多晶硅,且将底部氧化层凹槽结构内的多晶硅进行回刻形成k个源极多晶;

30、5】去除高于源极多晶的底部氧化层,并在源极多晶和底部氧化层的上表面制备中间氧化层;

31、6】在中间氧化层的上表面和对应沟槽的两侧侧壁上制备一体的氧化层,使其形成凹槽结构的栅氧化层;再在栅氧化层上部及其沟槽结构内整体淀积多晶硅,然后对淀积的多晶硅进行回刻,在k个栅氧化层凹槽结构内形成相应的m个第一栅极和(k-m)个第二栅极,所述m个第一栅极和(k-m)个第二栅极呈比例交错设置;

32、7】对外延层进行第一类型离子注入工艺,后热退火形成阱区;

33、8】在外延层上对应阱区的位置定义出源极注入区域,对源极注入区域的外延层进行第二类型离子注入工艺,后热退火形成源区;再在整个外延层上表面制备介质层;

34、9】在介质层上对应源区的位置刻蚀出源极接触孔,再在源极接触孔内进行第二类型离子注入,并在介质层表面制备相应金属层,形成源极;在衬底下表面制备相应金属层,形成漏极,完成提高器件抗浪涌能力的sgt mosfet结构的制备。

35、进一步地,所述衬底为n+型,外延层为n-型,第一类型离子为p型,第二类型离子为n型;

36、或者衬底为p+型,外延层为p-型,第一类型离子为n型,第二类型离子为p型。

37、进一步地,步骤6】中,所述形成的第一栅极的数量和第二栅极的数量比值满足:

38、m:(k-m)=1:1,或者m:(k-m)=1:2,或者m:(k-m)=1:3。

39、进一步地,步骤1】中,所述衬底为n+型,在衬底上层叠n-型外延层(2);

40、步骤2】中,通过光刻工艺在外延层上表面定义出mosfet的沟槽区域;再通过干法蚀刻工艺对沟槽区域进行刻蚀定义出k个沟槽;

41、步骤3】中,通过热氧化工艺在外延层上表面、k个沟槽的底部及侧壁上生长形成厚度为200nm-600nm的底部氧化层;

42、步骤4】中,通过干法蚀刻工艺对淀积的多晶硅进行回刻,回刻深度为0.8-1.7μm;

43、步骤5】中,通过化学气相工艺淀积厚度为200nm-400nm的氧化层,再回刻形成厚度为150nm-250nm的中间氧化层;

44、步骤6】中,通过热氧化工艺在中间氧化层上表面和对应沟槽的两侧侧壁上生长一层厚度为20nm-100nm的氧化层;再通过湿法蚀刻工艺对氧化层进行去除,之后进行第二次热氧化工艺,在中间氧化层上表面和对应沟槽的两侧侧壁上生长形成厚度为60nm-100nm的栅氧化层;本发明中的厚度均表示相应氧化层的高度;

45、步骤7】中,对外延层进行硼离子注入工艺,后再进行热退火形成p型阱区;其中硼离子的能量在100-180kev,注入剂量为0.8e12-1.3e13;

46、步骤8】中,通过光刻工艺在外延层上对应阱区的位置定义出源极注入区域;再对源极注入区域的外延层进行砷离子注入工艺,形成n+型源区,然后再进行热退火;其中砷离子的能量为60-100kev,注入剂量为4e15-8e15;再通过化学气相淀积工艺依次淀积usg层和bpsg层;

47、步骤9】中,通过干法蚀刻工艺在bpsg层和usg层上对应源区的位置刻蚀出源极接触孔,在源极接触孔内进行砷离子注入,并填充金属钨和铝铜,同时在bpsg层上设置金属钨和铝铜,形成源极。

48、本发明相比于现有技术的有益效果为:

49、1、本发明提供的提高器件抗浪涌能力的sgt mosfet结构,将sgt mosfet的栅极进行分区,分为第一栅极和第二栅极,第一栅极和第二栅极呈比例交错设置,在不增大器件尺寸的基础上,通过控制第一栅极和第二栅极中的一个完全导通,另外一个不完全导通或关断,以降低通过sgt mosfet的电流,从而防止sgt mosfet导通时系统突然出现高的浪涌电流对电源系统的损坏,在不增大器件内阻的情况下大大提高了电源系统的可靠性,可以广泛应用在热插拔这类特殊应用的系统中。

50、2、本发明基于上述提高器件抗浪涌能力的sgt mosfet结构,提供的提高器件抗浪涌能力的方法为:当不存在浪涌电流时,通过控制第一mos管m1和第二mos管m2完全导通,使二者均工作在饱和状态下,源极与漏极之间电流不再变化,使得第一mos管m1和第二mos管m2都具有较低的导通电阻,大大降低了损耗;当存在浪涌电流时,通过控制第一mos管m1和第二mos管m2中的一个mos管完全导通,另一个mos管不完全导通或者关断,不完全导通的mos管导电沟道宽度变窄,导通电阻增大,降低通过mos管的电流,减小通过器件的电流密度,避免通过sgt mosfet的电流过大而导致器件失效,保证了电源系统的可靠性。

51、3、本发明提供的提高器件抗浪涌能力的sgt mosfet结构的制备方法,操作简单方便,且可靠性高。

- 还没有人留言评论。精彩留言会获得点赞!