半导体结构及其制造方法与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构及其制造方法。

背景技术:

1、随着半导体结构的器件特征尺寸发展进入深纳米级别,一些物理问题逐渐凸出,例如:半导体结构的性能降低,量子效应影响、薄栅氧化层的可靠性以及迁移率退化等。为解决这些问题,人们改进工艺提出应变si/sige技术。应变si/sige技术能够使载流子迁移率提高,进而使得器件性能得到提升。

2、然而,这样的结构也致使栅致漏极泄漏效应(gidl,gate-induced drainleakage)和栅极直接隧穿(gdt,gate direct tunneling)这两种漏电机制加重,从而产生超出期望的静态漏电。其中,栅致漏极泄漏效应包括两种遂穿物理机制:横向带带遂穿(transverse band-to-band tunneling,t-btbt)和纵向带带遂穿(longitude band-to-band tunneling,l-btbt)。

技术实现思路

1、本公开实施例提供一种半导体结构及其制造方法,至少有利于在增加nmos器件和pmos器件的沟道载流子迁移率的同时,减小nmos器件以及pmos器件的漏电流。

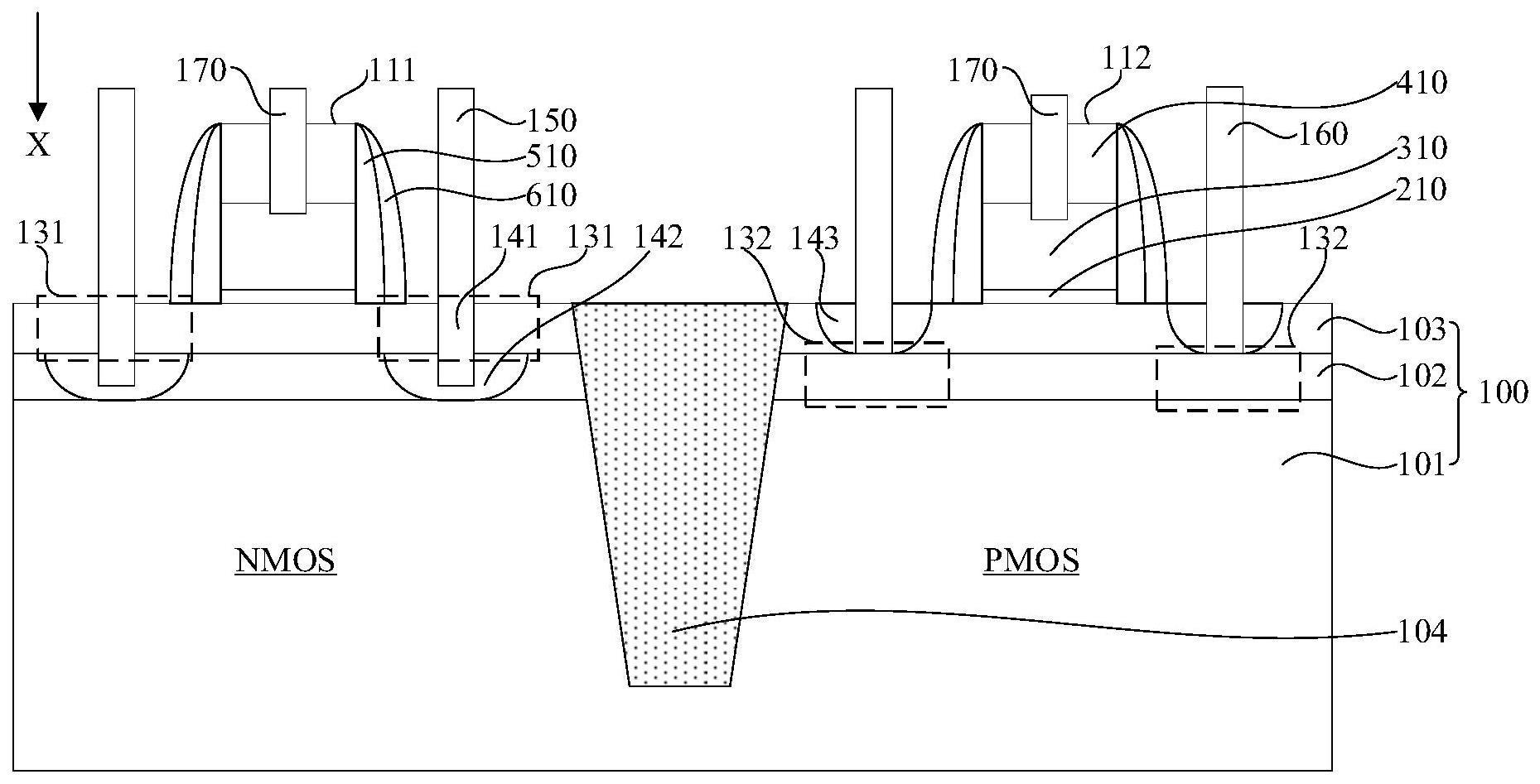

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构,包括:基底,所述基底包括依次层叠的衬底、第一半导体层以及第二半导体层,所述第一半导体层的材料的晶格常数大于所述第二半导体层的材料的晶格常数,所述基底包括nmos区以及pmos区;第一栅极和第二栅极,所述第一栅极位于所述基底的所述nmos区上,所述第二栅极位于所述基底的所述pmos区上;第一源漏掺杂区,位于所述第一栅极两侧的所述第二半导体层内;第二源漏掺杂区,位于所述第二栅极两侧的所述第一半导体层内;相连通的第一开口和第二开口,所述第一开口位于所述第一源漏掺杂区内且沿第一方向贯穿所述第一源漏掺杂区,所述第二开口位于所述第一源漏掺杂区正下方且沿所述第一方向以及第二方向贯穿所述第一半导体层,其中,所述第一方向为垂直于所述衬底表面的方向,所述第二方向为平行于所述衬底表面的方向;第三开口,位于所述第二源漏掺杂区正上方且沿所述第一方向以及所述第二方向贯穿所述第二半导体层;第一电连接部,填充满所述第一开口且与所述第一源漏掺杂区电接触;第二电连接部,至少位于所述第三开口内且与所述第二源漏掺杂区电接触。

3、在一些实施例中,第一介质层,位于所述第二开口内,且电隔离所述衬底与所述第一电连接部;第二介质层,位于所述第三开口内,且电隔离所述第二半导体层与所述第二电连接部。

4、在一些实施例中,还包括:第四开口,所述第四开口与所述第三开口相连通,所述第四开口位于所述第二源漏掺杂区内且沿所述第一方向贯穿所述第二源漏掺杂区,且在平行于所述衬底表面的剖面方向上,所述第四开口的剖面面积小于所述第三开口的剖面面积;所述第二电连接部还位于至少部分所述第四开口内,且覆盖至少部分所述第一半导体层朝向所述第四开口的侧壁。

5、在一些实施例中,所述第一半导体层的材料包括锗化硅;所述第二半导体层的材料包括硅。

6、在一些实施例中,位于所述nmos区的所述第一半导体层邻近所述第二半导体层的区域中锗离子的浓度为第一浓度,位于所述nmos区的所述第一半导体层邻近所述衬底的区域中锗离子的浓度为第二浓度,所述第一浓度大于所述第二浓度

7、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构的制造方法,包括:形成基底,所述基底包括依次层叠的衬底、第一半导体层以及第二半导体层,所述第一半导体层的材料的晶格常数大于所述第二半导体层的材料的晶格常数,所述基底包括nmos区以及pmos区;形成第一栅极以及第二栅极,所述第一栅极位于所述基底的所述nmos区上,所述第二栅极位于所述基底的所述pmos区上;形成第一源漏掺杂区和第二源漏掺杂区,所述第一源漏掺杂区位于所述第一栅极两侧的所述第二半导体层内,所述第二源漏掺杂区位于所述第二栅极两侧的所述第一半导体层内;形成相连通的第一开口和第二开口,所述第一开口位于所述第一源漏掺杂区内且沿第一方向贯穿所述第一源漏掺杂区,所述第二开口位于所述第一源漏掺杂区正下方且沿所述第一方向以及第二方向贯穿所述第一半导体层,其中,所述第一方向为垂直于所述衬底表面的方向,所述第二方向为平行于所述衬底表面的方向;形成第三开口,位于所述第二源漏掺杂区正上方且沿所述第一方向以及所述第二方向贯穿所述第二半导体层;形成第一电连接部和第二电连接部,所述第一电连接部填充满所述第一开口且与所述第一源漏掺杂区电接触,所述第二电连接部至少位于所述第三开口内且与所述第二源漏掺杂区电接触。

8、在一些实施例中,形成所述基底的步骤包括:提供依次层叠的衬底、第一初始半导体层以及掩膜层,所述掩膜层仅覆盖所述pmos区的所述第一初始半导体层表面;对位于所述nmos区的所述第一初始半导体层进行氧化处理,以形成氧化层;去除所述掩膜层以及所述氧化层。

9、在一些实施例中,形成所述第一开口以及所述第二开口的步骤包括:进行第一干法刻蚀,至少去除部分所述第一半导体层以及部分所述第二半导体层,形成所述第一开口以及位于所述第一开口正下方的第二初始开口;进行第一湿法刻蚀,对所述第二初始开口露出的所述第一半导体层进行刻蚀,以形成所述第二开口。

10、在一些实施例中,形成所述第三开口的步骤包括:进行第二干法刻蚀,所述第二干法刻蚀至少去除部分所述第二半导体层,形成第三初始开口,所述第三初始开口位于所述第二源漏掺杂区正上方的所述第二半导体层内;进行第二湿法刻蚀,对所述第三初始开口露出的所述第二半导体层进行刻蚀,以形成所述第三开口。

11、在一些实施例中,所述形成第三开口后,还包括:向所述第一开口和所述第二开口中填充第一初始介质层;向所述第三开口中填充第二初始介质层;刻蚀去除位于所述第一开口内的所述第一初始介质层以及位于所述第二开口和所述第三开口内的部分所述第二初始介质层,刻蚀后的所述第一初始介质层为第一介质层,刻蚀后的所述第二初始介质层为第二介质层。

12、本公开实施例提供的技术方案至少具有以下优点:

13、本公开实施例提供的半导体结构的技术方案中,基底包括依次层叠的衬底、第一半导体层以及第二半导体层,第一半导体层的晶格常数大于第二半导体层的晶格常数,基底包括nmos区和pmos区;位于nmos区上的第一栅极以及位于pmos区上的第二栅极;第一源漏掺杂区,位于第一栅极两侧的第二半导体层内;第二源漏掺杂区,位于第二栅极两侧的第一半导体层内;相连通的第一开口和第二开口,第一开口位于第一源漏掺杂区内且贯穿第一源漏掺杂区,第二开口位于第一源漏掺杂区正下方且贯穿第一半导体层;第三开口,位于第二源漏掺杂区上方且贯穿第二半导体层;第一电连接部,填充满第一开口且与第一源漏掺杂区电接触;第二电连接部,至少位于第三开口内且与第二源漏掺杂区电接触。在相关技术中,半导体结构中包括基底、第一源漏掺杂区、第二源漏掺杂区以及第一电连接部和第二电连接部,而并不具有第一开口、第二开口以及第三开口。本公开实施例提供的半导体结构中,位于nmos区源漏区域内的第一半导体层中具有第二开口,第二开口贯穿第一半导体层,位于pmos区源漏区域内的第二半导体层具有第三开口,第三开口贯穿第二半导体层。这种结构能够在增加nmos器件和pmos器件的沟道载流子迁移率的同时,还减小nmos器件以及pmos器件的减小半导体结构中的漏电流。

- 还没有人留言评论。精彩留言会获得点赞!