一种沟槽型原胞功率器件制备方法和沟槽型原胞功率器件与流程

本发明涉及功率器件领域,具体涉及一种沟槽型原胞功率器件的制备方法及该制备方法制得的沟槽型原胞功率器件。

背景技术:

1、igbt、mosfet等功率器件作为必需的开关器件广泛应用在变频器和逆变器等电路结构中。沟槽型原胞功率器件的结构经历了外延型、pt型、npt型、沟槽+fs型等数个代别的发展,随着其结构变化,功率器件的性能得到不断优化和提升,其静态损耗和关断损耗都不断的减小,功率密度也随之不断提高。

2、现有技术发展至今在诸多技术层面已经达到瓶颈,在某些方面也表现出了一些不足。如图1所示,主流igbt和mosfet等功率器件的正面原胞结构大都已经采用槽栅型原胞结构,因为槽栅型原胞结构的功率器件相比早期的平面型(planar)原胞结构,具有垂直于芯片表面的纵向沟道,能够大幅提高芯片的电流密度。

3、槽栅型原胞结构的功率器件的栅极形成步骤包括如下:

4、在硅基表面刻蚀出密集的沟槽分布;

5、经过氧化工艺在沟槽和硅基表面形成一层致密的氧化层作为栅氧层;

6、淀积一层低阻高掺杂多晶硅材料,并填充沟槽形成原胞内的栅极;

7、通过刻蚀表面多晶硅淀积层形成如图1所示的横纵交叉的叉指图形,叫做栅极总线gatebus或者gatefinger或者栅极汇流条等。沟槽与栅极总线gatebus相连,gatebus又最终汇流到栅极pad。形成完整的栅极布线与连接;

8、在芯片表面淀积一层氧化层,作为绝缘钝化层,把已经形成的栅极布线覆盖;

9、在栅极区和源极区开通孔,以备和金属层连接;

10、以溅射或蒸镀的形式在芯片表面淀积一层金属,通过通孔以连接到内部原胞的相关电极;

11、刻蚀金属,形成栅极和源极的电气隔离,形成栅极和源极(也称发射极);如图2所示。

12、本发明最接近技术是pitch在6um以上工艺平台上的沟槽trench型igbt与mosfet芯片制备技术。如图3所示,栅极汇流条基本上是由淀积的多晶硅刻蚀后形成的多晶硅汇流条,trench与多晶硅汇流条相连,多晶硅汇流条又最终汇流到栅极pad,形成完整栅极布线与连接。由于pitch较大,trench和trench的间距也比较大,栅极和源极的版图布线和电气隔离很容易实现。

13、随着功率器件加工工艺能力的进步和加工精度的提高,为了进一步提高igbt的功率密度,原胞的密度越来越高,单个pitch已经能够做到3um以下,已有2.4um,1.6um,甚至1.2um的工艺平台。按照传统工艺路线和设计方法就会在栅极与源极分界出处现一系列的问题。

14、如图4所示,现有工艺中设计规则要求多晶硅层对槽栅的覆盖最少要达到2um,这样能够保证在实际的多晶硅刻蚀工艺后即便有些过刻,依然能够保证多晶硅对trench的覆盖与良好连接。然而,上图中的槽栅间距已经小于2um,导致图4中至少有一条trench沟槽001无法与栅极拐角处的多晶硅相连,因为,即便是从版图上将trench连接到栅极拐角处多晶硅层,也将导致多晶硅层对槽栅的覆盖小于2um的最低要求,在多晶硅刻蚀环节,容易造成实际的虚接,断接等问题。芯片可能会产生漏电、短路、可靠性差等各类无法预知问题。如果如图4一样,干脆把trench不接到多晶硅层上,那么就会产生trench的一端电位浮空,会导致浮空侧原胞不能正常开启,同样会导致芯片产生闩锁问题以及热失效等系列可靠性问题。

15、综上,现有多晶硅汇流条工艺与版图设计方式在原胞密度较高的igbt和mosfet设计中遇到了难以突破的瓶颈。

技术实现思路

1、本发明的目的是提供一种沟槽型原胞功率器件的制备方法及该制备方法制得的沟槽型原胞功率器件,以克服现有技术中存在的上述诸多不足,简化工艺、提高芯片利用效率。

2、为实现上述发明目的,本发明的技术方案如下:

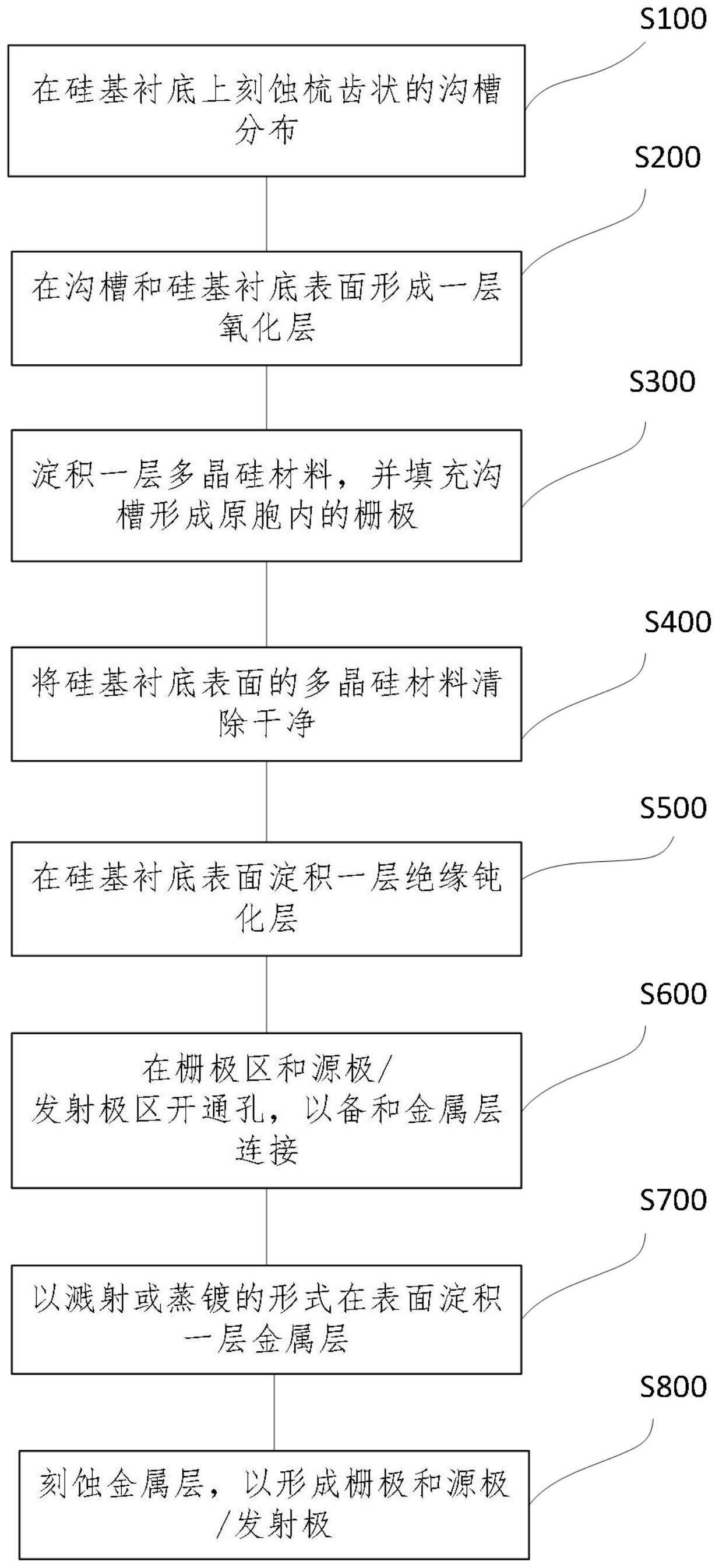

3、本发明的第一方面提供了一种沟槽型原胞功率器件的制备方法,包括如下步骤:

4、在硅基衬底上刻蚀梳齿状的沟槽分布;

5、经过氧化工艺在沟槽和硅基衬底表面形成一层氧化层作为栅极氧化层;

6、淀积一层多晶硅材料,并填充沟槽形成原胞内的栅极;

7、通过湿法腐蚀或研磨工艺,将硅基衬底表面的多晶硅材料和氧化层清除干净;

8、在硅基衬底表面淀积一层绝缘钝化层;

9、在栅极区和源极/发射极区开通孔,以备和金属层连接;

10、以溅射或蒸镀的形式在表面淀积一层金属层,通过通孔可连接到内部原胞的相关电极;

11、刻蚀金属层,形成栅极和源极/发射极;

12、其中,栅极和源极/发射极为双j互锁型形状,即栅极或源极/发射极主体两端向同一侧突出,且栅极和源极/发射极的突出方向相向。

13、进一步的,所述在硅基衬底1上刻蚀梳齿状的沟槽分布包括:

14、采用激光刻蚀工艺在硅基衬底1上刻蚀出梳齿状的沟槽;沟槽的宽度为0.5um-0.6um,深度为4um-5um,沟槽的间距为1um左右。

15、进一步的,所述沟槽的长度延伸为同时被栅极金属层和源极/发射极金属层覆盖,以便在栅极金属层和/或源极/发射极金属层下方的沟槽中开通孔,以供选择为将其通孔连接至栅极金属层或源极/发射极金属层。

16、进一步的,部分覆盖于栅极金属层和/或源极/发射极金属层突出短边的沟槽同时向两端延伸,以被栅极金属层和/或源极/发射极金属层的突出长边覆盖。

17、进一步的,所述沟槽分别连接于栅极、源极/发射极或者浮空。

18、进一步的,根据输入电容设置所述连接于栅极、源极/发射极的沟槽数量比例以及排列规则。

19、本发明的第二方面提供了一种沟槽型原胞功率器件,包括硅基衬底;

20、所述硅基衬底上刻蚀有梳齿状的沟槽;

21、所述沟槽表面上形成有氧化层,沟槽中填充有多晶硅;

22、还包括钝化层,形成在所述硅基衬底和沟槽表面上;

23、还包括金属层,所述金属层被刻蚀形成栅极和源极/发射极,通过通孔连接到内部原胞的相关电极;

24、其中,栅极和源极/发射极为双j互锁型形状,即栅极或源极/发射极主体两端向同一侧突出,且栅极和源极/发射极的突出方向相向。

25、进一步的,所述沟槽的长度延伸为同时被栅极金属层和源极/发射极金属层覆盖,以便在栅极金属层和/或源极/发射极金属层下方的沟槽中开通孔,以供选择为将其通孔连接至栅极金属层或源极/发射极金属层。

26、进一步的,部分覆盖于栅极金属层和/或源极/发射极金属层突出短边的沟槽同时向两端延伸,以被栅极金属层和/或源极/发射极金属层的突出长边覆盖。

27、进一步的,所述沟槽分别连接于栅极、源极/发射极或者浮空;根据输入电容设置所述连接于栅极、源极/发射极的沟槽数量比例以及排列规则。

28、综上所述,本发明提供了一种沟槽型原胞功率器件的制备方法和沟槽型原胞功率器件,本发明通过将金属层直接与多晶硅连接,提高了栅极汇流条的综合电导率,使得功率器件的栅极信号能够无损传导到各个原胞;且本发明采用双j型互锁式版图布线方式,解决了现有技术中高密度沟槽功率器件版图布局上容易造成虚接、断接的情况。

29、与现有技术相比,本发明的有益效果在于:

30、1、本发明在igbt/mosfet等功率器件的制备工艺中,采用金属栅极汇流条工艺,替代了现有多晶硅栅极汇流条工艺,提高了栅极汇流条的综合电导率,使得功率器件的栅极信号能够几乎无损传导到各个原胞;芯片表面各个区域的原胞开启均流性大大提高,使得更大面积的芯片制备成为可能;芯片工作时的热量均匀分布,大大提高了芯片的可靠性。

31、2、本发明采用将金属层与各原胞电极直接相连的原理,金属层和原胞结构层中间间隔一层氧化隔离层,只需将原胞对应电极位置直接开通孔就能与金属电极直接相连。结构与层次更简单,连通效率更高。而现有技术还有一层栅极多晶硅层。金属与原胞层之间有:金属层,氧化层,多晶硅层,氧化层,原胞结构层等。层次复杂,布线复杂,连通效率低。

32、3、本发明提出一种双j型互锁式版图布线方式,解决现有技术对包含高密度trench型功率器件版图布局上遇到容易造成虚接、断接的问题。

- 还没有人留言评论。精彩留言会获得点赞!