一种抗单粒子烧毁的氮化镓基准垂直沟槽MOSFET器件结构及其制造方法

本发明属于半导体功率器件及制造,特别涉及一种抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构及其制造方法。

背景技术:

1、能源消费的激增使得对用于发电、运输和用电的高效电力电子设备的需求日益增长。硅基器件在传统的电力电子应用中较为常用,然而宽带隙半导体如氮化镓更有效,因此,氮化镓在未来的能源应用中显得更为有效。在众多的垂直器件结构中,氮化镓基准垂直沟槽mosfet是一种具有吸引力的器件结构,准垂直结构的特点使得其具有更高的成本效益及更容易与其他器件(如sbd,led等)集成,且其非常适合于高压、高功率密度功率转换器的地面和空间应用。然而,氮化镓功率mosfet在遭受重离子辐射时,可能会发生灾难性故障,例如单粒子栅穿(segr)或单粒子烧毁(seb)。seb的发生依赖于mosfet器件结构中寄生bjt的开启,该bjt结构由重离子入射产生的电子空穴对在源漏偏压下的移动产生的短暂瞬态电流打开,由于再生反馈机制,bjt中的集电极电流增加到第二次击穿开始的点,在源极和漏极之间创造了一个永久的短路,使mosfet失效。

技术实现思路

1、为了克服上述现有技术的缺点,本发明的目的在于提供一种抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构及制造方法,引入额外的空穴泄露路径,增强抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构抗单粒子烧毁性能。

2、为了实现上述目的,本发明采用的技术方案是:

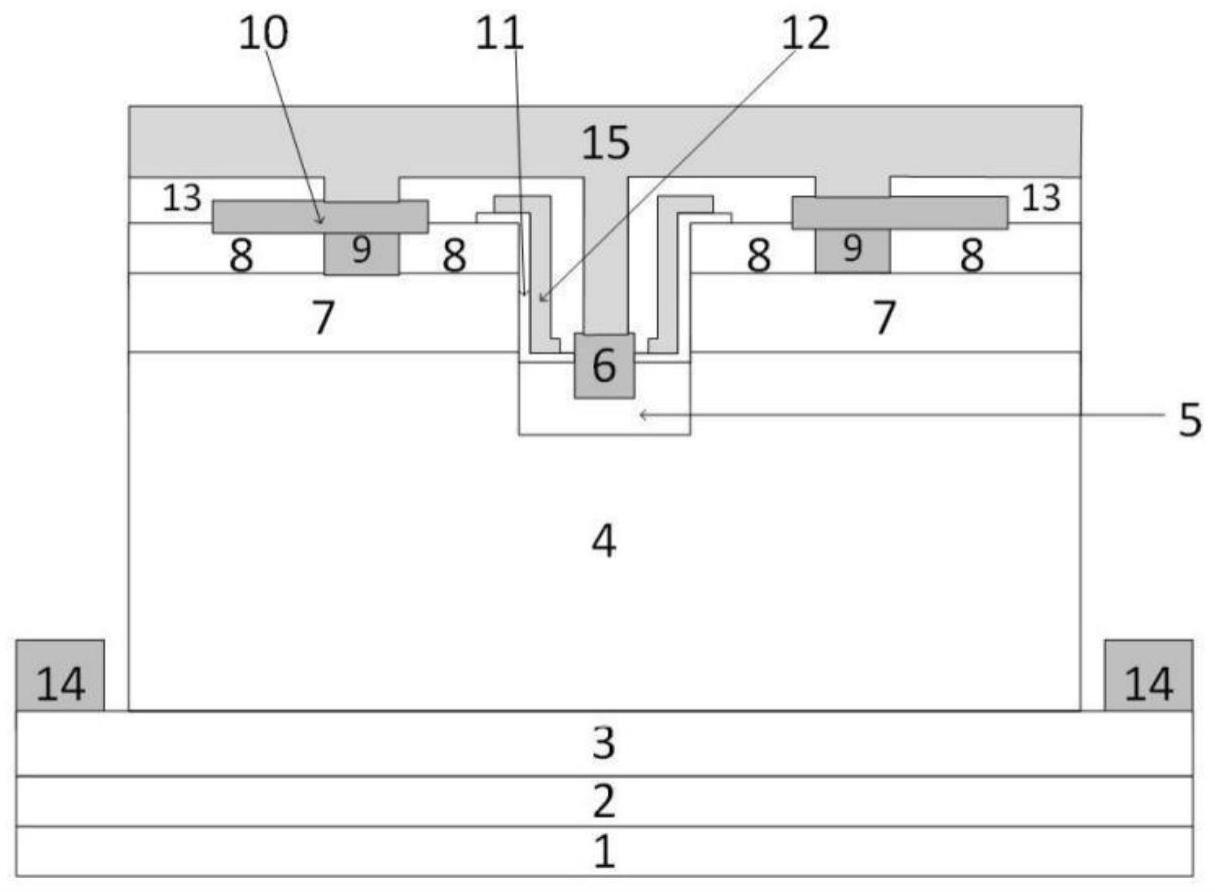

3、一种抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构,包括依次设置的衬底层、复合缓冲层、漏极重掺杂n+型氮化镓层、低掺杂n-型氮化镓漂移层、p型基区层和源极重掺杂n+型氮化镓层,漏电极设置在所述漏极重掺杂n+型氮化镓层远离所述复合缓冲层的一面,在所述低掺杂n-型氮化镓漂移层远离所述漏极重掺杂n+型氮化镓层的一面,设置有与栅极沟槽对应的栅下p型氮化镓区,所述栅极沟槽的槽底设置有栅下金属,槽壁或槽壁与槽底设置栅介质;所述源极重掺杂n+型氮化镓层中设置与所述p型基区层接触的p型基区接触金属,所述栅介质上设置栅电极,所述p型基区接触金属和所述源极重掺杂n+型氮化镓层均与源电极接触,所述源电极与所述栅下金属通过互联金属层进行互联。

4、在一个实施例中,所述低掺杂n-型氮化镓漂移层设置在所述漏极重掺杂n+型氮化镓层的中间,两处漏电极对称布置于所述低掺杂n-型氮化镓漂移层的两侧;所述栅下p型氮化镓区设置在所述低掺杂n-型氮化镓漂移层的中间,所述栅下金属设置在所述栅极沟槽的中间,所述栅介质、所述p型基区层以及所述源极重掺杂n+型氮化镓层均关于所述栅下金属对称布置;所述栅极沟槽两侧的源极重掺杂n+型氮化镓层分别布置有一处p型基区接触金属。

5、在一个实施例中,所述栅极沟槽深度为600nm-1um;所述源极重掺杂n+型氮化镓层上开有p基区凹槽,所述p型基区接触金属布置于所述p基区凹槽中,所述p基区凹槽的深度为200nm-500nm;所述源极重掺杂n+型氮化镓层、p型基区层和低掺杂n-型氮化镓漂移层与所述漏极重掺杂n+型氮化镓层形成台阶结构,所述漏电极布置于台阶结构的台阶面,所述台阶结构高度即源极重掺杂n+型氮化镓层、p型基区层和低掺杂n-型氮化镓漂移层的总厚度为1.5um-15um。

6、在一个实施例中,所述衬底层,材料为sic或si或sapphire,厚度为100-1500μm;所述复合缓冲层包括成核层、过渡层与复合缓冲层;成核层材料为aln,厚度为50-300nm;过渡层材料为al组分变化的algan,或algan/gan超晶格,厚度为100nm-1μm;缓冲层材料为gan或者algan,厚度为100nm-10μm。

7、在一个实施例中,所述漏极重掺杂n+型氮化镓层的材料为重掺杂n型gan,掺杂浓度为1×1018-5×1018cm-3,厚度为100-600nm;

8、所述低掺杂n-型氮化镓漂移层的材料为轻掺杂n型gan,掺杂浓度为1×1015-5×1016cm-3,厚度为1-20μm;

9、所述栅下p型氮化镓区的材料为重掺杂p型gan,掺杂浓度为5×1018-5×1019cm-3,厚度为200-600nm;

10、所述p型基区层的材料为重掺杂p型gan,掺杂浓度为5×1018-5×1019cm-3,厚度为0.3-1μm;

11、所述源极重掺杂n+型氮化镓层的材料为重掺杂n型gan,掺杂浓度为1×1018-5×1018cm-3,厚度为300-600nm。

12、在一个实施例中,所述栅下金属设置在栅下p型氮化镓区的表面或者嵌入所述栅下p型氮化镓区形成欧姆接触;所述栅介质设置在栅下p型氮化镓区的表面并沿所述栅极沟槽侧壁延伸至所述源极重掺杂n+型氮化镓层,所述栅电极与栅介质以及所述栅极沟槽侧壁形成mos结构;所述源电极与源极重掺杂n+型氮化镓层形成欧姆接触;所述漏电极与漏极重掺杂n+型氮化镓层形成欧姆接触;所述p型基区接触金属与p型基区层形成欧姆接触。

13、在一个实施例中,所述栅下p型氮化镓区通过离子注入和扩散形成,所述栅介质为通过沉积形成的sio2或al2o3绝缘层。

14、在一个实施例中,所述互联金属层与源极重掺杂n+型氮化镓层之间,以及与栅电极之间,均布设有钝化层。

15、本发明还提供了所述抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构的制造方法,包括如下步骤:

16、s1:在衬底层上依次生长复合缓冲层、漏极重掺杂n+型氮化镓层和低掺杂n-型氮化镓漂移层;

17、s2:在低掺杂n-型氮化镓漂移层远离漏极重掺杂n+型氮化镓层的一面,通过离子注入以及扩散,形成栅下p型氮化镓区;

18、s3:在栅下p型氮化镓区形成后,按s1生长次序,继续生长p型基区层和源极重掺杂n+型氮化镓层;

19、s4:对源极重掺杂n+型氮化镓层刻蚀出p基区凹槽,对源极重掺杂n+型氮化镓层和p型基区层刻蚀出栅极沟槽,对源极重掺杂n+型氮化镓层、p型基区层和低掺杂n-型氮化镓漂移层刻蚀出台阶结构;

20、s5:在所述p基区凹槽上制备p型基区接触金属;

21、s6:在所述台阶结构的台阶面,即漏极重掺杂n+型氮化镓层上制备漏电极,形成欧姆接触;在源极重掺杂n+型氮化镓层和p型基区接触金属上制备源电极,形成欧姆接触;

22、s7:在所述栅极沟槽沉积一层栅介质;

23、s8:覆盖所述栅极介质制备栅电极;

24、s9:在栅介质与栅下p型氮化镓区的接触位置开孔制备栅下金属,形成欧姆接触;

25、s10:利用互联金属层连接源电极与栅下金属。

26、在一个实施例中,所述s2,通过镁离子注入以及扩散,形成栅下p型氮化镓区;所述s9与s10之间,先在器件表面沉积一层钝化层,然后在源电极以及栅下金属处开孔,利用互联金属层形成互联。

27、与现有技术相比,本发明的有益效益在于:

28、1、本发明提供的一种抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构,在基础的抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构上引入栅极下方的栅下p型氮化镓区,为重离子入射后产生的空穴提供了额外的泄露路径,实现了抗单粒子烧毁性能的提高。

29、2、本发明提供的一种抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构,保持了基础准垂直沟槽mosfet的结构,且引入的栅下p型氮化镓区还可以缓解沟槽附近拥挤的电场,因此提高了击穿电压,避免了新结构对器件原有特性的破坏。

30、3、本发明相比较于现有的抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构,仅增加离子注入和扩散工艺,在工艺难度和制造成本增加有限的情况下,做到了有效提升抗单粒子烧毁的氮化镓基准垂直沟槽mosfet器件结构的扛单粒子烧毁能力,改善产品性能。

- 还没有人留言评论。精彩留言会获得点赞!