半导体器件及其制备方法与流程

本技术涉及半导体器件,尤其涉及一种半导体器件及其制备方法。

背景技术:

1、电容是目前集成电路领域必不可少的器件之一,芯片内集成电容需要额外的设计。三维封装中经常通过混合键合的方法集成电容,也即键合金属同时用作电容极板。但电容极板不能完全相互平行,电容值很小,且电极板之间间距不能太小,金属扩散容易产生可靠性问题,导致电容失效。混合键合对于键合金属层的图形均匀性非常敏感,电容极板的形状会影响键合界面金属图形的均匀性变差,有可能导致键合失效以及混合键合工艺与电容极板制作工艺兼容性差的技术问题。

技术实现思路

1、有鉴于此,本技术提供一种能够提高键合结构和电容的兼容性以及混合键合的良率的半导体器件及其制备方法。

2、为解决上述问题,本技术提供的技术方案如下:

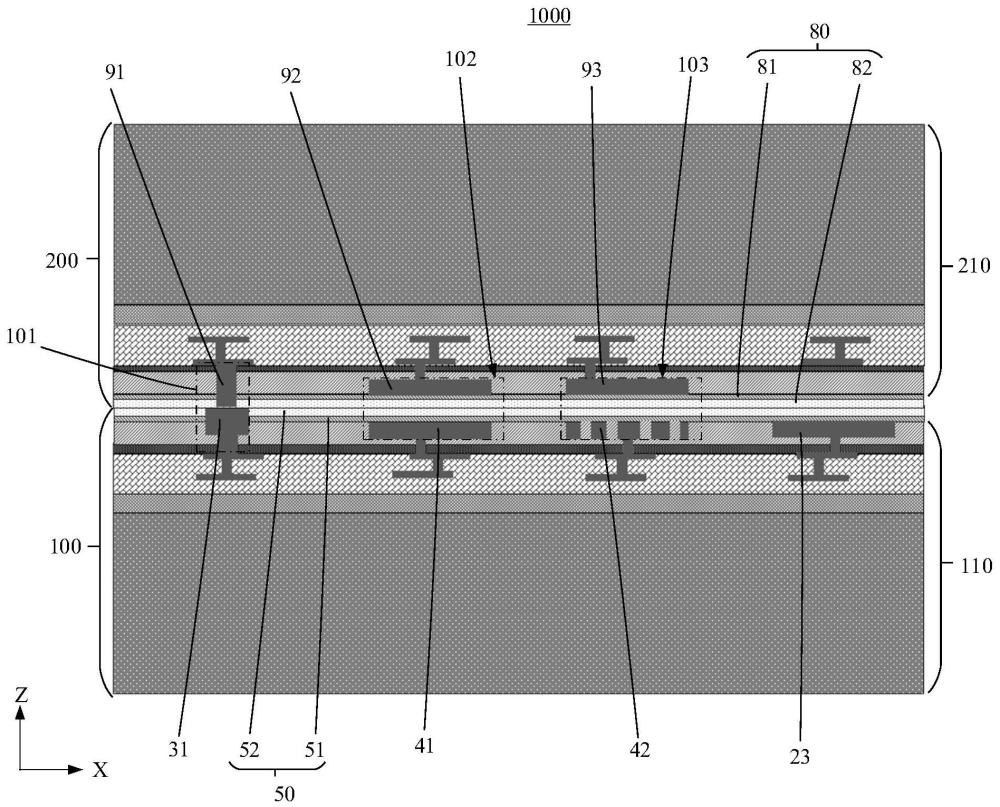

3、第一方面,本技术提供一种半导体器件,包括第一半导体结构及第二半导体结构,第一半导体结构包括第一电容极板、第一电容介质层及第一键合结构,第二半导体结构包括第二电容极板、第二电容介质层及第二键合结构,第一键合结构位于第一电容介质层内,第二键合结构位于第二电容介质层内,第一半导体结构及第二半导体结构通过第一键合结构和第二键合结构键合;

4、其中,第一电容极板与第一键合结构位于不同层且第二电容极板与第二键合结构位于不同层,第一电容极板在第二半导体结构上的正投影与第二电容极板至少部分重叠,第一电容极板及第二电容极板之间具有第一电容介质层和第二电容介质层中的至少一个,第一电容极板、第二电容极板及位于二者之间的第一电容介质层和第二电容介质层至少一个构成电容结构。

5、在本技术一些实施例中,所述第一键合结构在所述第一半导体结构上的正投影与所述第一电容极板相邻设置,所述第二键合结构在所述第二半导体结构上的正投影与所述第二电容极板相邻设置。

6、在本技术一些实施例中,第一半导体结构还包括第一互连结构,第二半导体结构还包括第二互连结构;第一互连结构包括连接的第一互连导电层和第三互连导电层,第二互连结构包括连接的第二互连导电层及第四互连导电层;

7、第一电容极板与第一互连结构连接,第二电容极板与第二互连结构连接。

8、在本技术一些实施例中,第一互连结构还包括第一互连导电线路,第一互连导电线路与第一互连导电层连接;及/或

9、第二互连结构还包括第二互连导电线路,第二互连导电线路与第二互连导电层连接;

10、其中,第一键合结构与第一互连导电层或第一互连导电线路连接,第二键合结构与第二互连导电层或第二互连导电线路连接。

11、在本技术一些实施例中,第一键合结构在第一互连结构上的正投影落在第一互连导电线路外;第二键合结构在第一互连结构上的正投影落在第一互连导电线路外。

12、在本技术一些实施例中,第一键合结构位于第一互连导电线路上且与第一互连导电线路连接;及

13、第二键合结构在第一互连结构上的正投影落在第一互连导电线路上且与位于第一互连导电线路上的第一键合结构键合。

14、在本技术一些实施例中,第一键合结构位于第一互连导电线路上且与第一互连导电线路连接;及

15、第二键合结构位于第二互连导电线路上且与第二互连导电线路连接;

16、第二键合结构与第一键合结构键合。

17、在本技术一些实施例中,第一键合结构和第二键合结构中的至少一个的截面呈i字型或t字型。

18、在本技术一些实施例中,第一电容极板为第一互连结构的顶层金属的至少一部分;及/或

19、第二电容极板为第二互连结构的顶层金属的至少一部分。

20、在本技术一些实施例中,第一互连导电线路与第一电容极板同层设置且材料相同;及/或

21、第二互连导电线路与第二电容极板同层设置且材料相同。

22、在本技术一些实施例中,第一互连导电线路与第一电容极板不同层;及/或

23、第二互连导电线路与第二电容极板不同层。

24、在本技术一些实施例中,第一半导体结构还包括第一介质层,第二半导体结构还包括第二介质层,第一互连导电线路位于第一介质层内,第二互连导电线路位于第二介质层内;

25、第一半导体结构还包括位于第一介质层上的第三介质层,第一电容极板位于第三介质层内。

26、在本技术一些实施例中,第一电容极板或第二电容极板的形状为实心片状或具有镂空的片状。

27、在本技术一些实施例中,所述第一电容极板或所述第二电容极板包括至少一镂空部,部分所述第一介质层或所述第二介质层位于所述镂空部内。

28、在本技术一些实施例中,第一电容极板和第二电容极板中的至少一个为键合结构阵列,键合结构阵列贯穿第一电容介质层或第二电容介质层并与第一互连结构或第二互连结构连接;

29、第一电容极板或第二电容极板的形状为实心片状或具有镂空的片状。

30、在本技术一些实施例中,第一键合结构和第二键合结构之间通过金属键键合,第一电容介质层与第二电容介质层之间通过共价键键合。

31、在本技术一些实施例中,第一电容介质层与第二电容介质层之间二氧化硅层,且所述二氧化硅层的厚度在1nm-20nm之间。

32、在本技术一些实施例中,第一电容介质层包括第一电容介质材料层或第二电容介质材料层;

33、第二电容介质层包括第三电容介质材料层或第四电容介质材料层;

34、其中,第一电容介质材料层的介电常数高于第二电容介质材料层的介电常数,第三电容介质材料层的介电常数高于第四电容介质材料层的介电常数。

35、在本技术一些实施例中,第一电容介质层包括层叠设置的第一电容介质材料层和第二电容介质材料层;第二电容介质层包括层叠设置的第三电容介质材料层和第四电容介质材料层;

36、第一电容介质材料层的介电常数高于第二电容介质材料层的介电常数,第三电容介质材料层的介电常数高于第四电容介质材料层的介电常数,第二电容介质材料层与第四电容介质材料层键合。

37、在本技术一些实施例中,第一键合结构和第二键合结构的数量相等且均大于或等于1;

38、当第一键合结构和第二键合结构的数量均大于1时,多个第一键合结构的结构相同或不相同,多个第二键合结构的结构相同或不相同。

39、在本技术一些实施例中,第一电容极板和第二电容极板的数量相等且均大于或等于1;

40、当第一电容极板和第二电容极板的数量且均大于1时,多个第一电容极板的结构相同或不相同,多个第二电容极板的结构相同或不相同。

41、本技术还提供一种半导体器件的制备方法,包括:

42、提供第一电路基板和第二电路基板,在第一电路基板上形成第一电容极板并在第二电路基板上形成第二电容极板;

43、形成覆盖第一电容极板的第一电容介质层并形成覆盖第二电容极板的第二电容介质层;

44、在第一电路基板上形成至少部分位于第一电容介质层内的第一键合结构,得到第一半导体结构;并在第二电路基板上形成至少部分位于第二电容介质层内的第二键合结构,得到第二半导体结构;及

45、将第一半导体结构和第二半导体结构通过第一键合结构和第二键合结构键合在一起;

46、其中,第一电容极板、第二电容极板及位于二者之间的第一电容介质层和第二电容介质层构成电容结构。

47、在本技术一些实施例中,在第一电路基板上形成第一电容极板并在第二电路基板上形成第二电容极板的步骤之前,还包括:

48、在第一初始电路基板上依次形成第一互连介质层和第一介质层,在第二初始电路基板上依次形成第二互连介质层和第二介质层;

49、在第一互连介质层和第一介质层内形成包括第一互连导电层的第一互连结构,得到第一电路基板;在第二互连介质层和第二介质层内形成包括第二互连导电层的第二互连结构,得到第二电路基板;及

50、连接第一互连导电层和第一电容极板,连接第二互连导电层与第二电容极板。

51、在本技术一些实施例中,在第一电路基板上形成第一电容极板并在第二电路基板上形成第二电容极板的步骤包括:

52、图案化第一介质层,并在图案化后的第一介质层的镂空内填充导电材料,以在第一电路基板上形成第一电容极板;及

53、图案化第二介质层,并在图案化后的第二介质层的镂空内填充导电材料,以在第二电路基板上形成第二电容极板;

54、其中,第一电容极板或第二电容极板呈实心片状或具有镂空的片状。

55、在本技术一些实施例中,在第一初始电路基板上依次形成第一互连介质层和第一介质层,在第二初始电路基板上依次形成第二互连介质层和第二介质层的步骤之后,还包括步骤:

56、在第一介质层内形成第一互连导电线路并使得第一互连导电线路与第一互连导电层连接;及/或

57、在第二介质层内形成第二互连导电线路并使得第二互连导电线路与第二互连导电层连接;

58、第一电容极板与第一互连导电线路同层且通过同一个工艺制作而成;第二电容极板与第二互连导电线路同层且通过同一个工艺制作而成。

59、在本技术一些实施例中,在第一初始电路基板上依次形成第一互连介质层和第一介质层,在第二初始电路基板上依次形成第二互连介质层和第二介质层的步骤之后,还包括步骤:

60、在第一介质层内形成第一互连导电线路并使得第一互连导电线路与第一互连导电层连接;及/或

61、在第二介质层内形成第二互连导电线路并使得第二互连导电线路与第二互连导电层连接;

62、在第一介质层上形成第三介质层;及

63、在第三介质层内形成第一电容极板。

64、在本技术一些实施例中,在第一电路基板上形成位于第一电容介质层内的第一键合结构,得到第一半导体结构;并在第二电路基板上形成位于第二电容介质层内的第二键合结构,得到第二半导体结构的步骤包括:

65、图案化第一电容介质层/第二电容介质层,得到自第一电容介质层/第二电容介质层的表面贯穿至第一互连导电层/第二互连导电层的第一连接孔,及/或贯穿至第一互连导电线路/第二互连导电线路的第二连接孔;

66、在第一连接孔/第二连接孔内填充导电材料,得到第一键合结构/第二键合结构并使得第一键合结构/第二键合结构与第一互连导电层/第三互连导电层连接。

67、在本技术一些实施例中,图案化第一电容介质层/第二电容介质层,得到自第一电容介质层/第二电容介质层的表面贯穿至第一互连导电层/第二互连导电层的第一连接孔包括:

68、在第一电容介质层远离第一电容极板的表面形成第一掩模层;图案化第一掩模层,以在第一掩模层上形成多个贯穿第一掩模层的第一开孔,并使得第一开孔在第一电路基板上的正投影落在第一互连导电层上;

69、以图案化后的第一掩模层为掩模,在第一电容介质层及部分第一电路基板上形成第二开孔,并在第一开孔及第二开孔内填充抗反射涂层,其中抗反射涂层与第一互连导电层连接;

70、去除第一掩模层,并在第一电容介质层远离第一电容极板的表面形成第二掩模层;图案化第二掩模层,以在第二掩模层上形成多个贯穿第二掩模层的第三开孔,并使得第三开孔与第一开孔连通;

71、以图案化后的第二掩模层为掩模,在第一电容介质层上形成与第三开孔及第二开孔连通且环绕抗反射涂层的第四开孔;

72、去除抗反射涂层,得到第一连接孔,第一连接孔包括第二开孔及第四开孔。

73、在本技术一些实施例中,在形成第三开孔的同时,还形成多个贯穿第二掩模层的第五开孔,第五开孔在第一电路基板上的正投影落在第一互连导电线路上;

74、在形成第四开孔的同时,还形成第六开孔,得到第二连接孔。

75、在本技术一些实施例中,形成覆盖第一电容极板的第一电容介质层并形成覆盖第二电容极板的第二电容介质层的步骤包括:

76、在第一电容极板上形成第一电容介质材料层或第二电容介质材料层,在第二电容极板上形成第三电容介质材料层或第四电容介质材料层;第一电容介质材料层的介电常数高于第二电容介质材料层的介电常数,第三电容介质材料层的介电常数高于第四电容介质材料层的介电常数。

77、在本技术一些实施例中,在第一电容极板上依次形成第一电容介质材料层及第二电容介质材料层,在第二电容极板上依次形成第三电容介质材料层或第四电容介质材料层,第一电容介质材料层的介电常数高于第二电容介质材料层的介电常数,第三电容介质材料层的介电常数高于第四电容介质材料层的介电常数;

78、在将第一半导体结构和第二半导体结构通过第一键合结构和第二键合结构键合在一起的步骤中,第二电容介质材料层与第四电容介质材料层键合。

79、在本技术一些实施例中,在将第一半导体结构和第二半导体结构通过第一键合结构和第二键合结构键合在一起的步骤之后,还包括步骤:

80、对键合后的第一半导体结构和第二半导体结构进行退火处理。

81、其中,该退火处理的条件设置为:使得相互键合的所述第一电容介质层50和所述第二电容介质层80之间形成二氧化硅层(图未示),且使得所述二氧化硅层的厚度在1nm-20nm之间。

82、在本技术一些实施例中,在第一电路基板上形成位于在第一电容介质层内的第一键合结构并在第二电路基板上形成位于第二电容介质层内的第二键合结构的步骤的同时,还包括:

83、以第一键合结构或第二键合结构形成键合结构阵列;

84、键合结构阵列作为其中一个电容极板,键合结构阵列在另一个半导体结构中的第一电容极板或第二电容极板上的正投影与另一个半导体结构中的第一电容极板或第二电容极板至少部分重叠。

85、本技术提供的半导体器件及其制备方法,本技术针对键合金属同时用作电容极板导致的键合失效以及混合键合工艺兼容性差的技术问题,并通过提供一种半导体器件,并将第一半导体结构中的第一电容极板与第一键合结构位于不同层,并将第二半导体结构中的第二电容极板与第二键合结构位于不同层,避免了因为电容的集成对键合层产生的影响,混合键合的良率对于图形均匀性非常敏感,电容极板的形成过程与键合工艺单独区分,可以使得电极集成方法与键合工艺完全兼容,不会影响混合键合的良率。

- 还没有人留言评论。精彩留言会获得点赞!