一种半导体结构及其制备方法与流程

本公开涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、在3ds及hbm产品中,模塑底部填充(molded underfill)技术是一种集成了底部填充和注塑工艺的技术,具有高产出、低成本的优势,然而随着集成度和i/o密度逐步提高,相邻凸块(bump)之间间隙越来越小,特别对于hbm产品,凸块间距(bump space)已经小于20μm,且bump数量很多,一般达到数万颗,紧密排布的bump增加了模塑料(molding compound)材料的流动阻力,给molded underfill技术的底部填充效果带来了巨大挑战,可能会出现填充空隙(void)或流痕(flow mark)等现象,严重时会影响封装可靠性。现有的解决方法有通过增大压缩成型工艺(compression mold process)中合模压力来平衡bump密排造成的流阻的增加,但是合模压力的增加同时也会增加晶圆裂片风险的增加,不是一个安全有效的解决方案。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其制备方法。

2、根据本公开实施例的第一方面,提供了一种半导体结构,包括:

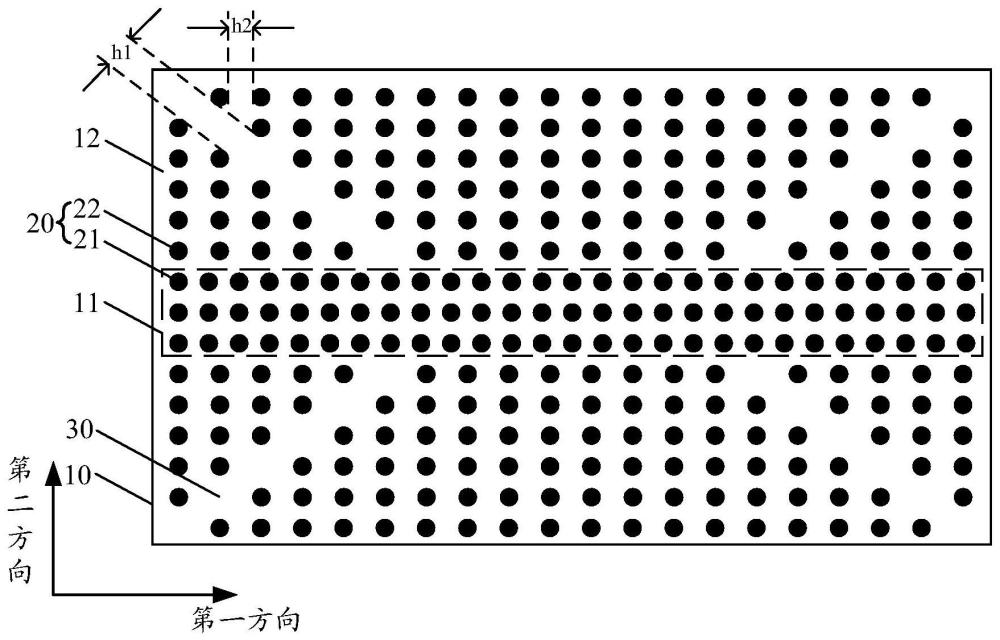

3、芯片单元,所述芯片单元包括第一区域和位于所述第一区域外围的第二区域;

4、多个连接结构,所述连接结构包括位于所述第一区域上的多个第一连接结构和位于所述第二区域上的多个第二连接结构,其中,在第一方向上,相邻的所述第一连接结构之间的间距小于相邻的所述第二连接结构之间的间距,所述第一方向平行于所述芯片单元的平面;

5、主路径,位于所述第二区域上,所述主路径两侧相对设置的两个所述第二连接结构之间的间距大于其他位置处相邻两个所述第二连接结构之间的间距。

6、在一些实施例中,所述第一区域沿所述第一方向延伸,所述第二区域沿第二方向分布在所述第一区域的两侧,其中,所述第二方向平行于所述芯片单元的平面,且所述第一方向和所述第二方向相交。

7、在一些实施例中,所述芯片单元包括多个间隔设置的所述第一区域,每个所述第一区域均有至少一条所述主路径与其连接,

8、相邻两个所述第一区域之间的所述第二区域上形成有多条所述主路径,其中,每个所述第一区域均有至少一条位于相邻两个所述第一区域之间的所述第二区域上的所述主路径与其连接。

9、在一些实施例中,所述主路径包括第一子路径,所述第一子路径从所述芯片单元的边缘向所述第一区域的方向延伸,所述第一子路径和与其接触的所述芯片单元的边的夹角范围为30°~60°。

10、在一些实施例中,所述主路径还包括第二子路径,所述第二子路径与至少一条所述第一子路径连通。

11、在一些实施例中,所述连接结构还包括位于所述第二区域上的多个第三连接结构,所述第三连接结构设置在所述主路径上,所述第三连接结构的顶表面低于所述第二连接结构的顶表面。

12、在一些实施例中,所述第一连接结构和所述第二连接结构同时具有第一连接层、第二连接层和第三连接层,所述第三连接结构具有第一连接层或第一连接层和第二连接层。

13、在一些实施例中,所述第一连接结构为导电接点凸块,所述第二连接结构为虚拟凸块。

14、根据本公开实施例的第二方面,提供了一种半导体封装结构,包括:

15、基板;

16、芯片单元,所述芯片单元通过连接结构安装于所述基板上;所述芯片单元具有第一区域和位于所述第一区域外围的第二区域,所述连接结构包括多个第一连接结构和多个第二连接结构,在第一方向上,相邻的所述第一连接结构之间的间距小于相邻的所述第二连接结构之间的间距,所述第一方向平行于所述芯片单元的平面;

17、主路径,位于所述第二区域上,所述主路径两侧相对设置的两个所述第二连接结构之间的间距大于其他位置处相邻两个所述第二连接结构之间的间距;

18、底部填充材料,所述底部填充材料沿所述主路径填入所述第一连接结构和所述第二连接结构之间,塑封所述芯片单元和所述基板。

19、在一些实施例中,所述连接结构还包括位于所述第二区域上的多个第三连接结构,所述第三连接结构设置在所述主路径上,所述第三连接结构不与所述基板接触连接。

20、在一些实施例中,所述第一连接结构和所述第二连接结构同时具有第一连接层、第二连接层和第三连接层,所述第三连接结构具有第一连接层或第一连接层和第二连接层。

21、根据本公开实施例的第三方面,提供了一种半导体结构的制备方法,包括:

22、提供芯片单元,所述芯片单元包括第一区域和位于所述第一区域外围的第二区域;

23、在所述芯片单元上形成多个连接结构,所述连接结构包括位于所述第一区域上的多个第一连接结构和位于所述第二区域上的多个第二连接结构,其中,在第一方向上,控制相邻的所述第一连接结构之间的间距小于相邻的所述第二连接结构之间的间距,所述第一方向平行于所述芯片单元的平面;

24、在所述第二区域上形成主路径,控制所述主路径两侧相对设置的两个所述第二连接结构之间的间距大于其他位置处相邻两个所述第二连接结构之间的间距。

25、在一些实施例中,还包括:

26、在所述第二区域的所述主路径上形成第三连接结构,所述第三连接结构的顶表面低于所述第二连接结构的顶表面。

27、在一些实施例中,形成所述第一连接结构、所述第二连接结构以及所述第三连接结构的步骤包括:

28、在所述芯片单元上形成第一连接层,所述第一连接层同时形成在所述第一区域和所述第二区域;

29、在所述芯片单元上形成掩膜层,所述掩膜层覆盖所述主路径,暴露出所述第一区域的所述第一连接层和所述主路径之外的其他所述第二区域的所述第一连接层;

30、在暴露的所述第一连接层上形成第二连接层和第三连接层,分别形成所述第一连接结构和所述第二连接结构;

31、去除所述掩膜层,暴露出被所述掩膜层覆盖的所述第一连接层,形成所述第三连接结构。

32、在一些实施例中,形成所述第一连接结构、所述第二连接结构以及所述第三连接结构的步骤包括:

33、在所述芯片单元上形成第一连接层,所述第一连接层同时形成在所述第一区域和所述第二区域;

34、在所述芯片单元上形成掩膜层,所述掩膜层暴露出所述第一连接层;

35、在所述第一连接层上形成第二连接层;

36、在所述第二连接层上形成第三连接层,所述第三连接层不形成在所述主路径上的所述第二连接层上,以同时形成所述第一连接结构、所述第二连接结构以及所述第三连接结构。

37、本公开实施例中,通过在第二区域上形成主路径,且主路径两侧相对设置的两个第二连接结构之间的间距大于其他位置处相邻两个第二连接结构之间的间距,如此,使得底部填充材料流动填充时可以通过主路径流进连接结构之间,因为主路径的宽度较大,没有第二连接结构进行阻碍,因此降低了主路径上的流阻,进而降低了总流阻,提高了填充效果。

- 还没有人留言评论。精彩留言会获得点赞!