一种横向高压功率半导体器件及生产工艺

本发明涉及半导体,具体涉及一种横向高压功率半导体器件及生产工艺。

背景技术:

1、电力电子系统最为关键的元器件就是功率半导体器件。随着电力电子技术的不断发展,集成化、智能化、小型化成为了主要的发展方向。智能功率集成电路应运而生,它将控制电路,驱动电路,保护电路以及功率半导体器件等集成到一个芯片里面,从而增加了系统的智能度和集成度。为了将功率器件集成到同一个芯片里,横向功率器件是最常见和最可行的选择。

2、击穿电压和比导通电阻是半导体功率器件的重要性能指标。随着器件技术的进步,功率器件逐渐接近了其性能极限。为了进一步提升器件性能,提升击穿电压,降低比导通电阻,resurf技术被广泛应用于功率器件之中。典型的resurf技术包括single-resurf,double-resurf和triple-resurf三类,在此基础上还提出了变掺杂resurf技术以及变深度resurf技术,其作用使顶层材料靠近介质层的一面会由于受到纵向电场的作用而耗尽(纵向结构可以看成是一个平板电容器),纵向耗尽区与横向耗尽区相互交叠,使横向耗尽区延长,提高了器件击穿电压并且保证了较低的比导通电阻。

3、然而,多层resurf技术涉及到复杂且昂贵的外延再生长技术,变掺杂、变深度resurf技术涉及到多次的离子注入。而且这些工艺在下一代宽禁带半导体(如碳化硅和氮化镓)中,难度和成本更是被抬升到了新的高度。

4、如附图1所示,为传统横向jbs二极管器件。虽然resurf技术使器件表面电场在横向上的分布距离变长,整体降低了表面电场,但在阳极p+/漂移区和阴极n+/漂移区这两处仍然有两个电场尖峰存在。因为这两处的掺杂浓度比漂移区内高得多,所以电力线在此大量集中,是表面电场最高的地方。器件在反向耐压时,resurf横向jbs器件结构的表面电场分布不够均匀,中间电场低而两边出现电场峰值,器件容易在两端发生击穿影响器件整体击穿电压。在表面电场分布中直接引入新电场峰的方法会使器件的可靠性受到影响,因为横向器件的电流流经表面,载流子碰撞电离产生的大量电子-空穴对会在表面强电场的作用下进入器件的场氧化层,进入场氧化层的电子-空穴对会改变表面电场的分布。由此可见,现有的传统resurf技术无法为提高横向器件的耐压和可靠性提供有力保障。因此,一种适用于横向功率器件的增强型resurf结构是迫切需要的。

技术实现思路

1、为解决上述问题,本发明提供的技术方案为:

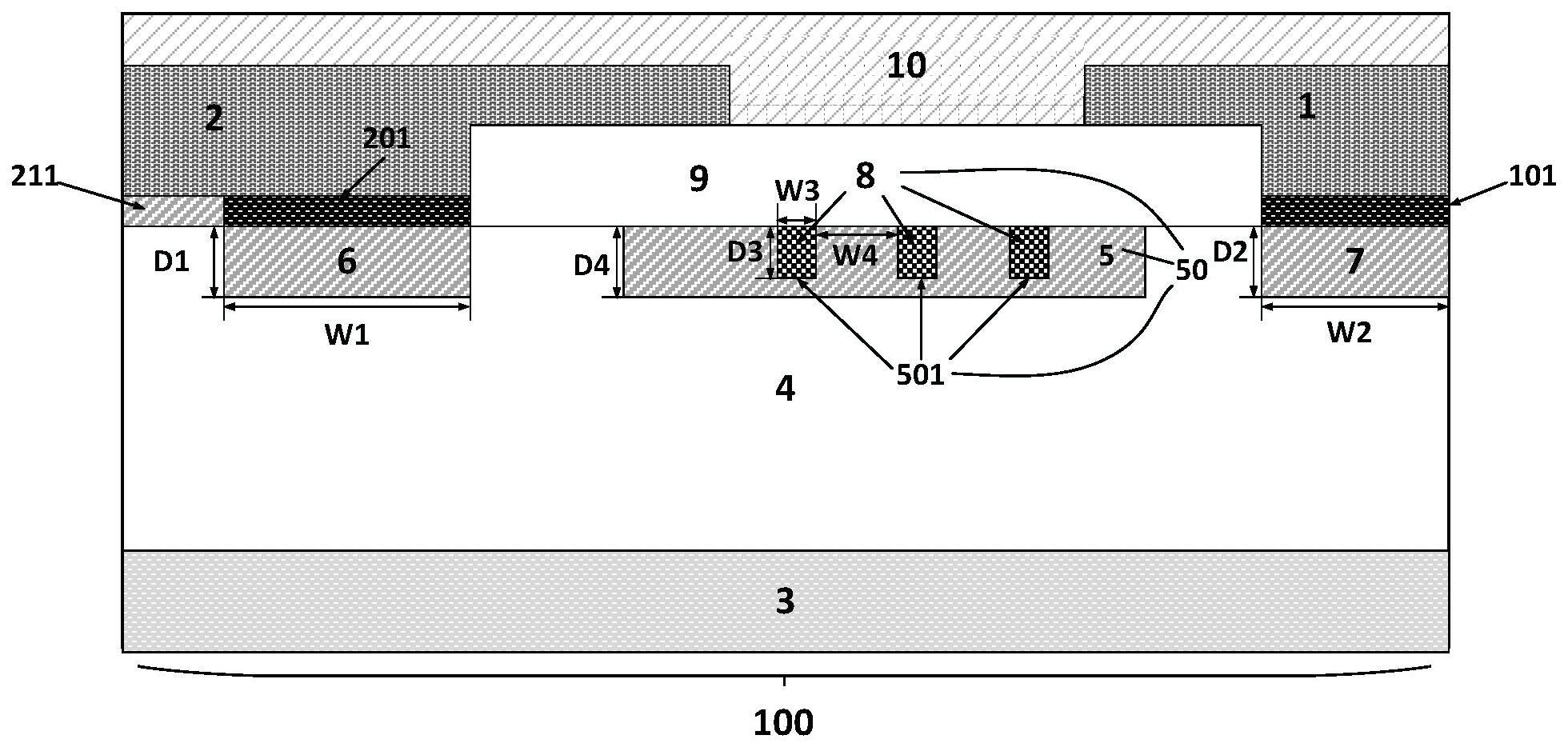

2、一种横向高压功率半导体器件,包括衬底、位于所述衬底上且具有第一导电类型的漂移区、位于所述漂移区顶部的第二导电类型高掺杂阱区、位于所述漂移区顶部的第二导电类型横向掺杂顶层区、位于所述漂移区顶部的第一导电类型高掺杂阱区、位于所述漂移区上的场氧化层、位于所述漂移区上的阴极金属层、位于所述漂移区上的阳极金属层以及器件顶部的钝化层,所述阳极金属层与所述第二导电类型高掺杂阱区之间形成阳极欧姆接触层,所述阳极金属层与所述漂移区之间形成阳极肖特基接触层,所述阴极金属层与所述第一导电类型高掺杂阱区之间形成阴极欧姆接触层,所述场氧化层与所述第二导电类型横向掺杂顶层区相接触,所述第二导电类型横向掺杂顶层区内形成窄槽,所述窄槽内填充有电介质。

3、本发明进一步设置为所述第二导电类型横向掺杂顶层区内的所述窄槽的数量不唯一,当所述窄槽的宽度和深度固定且所述窄槽之间的间距固定时,随着所述第二导电类型横向掺杂顶层区掺杂浓度的增大或者随着所述第二导电类型横向掺杂顶层区横向长度/纵向深度的增大,所述窄槽的数量增加。

4、本发明进一步设置为所述第二导电类型横向掺杂顶层区内的所述窄槽的深度不唯一,当所述窄槽的宽度和数量固定且所述窄槽之间的间距固定时,随着所述第二导电类型横向掺杂顶层区掺杂浓度的增大或者随着所述第二导电类型横向掺杂顶层区横向长度/纵向深度的增大,所述窄槽的深度增加。

5、本发明进一步设置为所述第二导电类型横向掺杂顶层区内的所述窄槽的宽度不唯一,当所述窄槽的数量和深度固定且所述窄槽之间的间距固定时,随着所述第二导电类型横向掺杂顶层区掺杂浓度的增大或者随着所述第二导电类型横向掺杂顶层区横向长度/纵向深度的增大,所述窄槽的宽度增加。

6、本发明进一步设置为当所述第二导电类型横向掺杂顶层区内的窄槽存在多个,且所述第二导电类型横向掺杂顶层的掺杂浓度、横向长度及纵向深度确定时,若所述窄槽的宽度和深度保持一致时,所述窄槽之间的间距从所述第二导电类型高掺杂阱区到所述第一导电类型高掺杂阱区由宽变窄。

7、本发明进一步设置为当所述第二导电类型横向掺杂顶层区内的窄槽存在多个,且所述第二导电类型横向掺杂顶层的掺杂浓度、横向长度及纵向深度确定时,若所述窄槽的宽度和间距保持一致时,所述窄槽的深度从所述第二导电类型高掺杂阱区到所述第一导电类型高掺杂阱区由浅变深。

8、本发明进一步设置为当所述第二导电类型横向掺杂顶层区内的窄槽存在多个,且所述第二导电类型横向掺杂顶层的掺杂浓度、横向长度及纵向深度确定时,若所述窄槽的深度和间距保持一致时,所述窄槽的宽度从所述第二导电类型高掺杂阱区到所述第一导电类型高掺杂阱区由窄变宽。

9、本发明进一步设置为当所述第二导电类型横向掺杂顶层区内的窄槽存在多个且所述窄槽内填充的电介质不一致时,所述窄槽内电介质的常数从所述第二导电类型高掺杂阱区到所述第一导电类型高掺杂阱区由大变小。

10、本发明进一步设置为当所述第二导电类型横向掺杂顶层区内的窄槽的三维布局为离散或点阵分布时,若所述窄槽的宽度和深度一致,则所述第二导电类型横向掺杂顶层区内的窄槽的分布从所述第二导电类型高掺杂阱区到所述第一导电类型高掺杂阱区由疏变密。

11、本发明进一步设置为所述第一导电类型高掺杂阱区远离所述第二导电类型横向掺杂顶层区的一侧形成有终端宽槽,所述终端宽槽内填充有电介质,所述终端宽槽的宽度至少大于四倍的所述第一导电类型高掺杂阱区的宽度,所述终端宽槽的深度至少大于四倍的所述第一导电类型高掺杂阱区的深度。

12、本发明进一步设置为所述第二导电类型横向掺杂顶层区和所述第一导电类型高掺杂阱区之间形成有隔离槽,所述隔离槽内填充有电介质,所述隔离槽的宽度小于或等于所述第二导电类型横向掺杂顶层区和所述第一导电类型高掺杂阱区之间的距离,所述隔离槽的深度大于所述窄槽的深度,所述隔离槽的深度小于所述终端宽槽的深度。

13、本发明进一步设置为所述窄槽、所述终端宽槽和所述隔离槽内填充的电介质为二氧化硅、聚酰亚胺或苯并环丁烯。

14、本发明进一步设置为所述窄槽的截面形状为矩形、倒梯形或圆形中的至少一种。

15、本发明进一步设置为所述第二导电类型横向掺杂顶层区内的窄槽的三维布局为连续的条形、离散的条形、点阵分布的圆形、点阵分布的三角形、点阵分布的六边形中的至少一种。

16、一种横向高压功率半导体器件的生产工艺,用于制备上述的横向高压功率半导体器件,包括:

17、于碳化硅晶圆中注入离子,高温退火进行离子激活后得到衬底;

18、衬底通过外延生长得到第一导电类型漂移区;

19、通过在漂移区的源端注入离子,高温退火进行离子激活后形成源极第二导电类型阱区;

20、通过在漂移区的漏端注入离子,高温退火进行离子激活后形成源极第一导电类型阱区;

21、通过在漂移区的横向掺杂端注入离子,高温退火进行离子激活后形成第二导电类型横向掺杂顶层区;

22、利用氧化硅掩膜并采用刻蚀工艺,于第二导电类型横向掺杂顶层区刻蚀出窄槽、于第一导电类型漂移区刻蚀出隔离槽和终端宽槽;

23、通过溅射、低压化学气相沉积或者等离子增强化学气相沉积于窄槽、隔离槽和终端宽槽回填电介质;

24、通过光刻以及刻蚀除去窄槽、隔离槽和终端宽槽外多余的电介质;

25、于器件表面生长一层氧化层,形成场氧化层;

26、通过光刻以及刻蚀,在源极区域与漏极区域进行开孔并溅射金属,在金属剥离后进行退火,形成良好的欧姆接触,完成阳极金属和阴极金属的淀积;

27、对源极区域肖特基部分进行开孔并溅射金属,形成肖特基接触,并通过剥离完成阳极金属和阴极金属的图形化;

28、于器件表面进行钝化,形成钝化层。

29、采用本发明提供的技术方案,与现有技术相比,具有如下有益效果:

30、本技术方案横向高压功率半导体器件是基于超级结原理,通过引入沟槽,在尽可能小的面积上形成耐压尽可能高的增强型resurf结构,优化了横向器件的表面电场分布,通过沟槽结构以及内部填充的高电介质常数的介质,引入了多个电场峰值,有效抑制了表面电场的掉落,在保证较低比导通电阻的同时提高了器件的耐压。

31、本技术方案横向高压功率半导体器件的生产工艺采用离子注入+沟槽刻蚀的技术路线,技术省去了多层resurf结构的外延再生长工艺,让resurf技术在功率器件,特别是宽禁带半导体功率器件中的应用前景更加广阔。

- 还没有人留言评论。精彩留言会获得点赞!