一种降低碳化硅外延薄膜表面缺陷的方法与流程

本发明涉及磁性材料,具体涉及碳化硅外延生长技术,尤其是一种降低碳化硅外延薄膜表面缺陷的方法。

背景技术:

1、碳化硅是一种特殊的半导体材料,以碳化硅(sic)材料为代表的第三代宽带隙半导体材料具有宽带隙、高临界击穿电场、高热导率、高载流子饱和漂移速度等特点,特别适合制作高温、高压、大功率、耐辐照等半导体器件。其优越的性能可以满足现代电子技术对高温抗辐射和高频大功率的要求。

2、sic晶体结构具有同质多型的特点,即在化学计量成分相同情况下具有不同的晶体结构,最常见的sic多型有立方结构的3c-sic、六方结构的4h-sic和6h-sic。4h-sic作为一种具有极高应用价值和广阔市场前景的半导体材料,已受到国内外半导体行业的极大关注。

3、目前大部分的sic器件并不是制备在晶体上面是制备在外延层上,因为外延层缺陷少,晶格排列整齐,比直接的晶体衬底性能好,在外延层上制造半导体器件性能更加优异。因此sic晶体材料的外延生长成为了发展sic半导体技术的关键因素之一。

4、尽管sic材料有许多优越的特性,但是由于sic材料中存在大量的缺陷,使得其在耐压、迁移率等方面的半导体性能大大受到影响,存在很多因素影响缺陷从衬底到外延层的扩展,这些因素包括衬底的晶向,表面极性,倾斜角度,偏离原晶向的结晶方向等,还包括缺陷繁衍机制和外延之前的化学处理,在衬底上的预生长和生长条件(如碳硅比,生长速度和边界生长工序等)。

5、为了能够降低外延层中的缺陷密度同时又得到确定的掺杂浓度和厚度,必须在实际生产中对以上提到的因素进行不断优化。

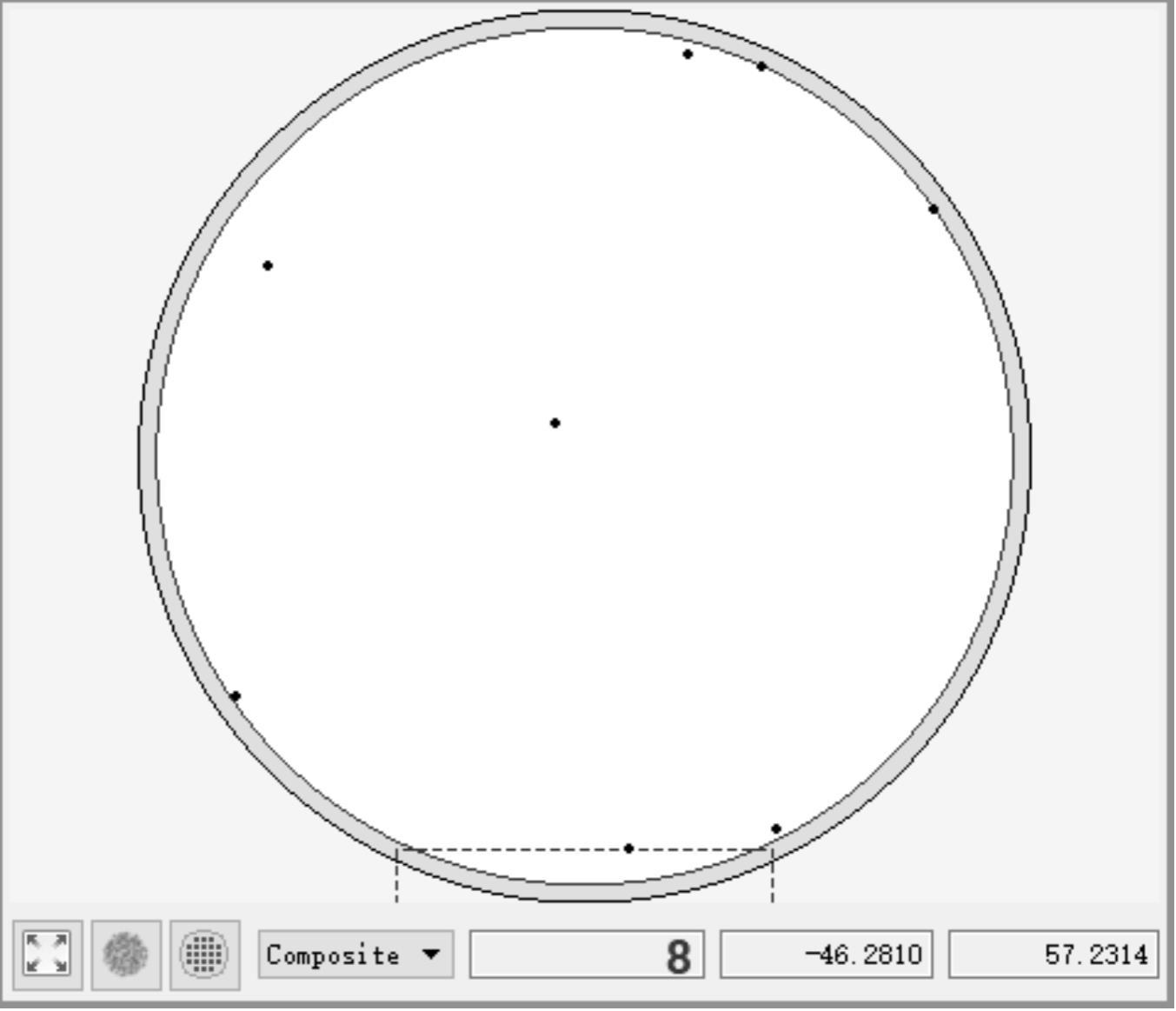

6、专利申请cn 112490117a公开了一种提高碳化硅外延薄膜生长质量的方法,包括清洗衬底置于反应室内的小盘上;将反应室抽至真空,随后通入氢气,进行恒温刻蚀;采用线性缓变的方式在20~100s内改变反应室压力、温度,同时通入碳源、硅源、掺杂源,其中c/si摩尔比由0渐变至0.80~1.10;采用线性缓变的方式在20~100s内改变碳源、掺杂源流量和硅源流量,保持c/si摩尔比不变;采用线性缓变的方式20~100s内改变温度、压力、碳源、掺杂源流量以及硅源流量至目标条件进行外延薄膜生长直至目标厚度等。采用该方法,可以显著降低外延薄膜的外延薄膜的晶体缺陷,主要是三角形缺陷,但是仍然存在一定量的三角形缺陷,数量大概在10-50,如图1所示,同时还存在一定量的颗粒缺陷,数量大概在100-500个,如图2所示。

7、其中三角形缺陷是在外延生长过程中,由外来颗粒物,表面划痕或诸如tsd等晶体结晶缺陷影响原子台阶流动,而在4h-sic外延层表面上所形成的具有三角形形状或图案的外延形貌缺陷,借助强光束或光学显微镜可以用肉眼直接观察。

8、而颗粒缺陷是在外延生长结束后降温阶段,反应室内结晶松动掉落到外延片上形成的外延形貌缺陷。该缺陷可以在整个工艺结束后通过额外的清洗工艺去除,但若测每件产品都需增加一道清洗工艺,则会增加时间成本,打断生长连续性,影响整体的产能。

9、实际上,在sic的整个外延层生长过程都有可能引入颗粒掉落,造成颗粒缺陷,若在升温、刻蚀或生长阶段引入,则会形成掉落物、三角形缺陷,影响外延良率。若在降温阶段引入,则会形成微粒,该缺陷会在后续的mcv测量中,导致汞探针漏汞,更甚者会导致汞探针损坏。

10、因此,寻找如何进一步降低三角形缺陷和颗粒缺陷的外延工艺具有积极的现实意义。

技术实现思路

1、本发明的目的是为了克服现有的碳化硅外延薄膜生产过程中存在颗粒缺陷的问题,提供一种降低碳化硅外延薄膜表面缺陷的方法,通过在外延结束后的降温阶段,降温前即升高氢气流至300~500slm,增大气流以减少颗粒掉落在外延片上,减少对外延片的污染,并且可以提高降温效率,优化工艺时长。

2、在此基础上,在升温及刻蚀阶段,在衬底放入反应室后,升温的同时提高氢气流至300~500slm,可以减少颗粒掉落在衬底上面,并可提高刻蚀效率,抑制三角形缺陷的产生,从而显著地减少碳化硅外延薄膜表面的颗粒缺陷和三角形缺陷。

3、具体方案如下:

4、一种降低碳化硅外延薄膜表面缺陷的方法,包括以下步骤:

5、第一步:对碳化硅衬底进行清洗,然后置于反应室内基座上;

6、第二步:将所述反应室抽至真空,随后通入氢气,加热所述反应室后,通入氢氩混合气使所述基座保持气浮状态,进行碳化硅衬底表面刻蚀;

7、第三步:采用线性缓变的方式,在20~100s内改变所述反应室的氢气流量,使得所述反应室的氢气流量为80~250slm,温度为1550~1630℃,待所述反应室的压力稳定后,向所述反应室通入硅源和碳源的混合气体,在刻蚀后的所述碳化硅衬底表面形成缓冲层;

8、第四步:保持第三步的温度、压力与氢气流量不变,采用线性缓变的方式20~100s内改变硅源气体和碳源气体的流量,使得所述反应室内硅源气体的流量为200~500 slm,c/si为0.8~1.3,在所述缓冲层表面形成外延层;

9、第五步:关闭硅源气体和碳源气体输入,使所述基座的气浮流量降低,采用线性缓变的方式20~100s内改变所述反应室的氢气流量至300~500 slm,在氢气气氛中对所述反应室进行降温;然后通入惰性气体置换所述反应室内的氢气,对所述反应室进行抽真空,之后向所述反应室充入惰性气体至大气压,打开所述反应室,取出外延片。

10、进一步地,所述第二步中,将所述反应室抽至真空,随后通入氢气,保持氢气流量为300~500slm,反应室压力为50~300 mbar,加热使所述反应室的温度为1000~1300℃;然后降低升温速度,继续升温至1550~1630℃,通入氢氩混合气使所述基座保持气浮状态,进行碳化硅衬底表面刻蚀。

11、进一步地,所述第二步中,使用射频加热的方式,以固定的升温速度将反应室由室温升温至1300℃,所述固定的升温速度为20-50℃/min;然后将升温速度降低至10-20℃/min,升温至1570~1610℃,通入氢氩混合气使所述基座保持气浮状态,气浮流量为100~2000slm,进行碳化硅衬底表面刻蚀,刻蚀时间为5~20分钟。

12、进一步地,所述第三步中,采用线性缓变的方式,在30~80s内改变所述反应室的氢气流量,使得所述反应室的氢气流量为100~200slm,温度为1570~1610℃。

13、进一步地,所述第三步中,待所述反应室的压力稳定后,向所述反应室通入sihcl3和c2h4的混合气体,其中sihcl3流量为40~200slm,c/si为0.5~1.1,使用氮气或三甲基铝作为掺杂源,形成n型或p型缓冲层,所述缓冲层的掺杂浓度1e17~1e19cm-3,厚度为0.1-1 um。

14、进一步地,所述第四步中,采用线性缓变的方式30~80s内改变硅源气体和碳源气体的流量,使得所述反应室内硅源气体的流量为250~450 slm,c/si为0.9~1.2。

15、进一步地,所述第四步中,在采用线性缓变的方式30~80s内改变硅源气体和碳源气体的流量时,还通入氮气或三甲基铝作为掺杂源,在所述缓冲层表面形成n型或p型外延层。

16、进一步地,所述第五步中,关闭硅源气体、掺杂源和碳源气体输入,使所述基座的气浮流量降低至30-60slm,采用线性缓变的方式30~80s内改变所述反应室的氢气流量至350~450 slm,在氢气气氛中将所述反应室的温度降温至室温。

17、进一步地,所述第五步中,对所述反应室进行抽真空,是将所述反应室的真空抽至0mbar,并维持3-10分钟。

18、本发明还保护所述降低碳化硅外延薄膜表面缺陷的方法制备得到的外延片,所述外延片的表面三角形缺陷分布密度为0.05-0.20cm-2, 和/或所述外延片的表面颗粒缺陷分布密度为0.08-1.15cm-2。

19、有益效果:

20、本发明中,所述降低碳化硅外延薄膜表面缺陷的方法中,在外延结束阶段即第五步中,通过采用线性缓变的方式20~100s内改变所述反应室的氢气流量至300~500 slm,在氢气气氛中对所述反应室进行降温,可以显著降低碳化硅外延薄膜的颗粒缺陷。

21、进一步的,在升温及刻蚀阶段,即第二步中,通过通入氢气,保持氢气流量为300~500slm,反应室压力为50~300 mbar,可以显著降低碳化硅外延薄膜的三角形缺陷。

22、总之,本发明通过控制碳化硅外延生长的工艺,显著改善了磁体材料的质量,可以获得高性能的外延片,从而更好地运用到半导体设备中,具有极好的市场运用前景。

- 还没有人留言评论。精彩留言会获得点赞!