具有掺杂区的MPS二极管及其制造方法与流程

本公开的方面一般涉及mps二极管和用于制造这样的mps二极管的方法。

背景技术:

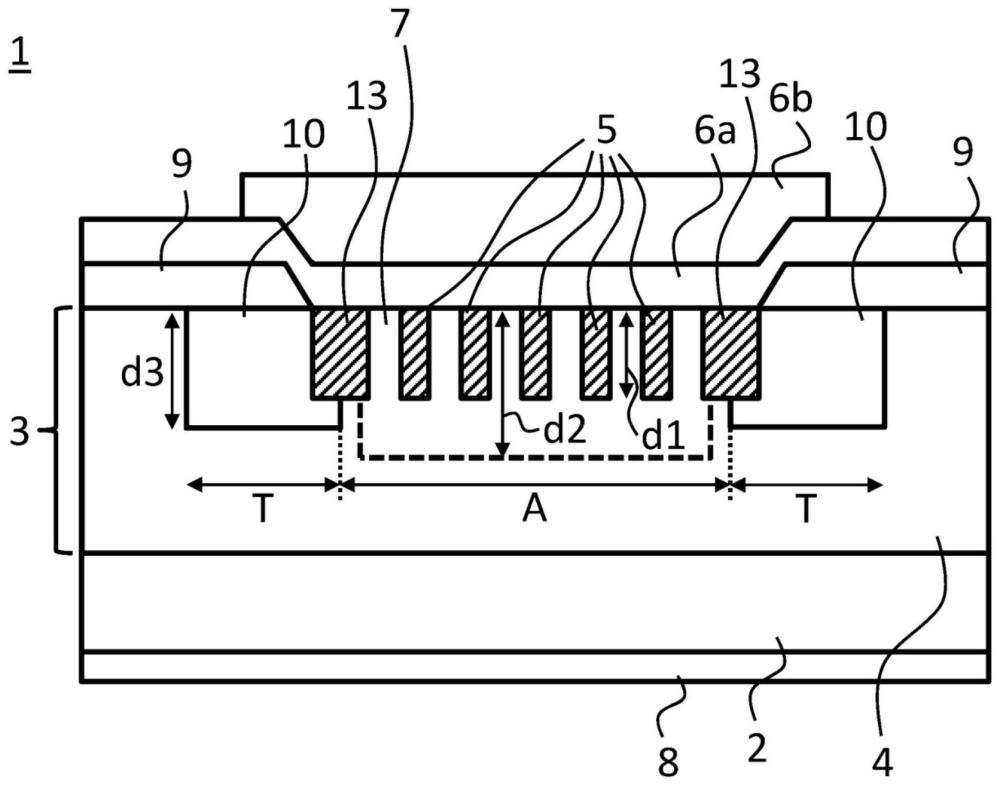

1、图1示出了本领域已知的混合式pin肖特基(mps)二极管100的截面图。mps二极管100包括衬底101和布置在所述衬底101上的外延层102,它们一起形成半导体主体。外延层102包括漂移区103和多个阱104。漂移区103具有第一导电类型,即漂移区103具有n型掺杂和p型掺杂中的一种。阱104具有不同于第一导电类型的第二导电类型,即,与漂移区103相反的导电类型。

2、mps二极管100还包括布置在半导体主体上的金属层组件。在该示例中,金属层组件包括与漂移区103和阱104接触的第一金属层105a。第一金属层105a形成与漂移区103的多个肖特基接触,以及与阱104的多个欧姆接触。金属层组件可以包括第二金属层105b,其布置在第一金属层105a上并且可以形成mps二极管100的第一端子,该第一端子提供到mps二极管100的外部电气接入。此外,接触件106被布置在衬底101上,并且可以形成mps二极管100的第二端子,该第二端子提供到mps二极管100的外部电气接入。

3、阱104和漂移区103包括在半导体主体的有源区中。终端区108可以被设置为与有源区相邻,且可以容纳高电场以防止沿有源区的边缘或周边发生过早击穿。金属层组件可以例如通过绝缘层107(诸如氧化层)与终端区电绝缘。如本领域技术人员所理解的,可以布置图1中未示出的其它层,例如钝化层。

4、阱104与漂移区103形成相应的pn结。根据施加到第一端子和第二端子的正向电压,mps二极管100可以在几种模式下操作。在较低电压下,mps二极管100可在第一模式下操作,所述pn结的耗尽区在相邻阱之间延伸,从而防止或基本上限制肖特基电流从第一金属层105a流向衬底101。在较高电压下,mps二极管100可在第二模式下操作,其中所述pn结的耗尽区变得更小,从而使得肖特基电流能够从第一金属层105a流向衬底101。

5、当施加到mps二极管100的电压使mps二极管100中的电场超过临界水平时,在反向偏置条件下,在mps二极管100中可能发生击穿。由于在这种情况下相对较高的电场,可能发生退化效应,例如由导致温度升高的功率耗散产生。这种退化可能具有短期效应(如装置的直接失效)和长期效应(如寿命缩短)。因此,需要一种mps二极管,其中可防止或实质上减轻由于击穿所致的退化效应。

6、在jp6632910b2、us2018/047855a1、us2021/242307a1、ep3945607a1和us2017/256657a1中公开了本领域已知的mps二极管的其他示例。

技术实现思路

1、本公开的各方面涉及mps二极管,其中不发生或几乎不发生上述(一个或多个)缺点。

2、下面阐述了本文公开的某些实施例的方面的概述。应当理解,这些方面仅被呈现以向读者提供这些特定实施例的简要概述,并且这些方面不旨在限制本公开的范围。实际上,本公开可以涵盖可能未阐述的各种方面和/或方面的组合。

3、根据本公开的一个方面,提供了一种mps二极管。mps二极管包括半导体主体,其包括有源区和与所述有源区相邻的终端区。所述有源区包括:第一导电类型的漂移区;以及不同于所述第一导电类型的第二导电类型的多个阱,所述多个阱相互间隔开,每个阱与所述漂移区形成相应pn结。mps二极管还包括金属层组件,其布置在所述半导体主体的表面上并且包括至少一个金属层,所述金属层组件与所述漂移区一起形成多个肖特基接触并且与所述多个阱形成多个相应欧姆接触。漂移区包括掺杂区,所述掺杂区围绕所述多个阱中的每一个并且具有比所述漂移区的其余部分更高的掺杂剂浓度,并且其中所述掺杂区与所述终端区间隔开。

4、申请人已经发现,在典型的mps二极管中,在终端区中可能发生击穿。然而,终端区是装置的相对小的部分,并且在击穿的情况下,相对大的电流可以流过所述小的部分。

5、在如上所述的根据本公开的mps二极管中,可以通过以下方式来减轻该效应:引入掺杂区,使得由于击穿时的临时操作而导致的过多功率耗散可以在更大的区域上耗散,特别是有源区的相当大的部分或者甚至整个有源区,而不是仅在终端区域上耗散。换句话说,可以防止或限制终端区中的过早击穿。这可以导致由温度增加产生的不太严重的退化效应,并且因此可以导致mps二极管的更高的耐用性和更长的寿命。

6、更具体地,在操作期间,例如由于场拥挤,终端区可能经受相对高的电场。通过将掺杂区与终端区间隔开,防止或限制了有源区中的电场向终端区的扩展。这允许为了更受控的在有源区上扩展的击穿而增加有源区中的电场,而对终端区的行为没有影响或具有有限的影响。

7、多个阱可以从表面延伸到半导体主体中达第一深度,并且掺杂区可以从表面延伸到半导体主体中达第二深度。第二深度可以比第一深度大至少20%,优选地大至少50%。掺杂区相对于多个阱的相对深度还确保了对应于漂移区和多个阱之间的结的耗尽区大部分被限制或集中在掺杂区内,以便进一步防止或限制在有源区外部发生击穿。

8、终端区可以包括第二导电类型的终端区域,其在半导体主体中从表面延伸到第三深度。第二深度可以大于等于第三深度。通过使第一深度大于等于第三深度,可以限制有源区和终端区之间的相交处的电位线的过度收缩,这种收缩可能导致在有源区外部发生击穿的可能性更高。

9、多个阱的掺杂剂浓度可以是终端区域的掺杂剂浓度的至少10倍,优选地至少20倍。通过使多个阱的掺杂剂浓度比终端区域更高,可以进一步增加有源区中的电场相对于终端区中的电场。

10、在垂直于所述表面的方向上,所述掺杂区的掺杂剂浓度可以从所述表面增加。换句话说,掺杂区可以具有从半导体主体的表面朝向掺杂区延伸到的第一深度增加的竖直掺杂剂分布。通过形成具有竖直掺杂剂分布的掺杂区,可以最小化反向偏置的漏电流。

11、在另一实施例中,掺杂区可以包括基本上均匀掺杂的上部区域和在所述上部区域下方的基本上均匀掺杂的下部区域。下部区域可以从多个阱的深度的70%至90%延伸至第一深度。例如,下部区域的掺杂剂浓度可以是上部区域的掺杂剂浓度的至少两倍,或者至少三倍。申请人已经发现,这种配置非常适合于减轻反向偏置的漏电流,以及将相对较高的电场集中在多个阱的底部,这也能够有效地增加在有源区中而不是有源区外部发生击穿的可能性。

12、掺杂区还可以包括一个或多个基本上均匀掺杂的中间区域,该中间区域布置在上部区域和下部区域之间并且具有在上部区域和下部区域的掺杂剂浓度之间的掺杂剂浓度。

13、掺杂区可以与终端区间隔开,并且可以在有源区的至多98%、优选地至多95%、更优选地至少80%中横向延伸。以此方式,有源区的大部分可以有助于传导由于击穿事件中的击穿而产生的电流。

14、掺杂区可以包括中心区域和与内部区域横向相邻的外部区域,其中外部区域具有比内部区域低的掺杂剂浓度,外部区域优选地具有从掺杂区的中心向外的方向上的倾斜的掺杂剂分布。换句话说,掺杂区可具有相对于掺杂区的中心至少在有源区的边缘附近的横向掺杂剂分布。通过使掺杂剂浓度从掺杂区朝终端区到漂移区的其余部分的过渡平滑,可以减少有源区和终端区之间的交叉处的电位线的过度收缩,从而增加有源区中发生击穿的可能性。

15、多个阱中的每对相邻布置的阱中的阱之间的间距以及所述掺杂区的掺杂剂浓度被选择为,使得在击穿时,所述金属层组件和所述漂移区之间的界面处的电场强度低于所述多个阱和所述漂移区之间的pn结处的电场强度的70%,并且优选地低于50%。以此方式,防止或基本上限制了肖特基结处的击穿(即掺杂区和金属层组件之间的界面处的击穿),并且相反可以将击穿基本上集中在阱和漂移区之间的界面处。因此,可以提高mps二极管的鲁棒性和寿命。在示例中,漂移区可具有约1e16 cm-3的掺杂剂浓度,掺杂区可具有在3e16 cm-3至6e16 cm-3之间的掺杂剂浓度,且多个阱可具有约1e18 cm-3的掺杂剂浓度及在2.5μm至3.5μm之间的相对间距。

16、半导体主体可以包括衬底和布置在衬底上的外延层。有源区和终端区可以布置在外延层中。

17、金属层组件可以形成mps二极管的第一端子,并且mps二极管还可以包括布置在衬底上的接触件,所述接触件形成mps二极管的第二端子。

18、掺杂区的掺杂剂浓度可以是漂移区的其余部分的掺杂剂浓度的至少两倍,优选至少三倍。在本公开的上下文内,漂移区的其余部分可以对应于在掺杂区和衬底之间延伸的漂移区的部分。

19、所述多个阱可以形成为平行的条带或同心形状,例如椭圆形或多边形。

20、多个阱中的每个还可以包括位于半导体主体的表面的子区域,该子区域具有比阱的其余部分更高的掺杂剂浓度,以实现与金属层组件和/或所述子区域的欧姆接触。

21、根据本公开的另一方面,提供了一种用于制造mps二极管的方法。该方法包括提供半导体主体,所述半导体主体包括有源区和与所述有源区相邻的终端区,其中所述有源区包括第一导电类型的漂移区;在所述漂移区中形成掺杂区,所述掺杂区具有比所述漂移区的其余部分更高的掺杂剂浓度,其中所述掺杂区与所述终端区间隔开;在所述掺杂区中形成不同于所述第一导电类型的第二导电类型的多个阱,所述多个阱相互间隔开,每个阱与所述漂移区形成相应pn结;以及在所述表面上布置金属层组件,所述金属层组件包括至少一个金属层,其中所述金属层组件与所述漂移区一起形成多个肖特基接触,并且与所述多个阱形成多个相应欧姆接触。

- 还没有人留言评论。精彩留言会获得点赞!