分离栅沟槽MOSFET器件及制备方法与流程

本发明涉及半导体,尤其涉及一种分离栅沟槽mosfet器件及制备方法。

背景技术:

1、现代功率mos通过引入电荷补偿结构,可同时实现较低的通态电阻和较高的阻断电压,其中分离栅沟槽mosfet(split gate trench mosfet,sgt mosfet)就是利用电荷补偿原理,将与源极等电位的分离多晶硅栅极引入普通沟槽mosfet多晶硅栅底部,利用体内场板辅助mosfet的漂移区耗尽,可以在保证耐压等级的情况下通过设置低阻漂移区,显著降低低功率mos器件的rds(on)。目前,分离栅沟槽mosfet已经不止被用作功率开关,很多场景下也被用于多种线性应用,如线性稳压器、线性放大器、电子负载、热插拨电路等。

2、但是,大多数的分离栅沟槽mosfet器件由于高vds电压下分离栅结构对于沟道电压的屏蔽作用,会造成跨导稳定性较差的问题,导致在线性应用中会使输出信号失真。

技术实现思路

1、本发明提供一种分离栅沟槽mosfet器件及制备方法,用以解决现有技术中分离栅沟槽mosfet器件在高vds电压下分离栅结构对于沟道电压的屏蔽作用,导致跨导稳定性较差的问题。

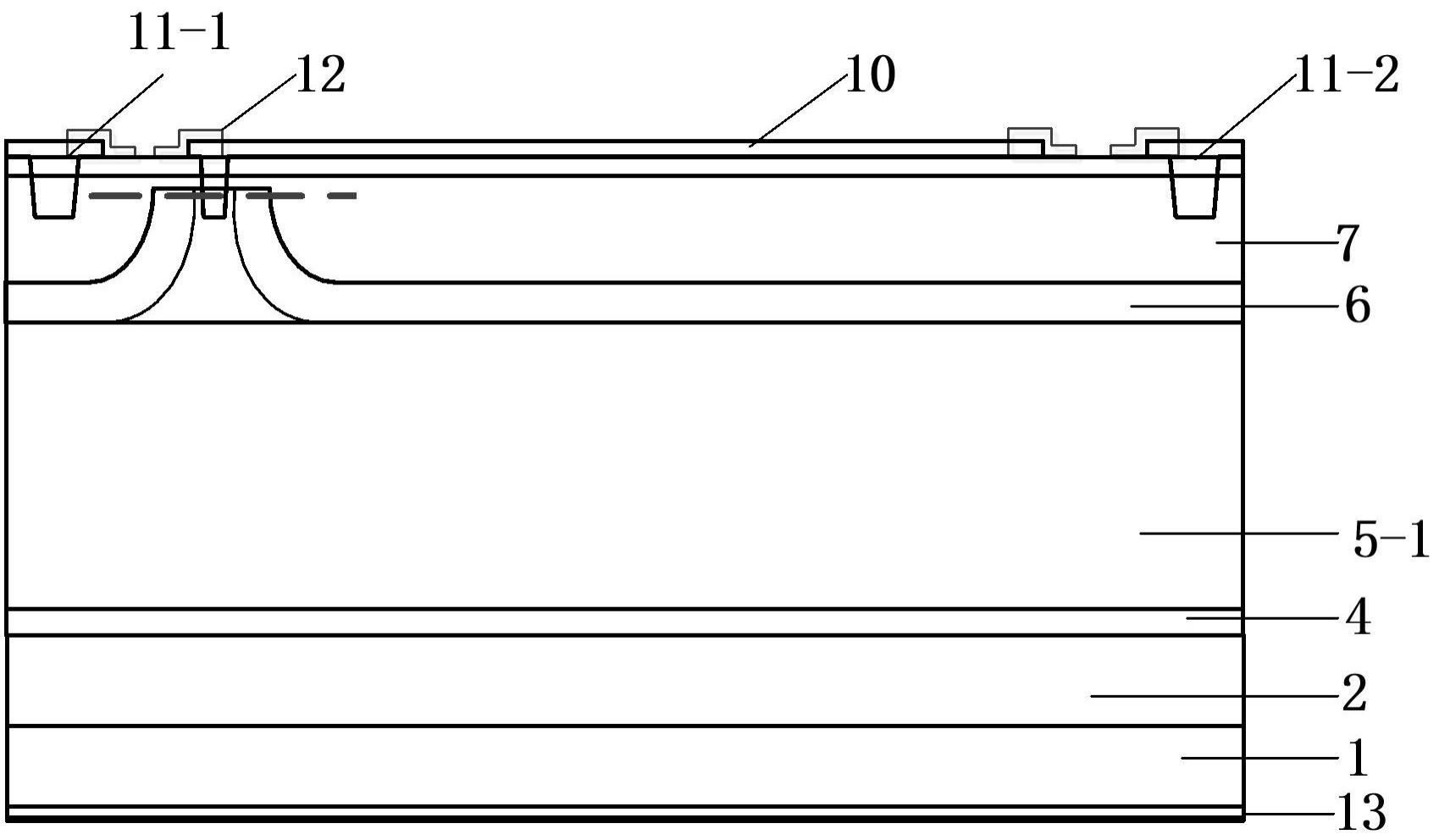

2、本发明提供一种分离栅沟槽mosfet器件,包括:n+型硅衬底、n-型漂移区、原胞沟槽、源极多晶硅接触沟槽、第一栅电极、第二栅电极、源电极和漏电极;

3、所述n-型漂移区设置于所述n+型硅衬底上,所述原胞沟槽和所述源极多晶硅接触沟槽设置于所述n-型漂移区上,所述第一栅电极、所述第二栅电极和所述源电极设置于所述原胞沟槽表面的金属层上,所述漏电极设置于所述n+型硅衬底远离所述n-型漂移区的表面的金属层上;

4、所述原胞沟槽内设置有第一源极多晶硅结构,所述第一源极多晶硅结构四周设置有栅极多晶硅结构,所述源极多晶硅接触沟槽内设置有第二源极多晶硅结构;

5、所述第一栅电极和所述第二栅电极通所述栅极多晶硅结构串联,所述第二栅电极还通过所述第二源极多晶硅结构与所述源电极串联。

6、根据本发明提供的一种分离栅沟槽mosfet器件,所述原胞沟槽与所述源极多晶硅接触沟槽以数量比例(15~30):1呈周期性设置。

7、根据本发明提供的一种分离栅沟槽mosfet器件,所述原胞沟槽内与所述第一源极多晶硅结构之间、所述源极多晶硅接触沟槽与所述第二源极多晶硅结构之间均设置有底部氧化层。

8、根据本发明提供的一种分离栅沟槽mosfet器件,所述第一源极多晶硅结构通过对淀积于所述原胞沟槽内的多晶硅进行光刻工艺、回刻工艺形成的;

9、所述第二源极多晶硅结构通过对淀积于所述源极多晶硅接触沟槽的多晶硅进行光刻工艺形成的。

10、根据本发明提供的一种分离栅沟槽mosfet器件,所述第一源极多晶硅结构上均设置氧化层;

11、所述栅氧化层结构是通过干氧氧化工艺在所述所述氧化层上方的原胞沟槽两侧侧壁热生长而成的。

12、根据本发明提供的一种分离栅沟槽mosfet器件,所述栅极多晶硅结构的表面设置有屏蔽氧化层;

13、p基区是形成所述屏蔽氧化层的晶圆上进行硼离子全局注入生成的。

14、根据本发明提供的一种分离栅沟槽mosfet器件,所述p基区表面设置有n+型注入层;

15、所述n+型注入层是在所述p基区表面进行砷离子注入形成的。

16、根据本发明提供的一种分离栅沟槽mosfet器件,所述n+型注入层表面还设置有介质氧化层;

17、所述介质氧化层通过光刻工艺形成金属电极接触孔,所述栅极多晶硅结构和所述第二源极多晶硅结构上的所述第二栅电极通过所述金属电极接触孔相连。

18、本发明还提供一种分离栅沟槽mosfet器件的制备方法,包括:

19、选取n+型硅衬底作为晶圆,在所述n+型硅衬底上淀积n-型外延层作为n-型漂移区,并在所述n-型漂移区进行光刻工艺、刻蚀工艺,形成沟槽,所述沟槽包括原胞沟槽和源极多晶硅接触沟槽;所述原胞沟槽与所述源极多晶硅接触沟槽数量以(15~30):1的比例周期性设置;

20、在所述原胞沟槽和所述源极多晶硅接触沟槽内通过热氧氧化工艺热生长氧化层形成底部氧化层;

21、在所述底部氧化层上、所述原胞沟槽内和所述源极多晶硅接触沟槽内淀积多晶硅,去除高于所述底部氧化层、所述原胞沟槽和所述源极多晶硅接触沟槽表面多余的多晶硅;对所述原胞沟槽内源极多晶硅回刻区的多晶硅采用光刻工艺、刻蚀工艺进行回刻,对所述原胞沟槽内的多晶硅回刻区之外的区域不进行多晶硅回刻,形成第一源极多晶硅结构;对所述源极多晶硅接触沟槽内淀积的多晶硅整体不进行回刻,形成第二源极多晶硅结构;

22、采用光刻工艺、刻蚀工艺去除所述原胞沟槽侧壁上的所述底部氧化层至所述第一源极多晶硅结构回刻深度0.3~0.6μm处;通过氧化工艺第一源极多晶硅结构再采用干氧氧化工艺在在所述氧化层上方的原胞沟槽两侧侧壁形成栅氧化层结构;

23、对所述原胞沟槽和所述源极多晶硅接触沟槽进行多晶硅淀积,并去除高于沟槽表面的多晶硅,在所述第一源极多晶硅结构回刻区形成栅极多晶硅结构,所述栅极多晶硅结构围绕于所述第一源极多晶硅结构四周;在所述栅极多晶硅结构的表面进行干氧氧化工艺形成厚0.04~0.07mm厚的氧化层;

24、对所述氧化层进行减薄至0.03~0.04μm厚度,并在形成所述氧化层的晶圆上进行硼离子全局注入形成p基区;

25、对所述p基区表面进行砷离子注入,形成n+型离子注入区,然后进行离子注入退火,形成n+型注入层;

26、在形成所述n+型注入层的晶圆上淀积厚度1.0~1.5μm的介质氧化层;再在所述介质氧化层上通过光刻工艺形成金属电极接触孔、在原胞沟槽内的源极多晶硅未回刻区形成第一类源极多晶硅接触孔、在原胞沟槽内的源极多晶硅回刻区形成第一栅极接触孔、第一类第二栅极接触孔、在原胞沟槽内的源极多晶硅回刻区形成第一栅极接触孔和第一类第二栅极接触孔、在源极多晶硅接触沟槽内的第二源极多晶硅结构上形成第二类第二栅极接触孔和第二类源极多晶硅接触孔;

27、通过所述金属电极接触孔进行硅回刻,回刻深度0.4~0.6μm,形成n+源区,进行源电极接触区bf2注入工艺,注入后进行退火;而后在形成所述金属电极接触孔的晶圆上表面淀积厚度为4~6μm的alsicu金属层,通过光刻工艺、刻蚀工艺形成源电极、第一栅电极和第二栅电极;

28、其中,所述第一栅电极通过所述第一栅极接触孔、所述第一类第二栅极接触孔和所述原胞沟槽内的所述源极多晶硅结构进行串联; 所述第二栅电极通过所述第二类源极多晶硅接触孔、所述第二类第二栅极接触孔和所述第二类源极多晶硅进行串联,所述第一类源极多晶硅接触孔与所述源电极相连;

29、在源电极、所述第一栅电极和所述第二栅电极上淀积钝化层,并通过光刻工艺、刻蚀工艺形成钝化结构;在所述n+型硅衬底远离所述n-型漂移区的表面蒸镀ti/ni/ag金属层,形成漏电极。

30、根据本发明提供的一种分离栅沟槽mosfet器件的制备方法,所述原胞沟槽和所述源极多晶硅接触沟槽的深度为4~7μm、宽度为1.0~1.8μm;

31、所述底部氧化层的厚度为0.4~0.9μm;

32、所述栅氧化层结构的厚度0.04~0.09μm;

33、形成所述p基区时,所述硼离子注入能量为80~150kev,注入剂量为1.3e13~2.1e13;

34、形成所述n+型注入层时,所述退火的温度为950~1000℃,退火时间为90~120min;

35、所述bf2注入工艺时,所述注入能量为60~80kev,注入剂量为3e14~5e14,退火温度为900~1000℃,退火时间为20~30min。

36、本发明提供的分离栅沟槽mosfet器件及制备方法,分离栅沟槽mosfet器件包括:n+型硅衬底、n-型漂移区、原胞沟槽、源极多晶硅接触沟槽、第一栅电极、第二栅电极、源电极和漏电极;n-型漂移区设置于n+型硅衬底上,原胞沟槽和源极多晶硅接触沟槽设置于n-型漂移区上,第一栅电极、第二栅电极和源电极设置于原胞沟槽表面的金属层上,漏电极设置于n+型硅衬底远离n-型漂移区的表面的金属层上;原胞沟槽内设置有第一源极多晶硅结构,第一源极多晶硅结构四周设置有栅极多晶硅结构,源极多晶硅接触沟槽内设置有第二源极多晶硅结构;第一栅电极和第二栅电极通栅极多晶硅结构串联,第二栅电极还通过第二源极多晶硅结构与源电极串联,由于设置第一栅电极和第二栅电极,实现串联分压,在原胞沟槽方向引入渐变的vgs电压,在利用分离栅沟槽mosfet器件使高漏源电压vds在器件沟道两端产生的实际电势差vds'趋近饱和的同时,拥有较低栅源电势的第二栅电极侧的mosfet原胞在相对较低的vds电压区间满足沟道两端的实际电势差vds'>vgs-vth而产生沟道夹断,进入mosfet器件输入输出特性曲线的饱和工作区,使器件具有良好跨导稳定性和线性输出特性。

- 还没有人留言评论。精彩留言会获得点赞!